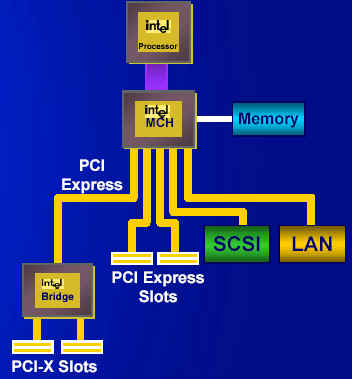

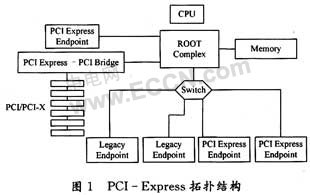

PCIE是一種典型的串行總線,本文是針對PCI-E接口的布線規則,這些規則是很多芯片廠商的設計指導,也是很多老工程師耳熟能詳的金科玉律。

1. 阻抗要求

PCI-Express的接口走線阻抗在4層或6層板時必須保持100ohm差分。

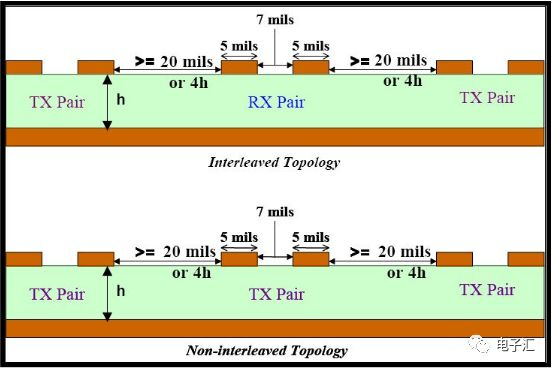

2.線寬和線距 通過阻抗計算軟件,結合PCB疊層情況,計算出合理的走線線寬和線距。比如,微帶線情況下,差分線的寬度為5mil,差分對中2條走線的間距是7mil。(帶狀線情況下,差分線的寬度為5mil,差分對中2條走線的間距是5mil。)

差分對之間的距離和差分線與其他非PCI Express信號的距離保持20mil或介質厚度的四倍,選擇其中更大者。如果非PCI Express信號電壓明顯高于或非PCI EXPRESS信號邊緣比PCI Express信號邊緣快的話,兩者的空間應增加到30mil,以避免耦合。如圖1所示:

3.長度和長度匹配

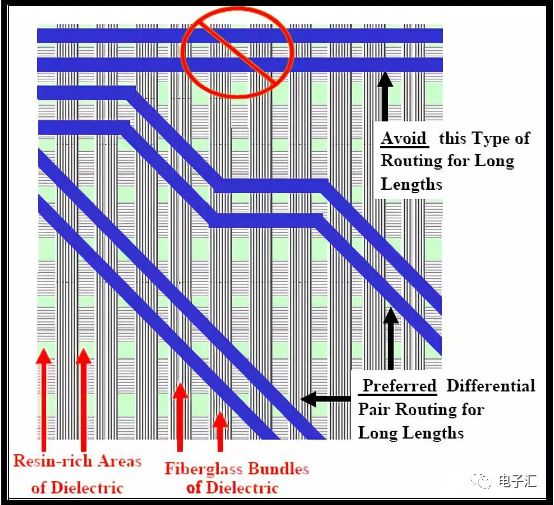

為了分散玻璃纖維束編織和介質層非增強表面樹脂層的有效厚度區域的影響,長距離走線必須與XY軸成一個斜的角度(長走線應在板上走斜線),如圖2所示:

圖2

PCB的每英寸走線可能會引進1ps~5ps的抖動預算和0.25dB~0.35dB的損耗。介質為FR4的PCB,一般來說: a.差分對從芯片到芯片的走線最大不能超過6英寸; b.差分對中兩條走線的長度的差距應小于等于5mil。

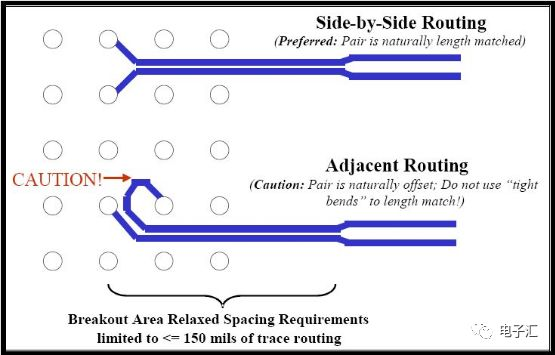

在遇到布局緊張等特殊情況時時走線可以由5-7變為更小的線寬和線距,但是當發生這種情況時,變換的差分對走線長度不能超過150mil。如圖3所示:

圖3

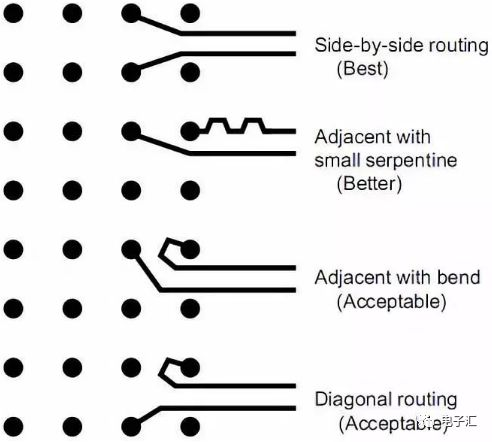

還有長度匹配應盡可能接近信號引腳而沒有引入任何小角度彎曲。具體走線可參考圖4:

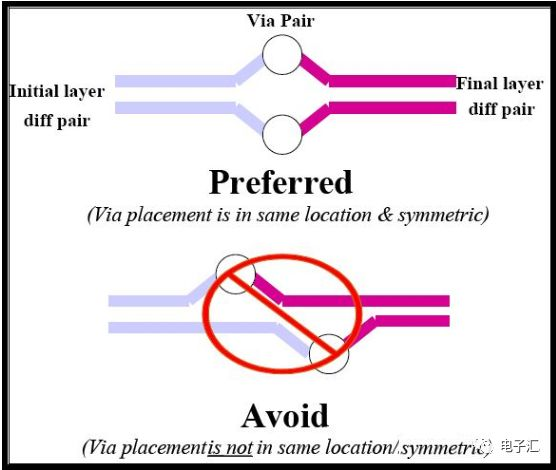

圖4 4.測試點、過孔和焊盤 信號過孔影響整體的損耗和抖動預算,限制最大的走線長度。 在TX差分對中最多可以使用4個過孔,而在RX差分對中最多只可以使用2個過孔。過孔應該有一個25mil或更小的焊盤,并且其完成內徑應該為14mil或更小。兩個過孔必須放在一互相對稱的位置上。如圖5所示:

圖5

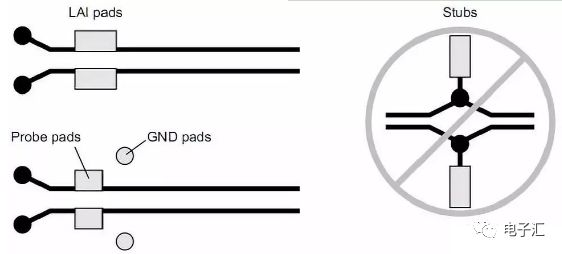

測試點(可以是過孔,焊盤或是元件)及探針腳應置于對稱的位置,不應當在差分對引入stub,如圖6:

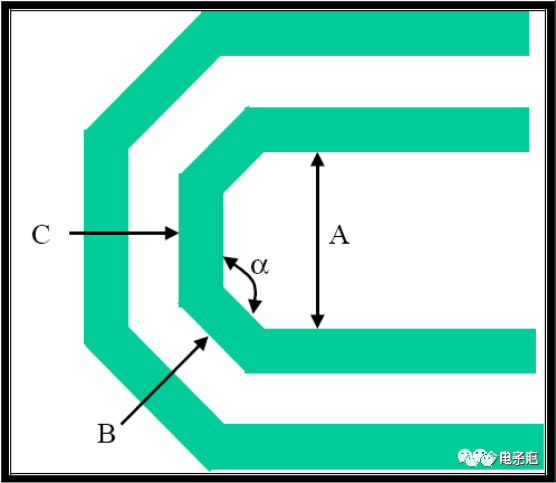

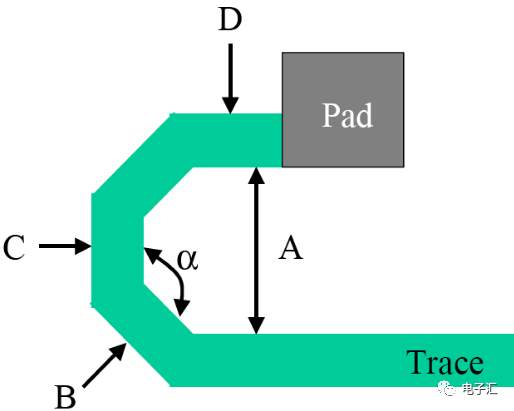

圖6 5.彎曲 應盡量不使用彎曲,因為其會引入共模噪聲。差分對使用彎曲應該遵循以下規則:(以圖7為例) 1.所有彎曲的角度(α)應該≥135°; 2.保持走線間距(A)≥20mil; 3.片斷,比如B和C,其側翼有一個彎曲,其長度應該≥1.5倍的走線寬度。

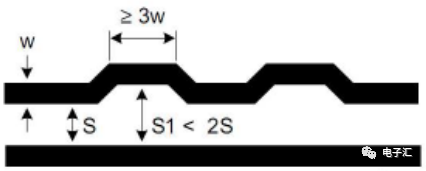

圖7 盡量使左彎曲的數量和右彎曲的數量相等。 當一段蛇形線用來和另一段走線來進行長度匹配時,每段長彎折的長度必須至少15mil(3倍于5mil的線寬)。蛇行線彎折部分和差分線的另一條線的最大距離必須小于正常差分線線距的2倍。如圖8所示:

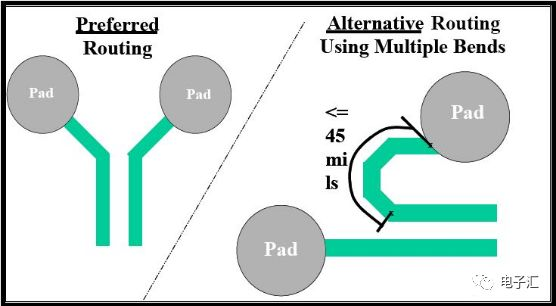

圖8 當使用多重彎曲布線到一個管腳或是一個BGA的焊盤的非匹配的部分應該≤45mil,如圖9所示:

圖9 連接到焊盤的彎曲線應該遵循以下規則:(以圖10為例) 1.所有彎曲的角度(α)應該≥135°; 2.保持走線間距(A)≥3倍的走線寬度; 3.B和C段其長度應該≥1.5倍的走線寬度; 4.D段應該盡量短。

圖10 6.AC電容 PCIExpress需要在發送端和接收端之間交流耦合。差分對兩個信號的交流耦合電容必須有相同的電容值,相同的封裝尺寸,并且位置對稱。 AC電容必須放在最靠近信號發送端的位置。電容值必須介于75nF到200nF之間(最好是100nF)。推薦使用0402封裝,但是0603封裝也是可以接受的。兩電容應該對稱放置,如圖11所示:

圖11

此外差分參考時鐘應該和高速串行數據線一樣使用相同幾何結構的差分線。

免責聲明:本文轉載于網絡,轉載此文目的在于傳播相關技術知識,版權歸原作者所有,如涉及侵權,請聯系小編刪除。

審核編輯 黃宇

-

電容

+關注

關注

100文章

6240瀏覽量

153523 -

接口

+關注

關注

33文章

8968瀏覽量

153347 -

PCI

+關注

關注

5文章

678瀏覽量

131588 -

總線

+關注

關注

10文章

2956瀏覽量

89453 -

布線

+關注

關注

9文章

796瀏覽量

84961

發布評論請先 登錄

如何進行PCI-Express的一致性測試和分析

基于PCI-Express的高速數據交換設計及應用

如何對PCI-Express總線的SSC(擴頻時鐘)進行驗證

pci express總線概念

PCI Express插槽,什么是PCI Express插槽

基于Virtex5的PCI-Express總線接口設計

PCB布線規則之PCI卡篇

PCI-Express插槽

從PCI、PCI-X到PCI-Express之間的連接

PCI-Express總線接口的布線規則

PCI-Express總線接口的布線規則

評論