(一)低功耗isolation cell的目的

低功耗架構(gòu)設(shè)計需要前后端拉通規(guī)劃,前端設(shè)計有PMU功耗管理單元,比如A模塊電壓常開,B模塊電壓可關(guān)斷,那么請思考,當B模塊關(guān)斷電壓后,B模塊輸出到A模塊的信號是怎樣的驅(qū)動力?會造成什么結(jié)果?

后果1:

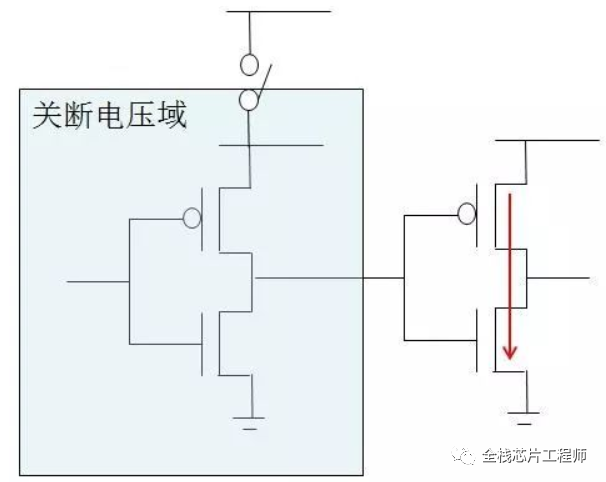

假如電源的工作電源為1.2V,當B模塊關(guān)斷電壓后,B模塊輸出到A模塊的信號(X態(tài))可能為0~1.2V中任意電壓,如果X處在中間電平0.6V,若這個信號送給電壓常開域中的一個反相器,就會導致這個反相器的PMOS和NMOS都導通,就會存在一個短路電流從電源流經(jīng)PMOS、NMOS再到地,造成功耗浪費。

后果2:

假如電源的工作電源為0~1.2V,那么X態(tài)信號可能隨著溫度、電壓等環(huán)境因素改變而震蕩,導致常開電壓模塊的邏輯功能出現(xiàn)不可預知的錯誤,甚至引起系統(tǒng)宕機,造成芯片功能的不可靠,芯片上到汽車、飛機上去后,不堪設(shè)想。

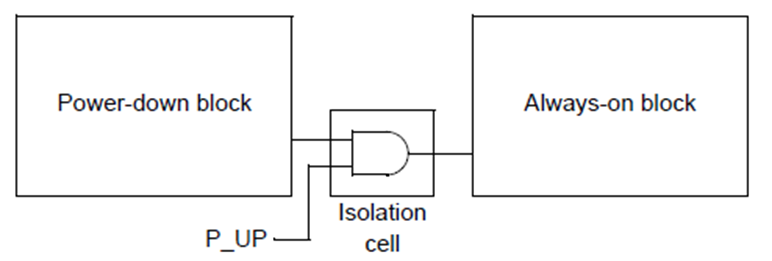

因此,當A模塊電壓常開,B模塊電壓可關(guān)斷,在B模塊關(guān)斷電壓后,B模塊輸出到A模塊的信號需要用isolation cell進行電壓鉗位(clamp 0或者clamp 1信號),這樣就避免了X態(tài)的傳播。

也就是說Isolation cell連接的兩端分別是power gated domian和always_on_domain,Isolation_cell的作用就是將power gated domian輸出到always on domain的信號隔離,以防止power gated domian電源關(guān)閉后輸入到always on domian的信號出現(xiàn)不確定狀態(tài)(如X態(tài)等)。

(二)低功耗isolation cell的類型

isolation cell一般有sink side、source side兩種類型。

什么是sink side?

即isolation cell放置于常開電壓域PD_ON,只需要一組電源,推薦使用這種類型,較為簡潔。

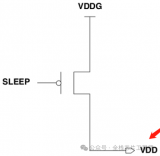

什么是source side?

即isolation cell放置在power gated domain(PD_SHUT)里面,但是需要接常開電源(VDDG)供電,保證power gated domain(PD_SHUT)的電壓關(guān)閉后,isolation仍能輸出clamp值。這種情況下,isolation cell一般得有兩組電源,分別是primary power(VDD)和 backup power(VDDG),當VDD關(guān)斷后,VDDG就供電,否則isolation誰來供電輸出clamp值呢。

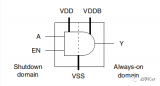

isolation cell的結(jié)構(gòu)(下圖為source side isolation類型):

(三)低功耗isolation cell的結(jié)構(gòu)

上面介紹了模塊電壓關(guān)閉之后,其輸出需要isolation cell進行鉗位的原因,以及isolation cell的兩種類型及兩組電源的需求,通常isolation cell和Level Shifter一起連用,AND和OR門都可以組成一個isolation cell;

AND類型:輸出iso成0;

OR類型:輸出iso成1;

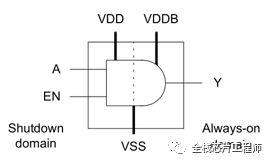

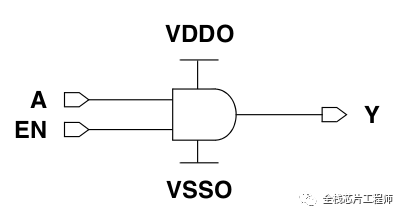

首先看AND類型,EN有效時(置0),輸出Y(isolation)=0,請思考下圖的類型是source類型還是sink類型?

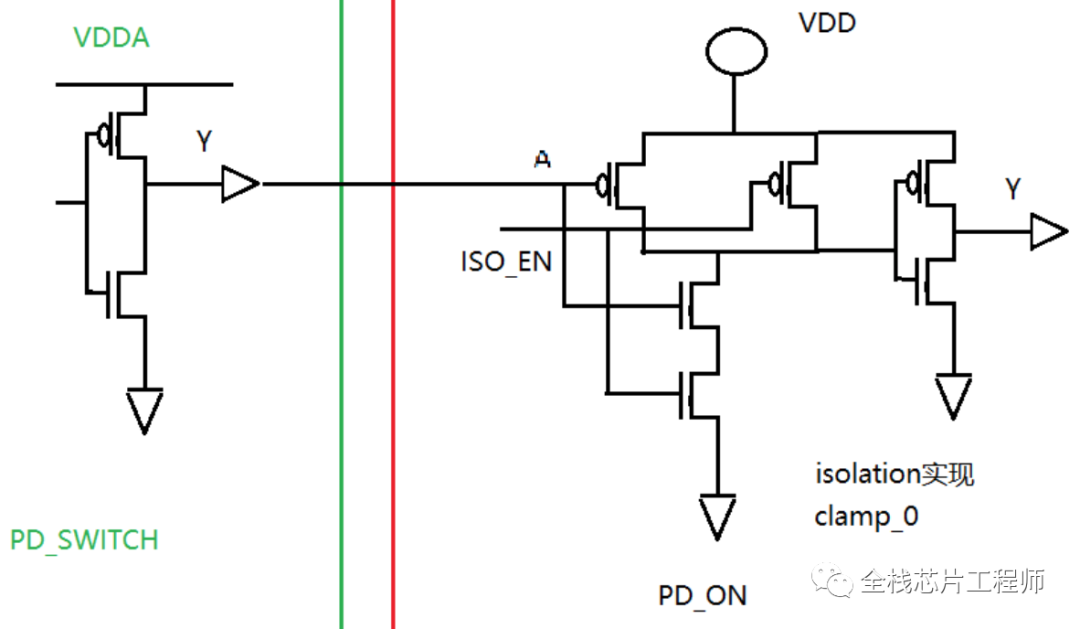

展開與門電路結(jié)構(gòu)如下圖右邊部分,請思考,下圖Y輸出是否和上圖一致?ISO_EN是高有效還是低有效?想通了就很有趣!

isolation實現(xiàn)clampe_0功能

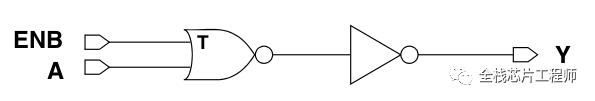

然后我們看OR或門類型:ENB有效,Y就被鉗位為1。

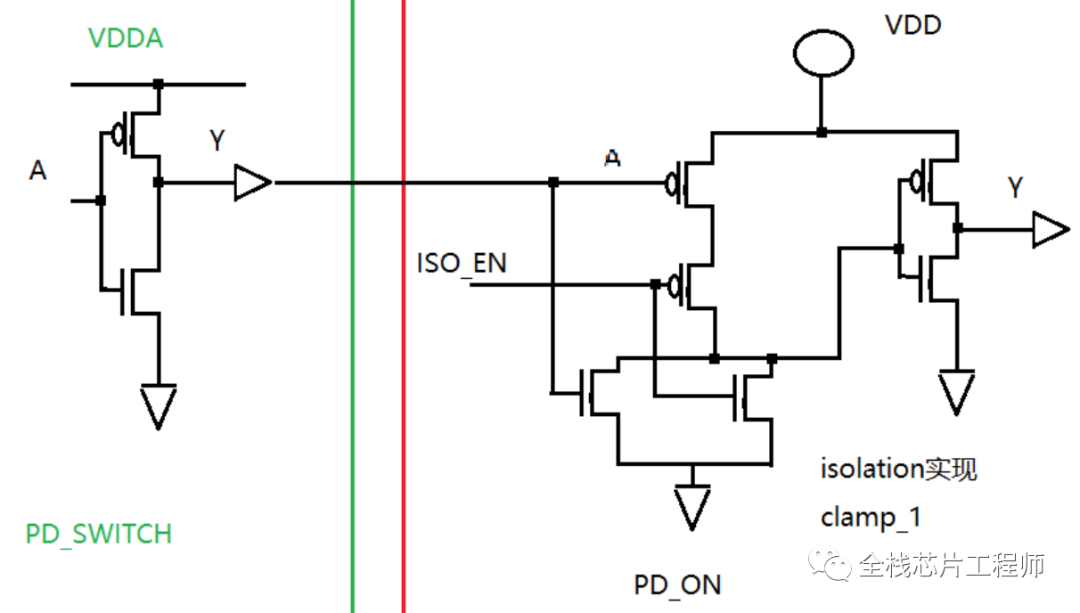

或門展開電路如下圖右邊部分,請思考下圖ISO_EN是1有效嗎?管子是如何工作才能鉗位輸出?鉗位輸出是1嗎?是不是很有趣!

綜上,通常Isolation cell和Level Shifter一起連用,AND和OR門都可以組成一個isolation cell。Isolation可以放在input端,output端或者第三方Voltage Area中,但是考慮到power-on rail的走線,isolation cell自身的功耗,一般還是放在input端比較好,因為放在input端不需要always-on的power。

(四)低功耗isolation cell的UPF語法

set_isolation ISO0_PD_SHUT 指定isolation cell的添加rule,相當于前綴名稱

-domain PD_SHUT 指定添加isolation cell的voltage area

-applies_to input 指定isolation cell在voltage area的input還是output

-diff_supply_only true 指定cell port上是否允許有其他supply

-loacation parent 指定isolation的放置位置,parent代表放在driver pin的父module

-isolation_signal PMU/iso_en 指定isolation cell的isolation 控制信號

-calmp_value 1 指定isolation cell的輸出值

-

模塊

+關(guān)注

關(guān)注

7文章

2785瀏覽量

49979 -

NMOS

+關(guān)注

關(guān)注

3文章

358瀏覽量

35495 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1075瀏覽量

55536 -

低功耗

+關(guān)注

關(guān)注

11文章

2766瀏覽量

104700 -

PMOS

+關(guān)注

關(guān)注

4文章

267瀏覽量

30424

原文標題:芯片設(shè)計—低功耗isolation cell

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

什么是Isolation Cell?低功耗設(shè)計基礎(chǔ)—Isolation Cell

低功耗藍牙怎么低功耗?如何界定

分享幾種實現(xiàn)數(shù)字IC的低功耗設(shè)計方法

低功耗電路設(shè)計_低功耗設(shè)計方法

什么是低功耗,對FPGA低功耗設(shè)計的介紹

低功耗設(shè)計之multi-bit cell技術(shù)簡介

基于UPF的低功耗數(shù)字后端設(shè)計實訓課

是否需要補插scan chain的isolation cell?怎么插呢?

isolation cell的低功耗設(shè)計

低功耗isolation cell設(shè)計

低功耗isolation cell設(shè)計

評論