也是一個平常的工作日,和同事就PipelinedADC中的MDAC電路拉了幾句家常。他說:“你看,這個1.5bit結(jié)構(gòu)的MDAC電路,一堆的開關(guān)加電容,看起來似乎很復(fù)雜,但如果推導(dǎo)出它的傳遞函數(shù),會發(fā)現(xiàn)只是一條簡單的數(shù)學(xué)公式,其傳輸曲線也很簡潔明了。所以,很多電路本質(zhì)上還是數(shù)學(xué),只不過是用電路的形式實(shí)現(xiàn)而已。”

我覺得,這算是一個老工程人的中肯的見解,很是讓人信服(心里默默點(diǎn)個贊)。

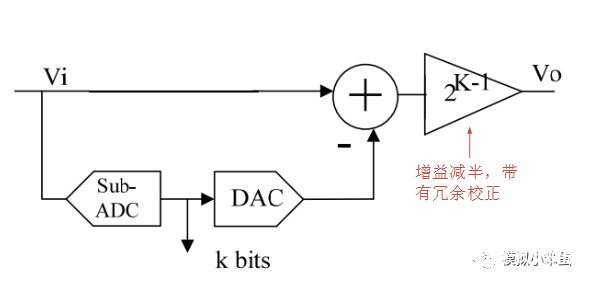

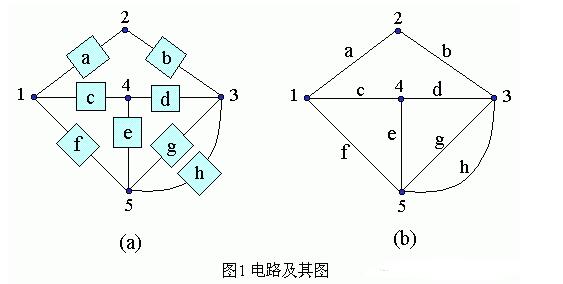

圖1:MDAC原理框圖

MDAC 電路一般由開關(guān)電容電路來實(shí)現(xiàn),和 S/H 類似,它在兩相非交疊時鐘 控制下工作,工作階段分為兩個階段:采樣階段和放大階段。

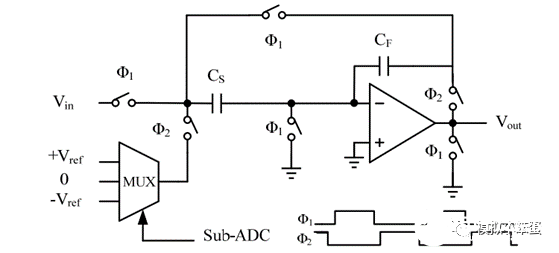

圖2給出了 1.5 位結(jié)構(gòu) MDAC的電路結(jié)構(gòu)示意圖,其中電容 CS和 CF容值相同。時鐘 Φ1 和Φ2為兩相非交疊時鐘。

圖2:1.5bitMDAC電路結(jié)構(gòu)

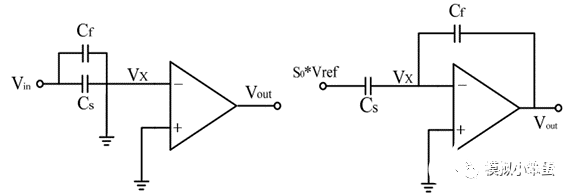

圖3:1.5位MDAC工作原理(a)采樣階段(b)放大階段

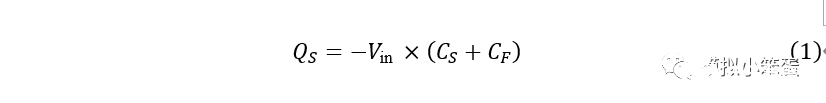

MDAC 電路工作過程如下:假定時鐘為高的時候有效。在采樣相,連接關(guān)系如圖3(a)。兩個電容對輸入信號 Vin進(jìn)行采樣,運(yùn)放此時處于復(fù)位狀態(tài)。采樣結(jié)束時刻,Vx節(jié)點(diǎn)存儲的總電荷量為:

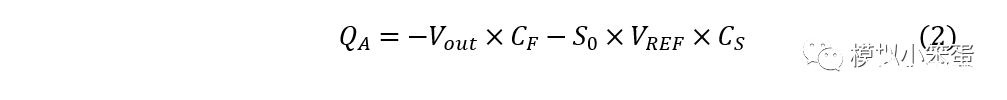

在放大階段, 電路處于閉環(huán)狀態(tài), 連接關(guān)系如圖3b所示。CS電容的一端接S0*Vref , 它的值可以為Vref、0、-Vref , 由本級sub-ADC輸出決定, 在放大相, 節(jié)點(diǎn)上的總電荷為:

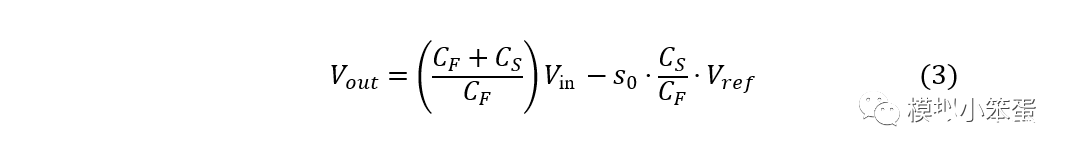

根據(jù)電荷守恒,可得出MDAC的最終輸出為:

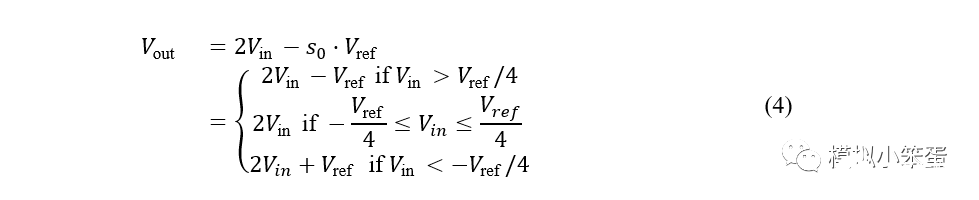

因?yàn)镃S=CF,S0根據(jù)Sub-ADC結(jié)果不同可為+1、0、-1。因此上式可以寫成如下分段形式:

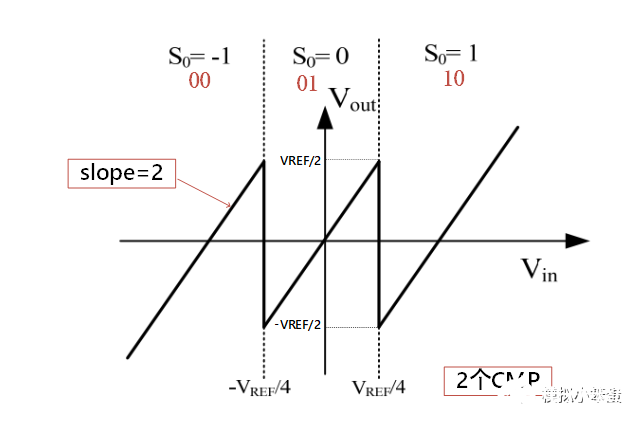

MDAC的輸出也稱為余量電壓。式(3)所示的余量會被傳輸?shù)较乱患壛魉€級進(jìn)行繼續(xù)量化,直到最后一級的Flash級,完成所有的量化,輸出N位數(shù)字碼。從式(4)可以得到1.5位流水線級的傳輸曲線,如圖4所示。其中±VREF/4是sub-ADC中比較器陣列的參考電平,S0為-1、0、1分別對應(yīng)著數(shù)字輸出00、01、10。有效位數(shù)為1位,另外一位為冗余位,和后級流水線級的數(shù)字輸出碼進(jìn)行錯位相加,消除比較器的失調(diào)帶來的誤差。因此這樣的結(jié)構(gòu),被稱為1.5位流水線級結(jié)構(gòu)。

圖4:1.5位MDAC傳輸曲線

審核編輯:黃飛

-

電容

+關(guān)注

關(guān)注

100文章

6236瀏覽量

153451 -

比較器

+關(guān)注

關(guān)注

14文章

1842瀏覽量

108657 -

開關(guān)電容

+關(guān)注

關(guān)注

0文章

103瀏覽量

18706 -

輸入信號

+關(guān)注

關(guān)注

0文章

472瀏覽量

12855

發(fā)布評論請先 登錄

位結(jié)構(gòu)解析

電阻器梯形結(jié)構(gòu):R-2R DAC與MDAC架構(gòu)

請問什么是電機(jī)結(jié)構(gòu)分析的大局觀?

硬件的引腳和電路結(jié)構(gòu)分析一下要如何啟動

NCP1562的有源鉗位正激拓補(bǔ)結(jié)構(gòu)及電路

監(jiān)護(hù)儀原理、電路結(jié)構(gòu)及其應(yīng)用分析

NAND_Flash結(jié)構(gòu)與驅(qū)動分析

什么是電路拓?fù)?b class='flag-5'>結(jié)構(gòu)_多種pfc電路的拓?fù)?b class='flag-5'>結(jié)構(gòu)介紹

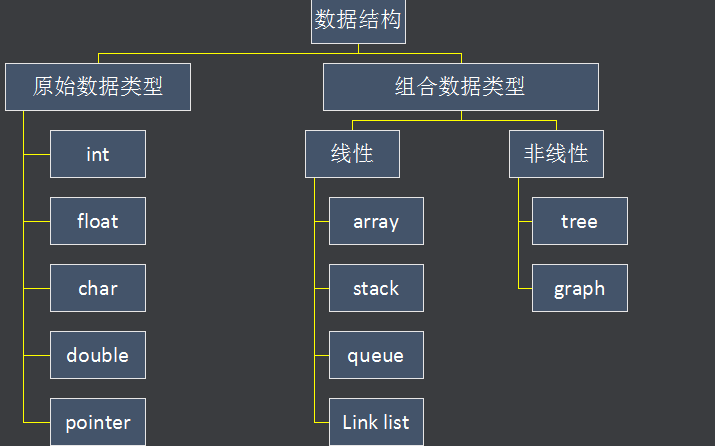

什么是數(shù)據(jù)結(jié)構(gòu)?為什么要學(xué)習(xí)數(shù)據(jù)結(jié)構(gòu)?數(shù)據(jù)結(jié)構(gòu)的應(yīng)用實(shí)例分析

AD7837/AD7847:LC<sup>2</sup>完整MOS,雙12位MDAC產(chǎn)品手冊

1.5位結(jié)構(gòu)MDAC的電路結(jié)構(gòu)分析

1.5位結(jié)構(gòu)MDAC的電路結(jié)構(gòu)分析

評論