電遷移(EM)是一種分子位移,是由于導(dǎo)電電子和離子在一段時(shí)間內(nèi)的動(dòng)量轉(zhuǎn)移而引起的。當(dāng)電流密度較高時(shí)會(huì)發(fā)生這種現(xiàn)象,這會(huì)導(dǎo)致金屬離子向電子流方向漂移。EM通常發(fā)生在多年之后。

由于電遷移效應(yīng),金屬線可能會(huì)斷裂并短路。EM會(huì)增加導(dǎo)線電阻,這會(huì)導(dǎo)致電壓下降,從而導(dǎo)致設(shè)備降速。由于短路或開路,它還可能導(dǎo)致電路永久性故障。

隨著可靠性要求越來越高,EMIR問題也是必須的檢查項(xiàng)。目前流程一般都是根據(jù)代工廠提供的 EM 規(guī)則執(zhí)行 EM Checks,根據(jù)檢查的結(jié)果進(jìn)行EM優(yōu)化。下面經(jīng)驗(yàn)分享幾種優(yōu)化EM的有效措施,這些方法都經(jīng)過驗(yàn)證非常有效。主要用圖示加說明來介紹。

1.增加金屬寬度以降低電流密度

這是最常用的解決EM的方法,增加到滿足電流的寬度或者通過疊層金屬實(shí)現(xiàn)電流能力。

2.合理分配大電流金屬走線

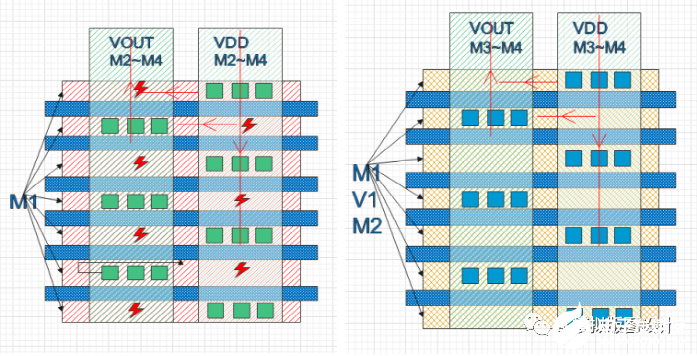

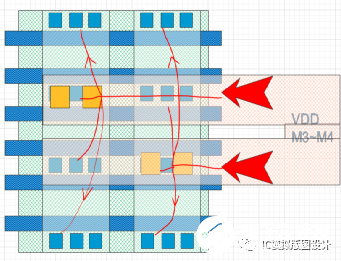

下圖是一個(gè)power mos 的EM問題示意圖,先看下左圖存在EM問題的連接方式,mos管源漏端使用橫向M1通過VIA1 連到縱向M2~M4的疊層通路上。產(chǎn)生EM問題的地方為圖中紅色閃電圖標(biāo)位置M1層。

拿源端的VDD來分析,電流從上方M2~M4 到mos上對(duì)于VIA1區(qū)域電流從上到下豎直直接到源上沒有EM瓶頸,而對(duì)于左邊的源區(qū)域來說,電流需要通過橫向M1 向左流動(dòng),這樣M1就成了電流的瓶頸,所以會(huì)在這個(gè)區(qū)域產(chǎn)生M1上的EM問題。

如何改善?合理分配金屬走線,如右圖所示,原來縱向的M2~M4 足夠強(qiáng)壯,而到了橫向M1上時(shí)又非常弱。

我們可以把縱向M2~M4 減少成M3~M4,用M2 改成與原來M1疊層,這樣就能解決橫向電流能力。M1的EM問也就解決了。

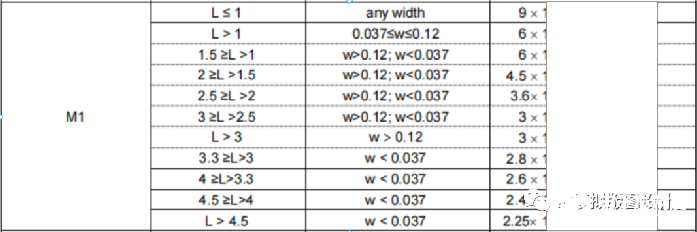

3.充分利用短金屬的強(qiáng)電流密度能力

有些場(chǎng)景可能會(huì)出現(xiàn)下圖一樣的連接方式類似魚骨型的連接,出現(xiàn)的EM問題是在較短的金屬上,這個(gè)時(shí)候我們可以借用短金屬的強(qiáng)電流能力來修改EM,如下圖當(dāng)長度小于1u任意寬度的時(shí)候電流能力是長度大于3u寬度大于0.12的3倍能力。可以通過design rule中這些信息來修改EM。如下圖示意,當(dāng)適當(dāng)減短連線時(shí),對(duì)電流能力的提升是成倍的。

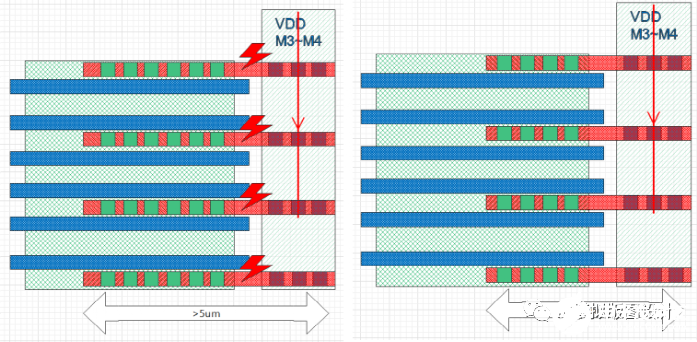

4.分流,避免電流匯集瓶頸

版圖中連線對(duì)EM不合理導(dǎo)致在通路上存在電流瓶頸,如下左圖電流從右側(cè)到mos 管雖然版圖上做了兩條縱向M2均勻連到源端的橫向M1上,但是電流就近流入右側(cè)M2然后到下層M1,電流集中到了右側(cè)的M2到M1的通路上,反而左邊這根縱向M2上沒有EM問題。

如何改善?采用分流,盡可能讓電流分配均勻。我們采用類似星型連接讓電流分通路到mos上。這樣電流就不會(huì)匯集到同一位置上。這個(gè)方式在電源模塊功率器件到Bump連接上比較常見。

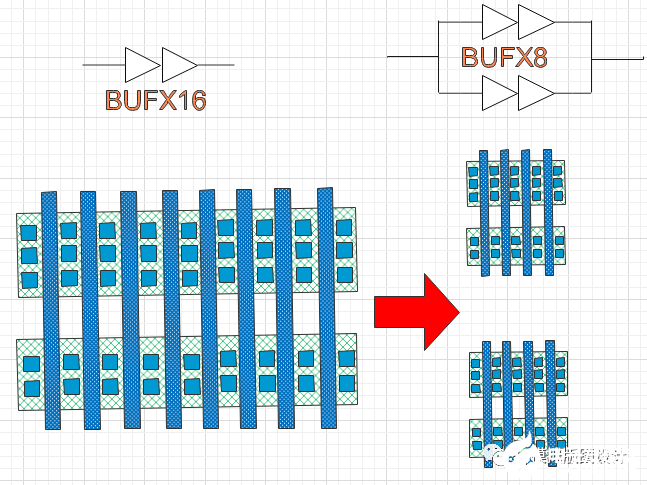

5.大推力BUFFER 使用帶來的EM問題

對(duì)于一些使用大size的BUF,尤其是使用STD cell中的BUF,常常會(huì)遇到EM 問題,大BUF電流更大,而電源地連接強(qiáng)度非常弱。導(dǎo)致BUF的電源地區(qū)域EM嚴(yán)重。

如何優(yōu)化?找designer 討論將大size BUF改成多個(gè)小size的并聯(lián)如下示意圖。版圖上盡可能分散開,讓電源連到到每個(gè)buf上都能充分連接上。另外在周圍空的區(qū)域盡可能添加電源地的decap。Decap對(duì)EM是有非常大的幫助的,decap能夠消除電源上高頻噪聲,同時(shí)儲(chǔ)存能量,在buf的抽拉電流時(shí)能及時(shí)補(bǔ)充(個(gè)人理解)。

6.高頻信號(hào)的EM 問題

高頻信號(hào)需要快速抽拉電流,所以 產(chǎn)生EM的問題也是非常明顯。對(duì)這塊的解決辦法首先要增強(qiáng)電源地的走線強(qiáng)度。對(duì)高頻信號(hào)要盡可能換到高層后金屬走線。高頻信號(hào)的BUF也是采用第五條的方式盡可能拆分并聯(lián)均勻分布。

同時(shí)周圍盡可能添加電源地decap。高反轉(zhuǎn)的cell 周圍預(yù)留足夠空間。

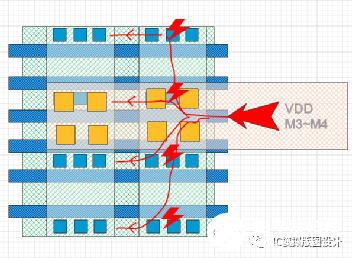

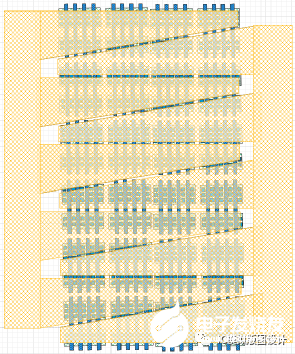

7.大面積功率MOS的接法

對(duì)于大面積功率管,它的連接方式還是比較講究的,很多人應(yīng)該看到過下圖這種寶塔型寬度漸變的連接方式。

這種方式根據(jù)電流走向,走線寬度變化根據(jù)逐步匯總電流強(qiáng)度同步。比較推薦的一種走線方式。

8.仿真場(chǎng)景與環(huán)境確認(rèn)

遇到過這種情況:EM情況異常,最終排查到是testbench設(shè)置仿真時(shí)間不合理,仿真時(shí)間段也是非常重要的。選取正常工作階段的一到兩周期。仿真溫度是否合理,105°下的EM能力是150°兩倍以上。

所以確保電流信息的來源要是正確的合理的。

設(shè)計(jì)過程中及時(shí)EM檢查方式

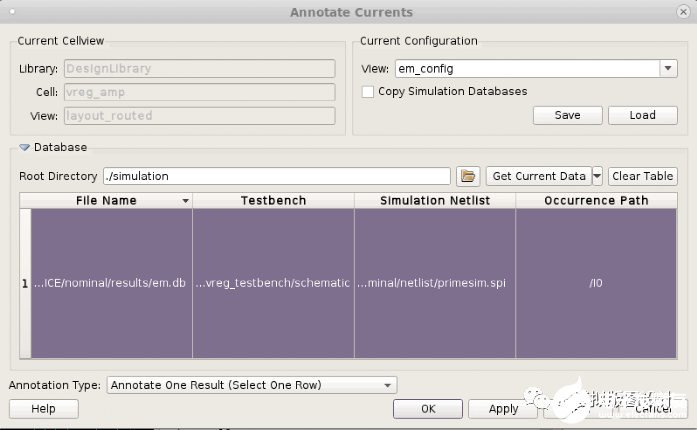

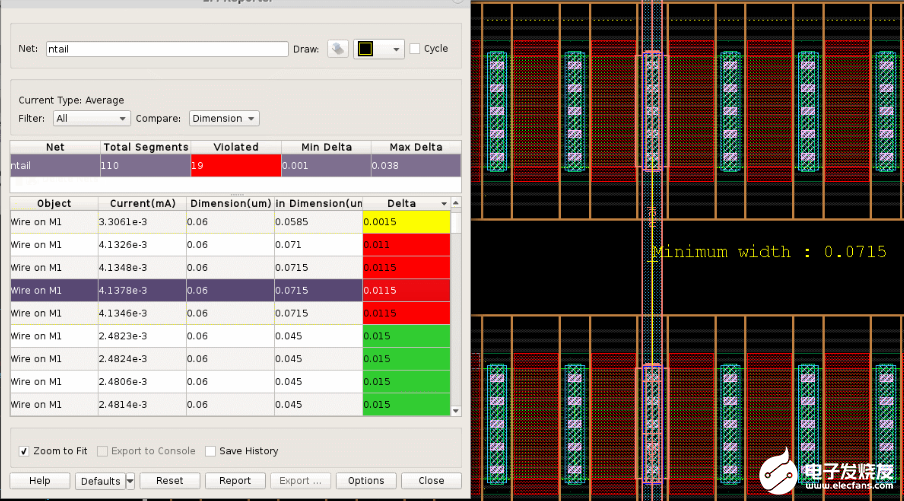

為了避免在sign off 階段EMIR的檢查帶來的設(shè)計(jì)修改風(fēng)險(xiǎn),上面每種方式都需要對(duì)設(shè)計(jì)較大改動(dòng)。我們可以使用 Custom compiler 的Indesign EM功能。Indesign EM可以實(shí)現(xiàn)在設(shè)計(jì)過程中時(shí)時(shí)EM檢查,避免signoff時(shí)EM風(fēng)險(xiǎn)帶來的設(shè)計(jì)迭代。In Design EM的優(yōu)點(diǎn)是無需版圖完成,只需要連接了對(duì)于net,就可對(duì)此net進(jìn)行EM check.

Check的速度是非常快,使用也是非常方便一次性配置,后續(xù)只需要選對(duì)應(yīng)net 進(jìn)行reporting。

首先第一步需要把仿真結(jié)果中保存的電流信息反標(biāo)到對(duì)應(yīng)net節(jié)點(diǎn)上。我們知道不同的仿真corner對(duì)應(yīng)的電流也是不同的,這里我看選的多個(gè)corner的仿真結(jié)果,選擇最差的電流情況進(jìn)行反標(biāo),以避免個(gè)別場(chǎng)景下電流不是最worst的情況。

電流標(biāo)注成功后,隨便選擇一個(gè)mos查看對(duì)應(yīng)terminal信息可以看到對(duì)應(yīng)的電流信息已經(jīng)標(biāo)注成功了同時(shí)Avg Peak Rms對(duì)應(yīng)電流,下圖演示操作效果和debug優(yōu)化的過程。

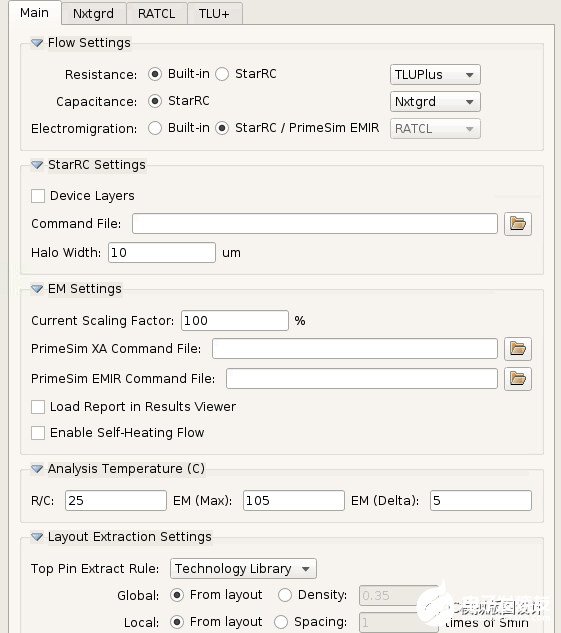

關(guān)于EM的準(zhǔn)確性,從下面setting可以得到EM計(jì)算有兩種方式,使用Built-in是快速的方式。使用StarRC PrimeSimEMIR方式高精度方式。

審核編輯:黃飛

-

電流

+關(guān)注

關(guān)注

40文章

7137瀏覽量

135064 -

MOS管

+關(guān)注

關(guān)注

109文章

2626瀏覽量

70856 -

電源模塊

+關(guān)注

關(guān)注

33文章

1911瀏覽量

94486 -

功率器件

+關(guān)注

關(guān)注

42文章

1934瀏覽量

92800 -

功率管

+關(guān)注

關(guān)注

3文章

86瀏覽量

22432

發(fā)布評(píng)論請(qǐng)先 登錄

汽車電子電氣架構(gòu)設(shè)計(jì)及優(yōu)化措施

ADS內(nèi)部的2.5D EM優(yōu)化不可行

基于熱電偶的抗干擾方法和有效措施

改善電路的EMI特性的有效措施

ESD有哪幾種防護(hù)措施?

對(duì)UPS電源采取有效的監(jiān)控措施

解析幾種有效的開關(guān)電源電磁干擾的抑制措施

幾種有效的開關(guān)電源電磁干擾抑制措施

幾種優(yōu)化EM的有效措施

幾種優(yōu)化EM的有效措施

評(píng)論