前言

時鐘好比MCU的心跳,只有時鐘正常了,MCU的核及外設才能正常工作。從源頭到系統(tǒng)到外設理解每一個時鐘的來源及其具體值才能方便后面理解MCAL的GPT,PWM,ICU等模塊的配置(MCAL模塊中的Tick數(shù)就是基于模塊時鐘的)。本系列文章就來詳細介紹TC3xx芯片的時鐘系統(tǒng)及其具體配置。本文為TC3xx芯片時鐘系統(tǒng)的鎖相環(huán)PLL詳解。

縮略詞

| 簡寫 | 全稱 |

| OSC | OscillatorCircuit |

| PLL | Phase-LockedLoop |

| DCO | DigitallyControlledOscillator |

注:本文章引用了一些第三方工具和文檔,若有侵權,請聯(lián)系作者刪除!

正文

2. 時鐘倍頻PLL

系統(tǒng) PLL 可以將低頻外部時鐘信號轉換為高速內部時鐘,以獲得最佳性能。它允許通過改變不同的分頻器因子來使用多種輸入和輸出頻率。

系統(tǒng) PLL 還具有故障安全邏輯,可檢測到非生成外部時鐘行為,如異常頻率偏差或外部時鐘完全丟失。如果它在外部時鐘上失去鎖定,它可以執(zhí)行緊急操作。

2.1 特點

DCO鎖檢測

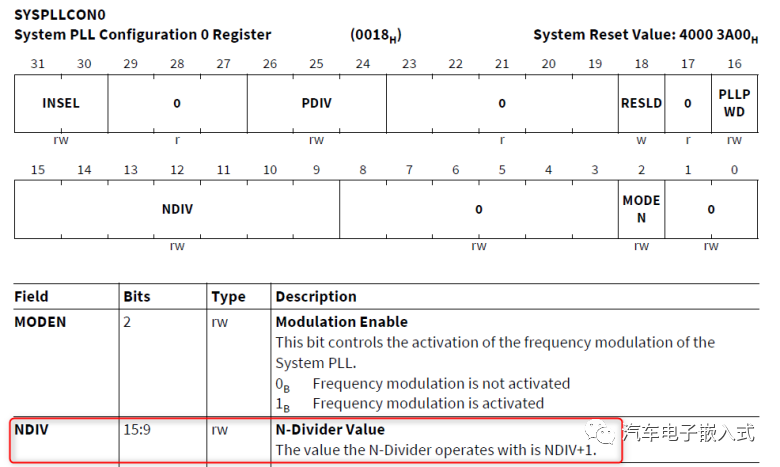

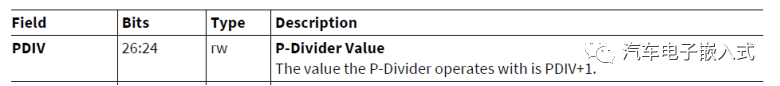

3 位輸入分隔器 P (除以 PDIV+1)

7 位反饋分隔器 N (乘以 NDIV+1)

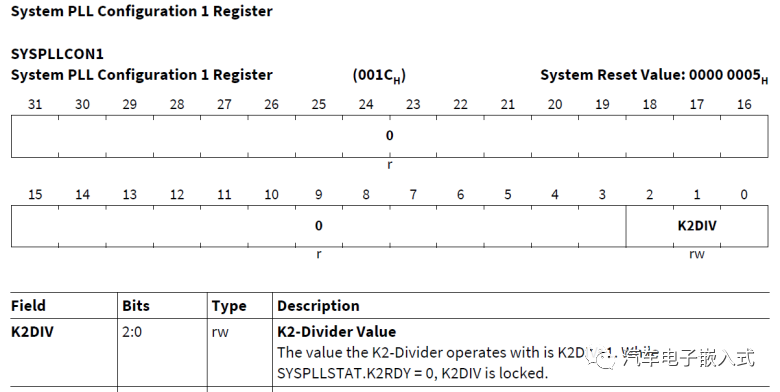

3 位輸出分隔器 K2 (除以 K2DIV+1)

振蕩器監(jiān)視(Oscillator Watchdog)

-檢測輸入頻率是否太低

-檢測輸入頻率是否太高

低頻率抖動調制

2.2 系統(tǒng)時鐘鎖相環(huán)PLL

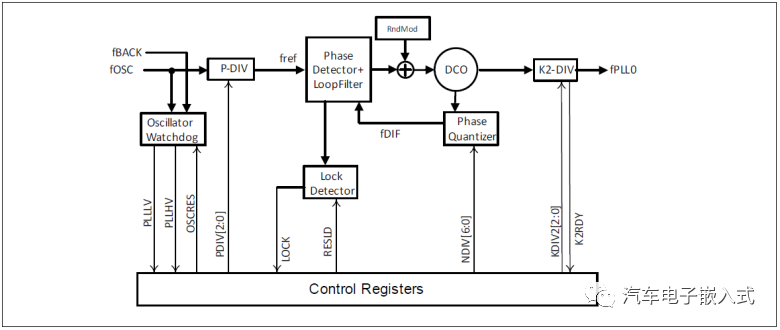

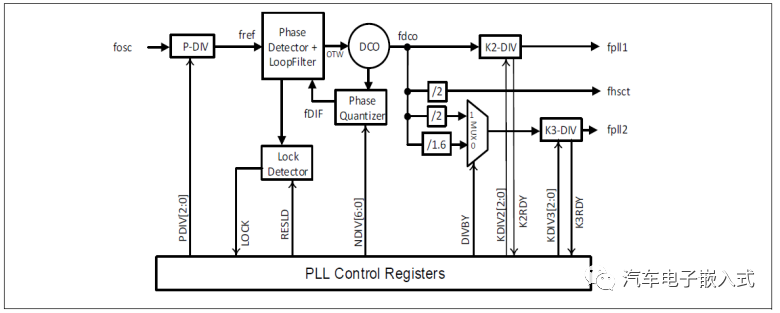

Figure 3 System PLL Block Diagram

輸入頻率 fOSC 除以因子 P ,乘以因子 N ,然后再除以因子 K2。

輸出頻率計算公式如下:

fPLL0 = (N* fOSC) / (P * K2)

fPLL0需要 fOSC的輸入時鐘頻率。 因此,建議通過檢查 OSCCON.PLLV 來檢查和監(jiān)控輸入頻率 fOSC 是否可用。 為了更好地監(jiān)控,還可以通過 OSCCON.PLLHV 監(jiān)控上頻。

系統(tǒng)操作頻率由三個分頻器(divider)的值控制: P , N 和 K2。修改兩個分頻器 P 和 N 對 DCO 頻率有直接影響,可能導致鎖定狀態(tài)丟失。修改 K2 分頻器對鎖定狀態(tài)沒有影響,但仍會更改系統(tǒng) PLL 輸出頻率 fPLL0.

注意:通過更改 K2-Divider 的值來更改系統(tǒng)操作頻率,可以直接連接到設備的功耗。因此,必須謹慎行事。

當必須修改系統(tǒng) PLL 輸出頻率的頻率時,應遵循以下順序:

應禁用為失去鎖定而生成的 SMU 警報。

CCU 使用不同的時鐘源時,可以配置系統(tǒng) PLL 并檢查其位置 DCO 鎖定狀態(tài)。第一個目標頻率的選擇方式應與 CCU 當前使用的目標頻率相匹配,或僅略高一些。這可以避免在以后切換至系統(tǒng) PLL 時發(fā)生系統(tǒng)操作頻率 (因此也避免功耗) 的大變化。應按以下方式選擇 P 和 N 分頻因子(divider):

選擇 P 和 N 時, fDCO位于其允許值的下半部分。 這會導致功耗略有降低,但抖動略有增加。

選擇 P 和 N 時, fDCO位于其允許值的上部區(qū)域。 這會導致功耗略有增加,但抖動略有降低。

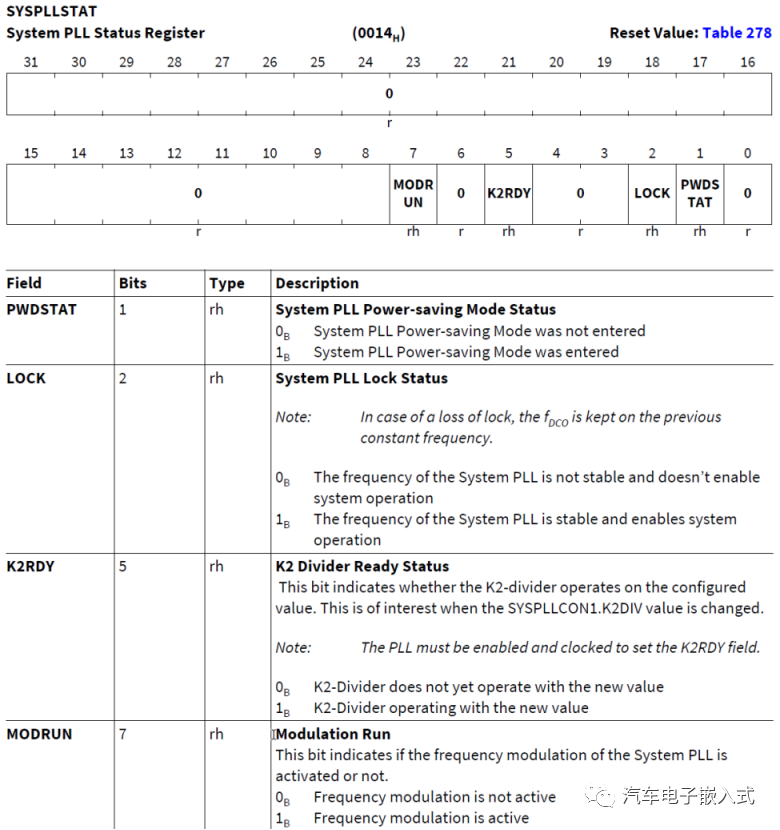

通過更新 P , N 和 K2 分頻因子完成第一次PLL時鐘配置后,應檢查 DCO 鎖定狀態(tài)指示 (SYSPLLSTAT.LOCK = 1)。

系統(tǒng) PLL 鎖定后,可以切換至系統(tǒng) PLL。系統(tǒng) PLL 丟失鎖定事件的 SMU 狀態(tài)標志應被清除,然后再次啟用SMU監(jiān)控。

現(xiàn)在只能通過更改 K2-Divider 來配置目標系統(tǒng) PLL 輸出目標頻率。根據 K2-Divider 的值,選擇輸出時鐘的周期時間。這可能會對使用外部通信接口的操作產生影響。多步更改 k2-Divider ,以避免輸出頻率發(fā)生大變化,從而避免功耗發(fā)生大變化。

注意:

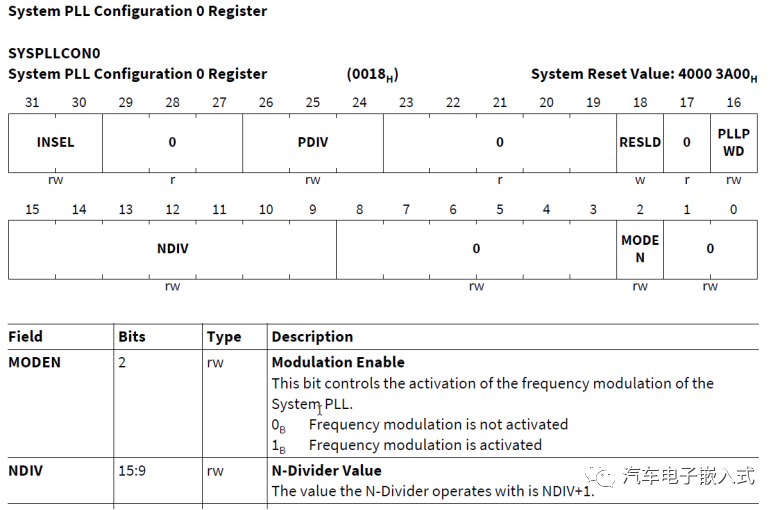

建議配置完P 和 N 分頻器(divider)的新值后重置 DCO 鎖定檢測 (SYSPLLCON0.RESLD = 1),這樣就能得到一個芯片預定義好的DCO鎖的檢測時間(讓DCO鎖有充足時間檢測并鎖定) 。

由于兩個 PLL (System PLL and Peripheral PLL)的緊急從 PLL 切換至備用時鐘同時激活,強烈建議僅在設置了外圍 PLL 并將其鎖定到目標頻率時,才將系統(tǒng)時鐘切換至系統(tǒng) PLL。如果執(zhí)行了順序設置,則可能會發(fā)生外設 PLL 在設置過程中丟失鎖定事件,這也會導致系統(tǒng)時鐘切換至備用時鐘。

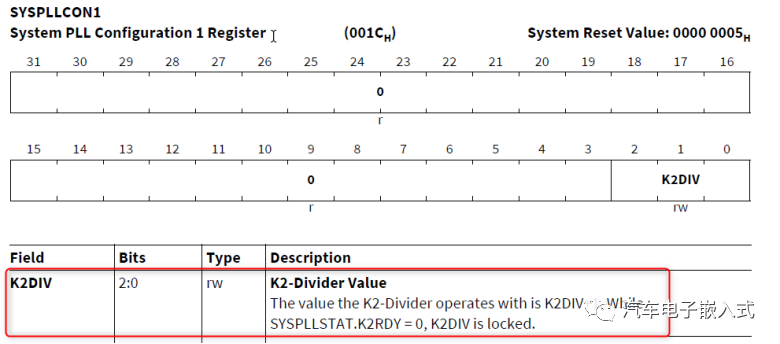

建議在設置 DCO 頻率并鎖定系統(tǒng) PLL 后步進的設置系統(tǒng) PLL K2-Divider (降低功率突變沖擊)。此外,用戶必須在再次更改 SYSPLLCON1.K2DIV 值之前檢查 SYSPLLSTAT.K2RDY =1。SYSPLLCON1.K2DIV 寄存器在上一次寫入仍在進行時被鎖定,如 SYSPLLSTAT.K2RDY =0 所示。

System PLL Lock Detection

系統(tǒng) PLL 具有鎖定檢測(lockdetection)功能,用于監(jiān)控系統(tǒng) PLL 的 DCO 部分,以區(qū)分穩(wěn)定和不穩(wěn)定的 DCO 電路行為。如果兩個輸入fREF 和fDIV的差異太大,鎖定探測器(lock detector)會將 DCO 電路標記為不穩(wěn)定,因此 DCO 的輸出fDCO. 低于某一級別的一個或兩個輸入頻率的變化不會被鎖定標記,因為 DCO 可以處理小的變化且保證系統(tǒng)沒有任何問題。

System PLL Loss-of-Lock Event

由于晶體 / 陶瓷諧振器或外部時鐘線斷裂,系統(tǒng)PLL 可能會解鎖。在這種情況下,會生成 SMU 警報事件。

System PLL Power Down Mode

系統(tǒng) PLL 提供斷電模式。如果根本不需要外圍 PLL ,則可以進入此模式以節(jié)省電源。通過設置位 SYSPLLCON0.PLLPWD 進入斷電模式。當系統(tǒng) PLL 處于斷電模式時,不會生成系統(tǒng)PLL 輸出頻率。

Frequency Modulation

系統(tǒng) PLL 輸出頻率 fPLL0還可以通過低頻調制進行修改,以減少 EMI。隨機序列被添加到 DCO ,從而形成隨機調制的 fDCO。 調制頻率由 fREF定義。

調制通過位 SYSPLLCON0.MODEN啟用。 調制本身會在配置的調制幅度 (MA) 范圍內隨機改變 DCO 頻率。調制振幅通過 SYSPLLCON2.MODCFG[9:0] 選擇。

SYSPLLCON2.MODCFG[9:0] = HEX[(64 * (MA / 100)) * (fOSC / P) *(N/ fMV)]

Example: for MA = 1.25%; fOSC = 20 MHz; P = 2; N = 60; fMV = 3.6 MHz the resulting bit field setting is 0x85.

調制的執(zhí)行方式是,調制所增加的累積抖動保持在JMOD以下 (有關定義的值,請參閱數(shù)據表)。調制本身通過 fREF進行監(jiān)控,因此應使用盡可能最小的值配置分壓器。

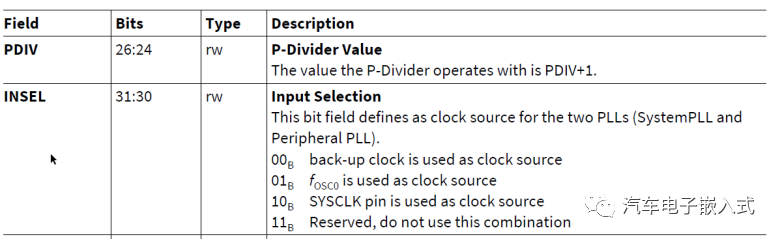

2.3 系統(tǒng)PLL寄存器

系統(tǒng)PLL狀態(tài)寄存器

系統(tǒng)控制寄存器0

系統(tǒng)PLL配置寄存器1

2.4 外設時鐘鎖相環(huán)PLL

外設PLL配置基本和系統(tǒng)PLL類似,這里只給出時鐘倍頻圖及其計算公式。

Figure4 Peripheral PLL Block Diagram

fPLL1 = (N* fOSC) / (P * K2)

fPLL2 = (N* fOSC) / (P * K3 * 1.6) if DIVBY = 0 or fPLL2 = (N* fOSC) / (P * K3 * 2) if DIVBY = 1

fHSCT = fDCO / 2

通過配置外設PLL的配置寄存器就能配置P, K2, K3參數(shù)的具體值。

2.5 PLL實際應用配置

需求1:配置fOSC到100MHz.

公式:fPLL0 = (N* fOSC) / (P * K2)

fOSC== 20MHz

N= SYSPLLCON0.NDIV + 1 = 29(0x1D, 配置SYSPLLCON0.NDIV為29) + 1 = 30

P = SYSPLLCON0.PDIV+ 1 = 0(配置SYSPLLCON0.PDIV為0) + 1 = 1

K2 = SYSPLLCON1.K2DIV + 1 = 5(配置SYSPLLCON1.K2DIV為5) +1 = 6

fPLL0 = (N* fOSC) / (P * K2) = (30 * 20)/(1 * 6) = 100MHz

查看SYSPLLSTAT寄存器的PWDSTAT和K2RD位域來判斷時鐘配置結果。

需求2:配置fPLL1到320MHz.

需求3:配置fPLL2到200MHz.

需求4:配置fHSCT到640MHz.

計算公式:

fPLL1 = (N* fOSC) / (P * K2)

fPLL2 = (N* fOSC) / (P * K3 * 1.6) if DIVBY = 0 or fPLL2 = (N* fOSC) / (P * K3 * 2) if DIVBY = 1

fHSCT = fDCO / 2

同樣,我們配置:

N = 32

P = 1

K2 = 2

K3 = 2

fPLL1 = (N* fOSC) / (P * K2) = (32 * 20) / (1 * 2) = 320 MHz.

fPLL2 = (N* fOSC) / (P * K3 * 1.6) if DIVBY = 0 or fPLL2 = (N* fOSC) / (P * K3 * 2) if DIVBY = 1

= (32 * 20) / (1 * 2 * 1.6) = 200 MHz.

fHSCT = fDCO / 2 = = (N* fOSC) / (P) = 640 MHz.

示例代碼:

#include"IfxScu_reg.h"

#include "IfxSmu_reg.h"

staticuint8Startup_ClockInit_ConfigPLL(void)

{

Ifx_SCU_SYSPLLCON0SysPLLCon0;

Ifx_SCU_PERPLLCON0ScuPerPllCon0;

Ifx_SCU_PERPLLCON1ScuPerPllCon1;

uint32TimeoutCount;

uint8Error=0;

LockEndinit_Core0();

/*ConfigurethesystemPLL*/

SysPLLCon0.U =MODULE_SCU.SYSPLLCON0.U;

SysPLLCon0.B.PDIV=0x00;

SysPLLCon0.B.NDIV=0x1D;

SysPLLCon0.B.INSEL=1;//fOSCisusedasclocksource

MODULE_SCU.SYSPLLCON0.U = SysPLLCon0.U;

/*ConfiguretheperipheralPLL*/

ScuPerPllCon0.U=MODULE_SCU.PERPLLCON0.U;

ScuPerPllCon0.B.DIVBY=0x00;

ScuPerPllCon0.B.PDIV=0x00;

ScuPerPllCon0.B.NDIV=0x1F;

MODULE_SCU.PERPLLCON0.U = ScuPerPllCon0.U;

/*PowerupthesystemPLLandperipheralPLL*/

MODULE_SCU.SYSPLLCON0.B.PLLPWD=1;

MODULE_SCU.PERPLLCON0.B.PLLPWD=1;

/*Checkiftheconfigurationisvalid*/

TimeoutCount=0x3000;

while((MODULE_SCU.SYSPLLSTAT.B.PWDSTAT==1U)||(MODULE_SCU.PERPLLSTAT.B.PWDSTAT==1U))

{

if(((--(TimeoutCount))<=?0)

????????{

????????????(Error?)?=?1;

????????????break;

????????}

????}??

/*?Check?if?the?configuration?is?valid?*/

????TimeoutCount?=?0x5000;

????while((MODULE_SCU.SYSPLLSTAT.B.K2RDY?==?0U)?||

???????????????(MODULE_SCU.PERPLLSTAT.B.K2RDY?==?0U)?||

??????????????(MODULE_SCU.PERPLLSTAT.B.K3RDY == 0U)) ???????????????????????????????????????

????{

????????if (((--TimeoutCount)) <= 0)

????????{

????????????(Error ) = 1;

????????????break;

????????}

????}??

????MODULE_SCU.SYSPLLCON1.B.K2DIV?=?5;

????ScuPerPllCon1.U?=?MODULE_SCU.PERPLLCON1.U;

????ScuPerPllCon1.B.K2DIV?=?1;

????ScuPerPllCon1.B.K3DIV?=?1;

????MODULE_SCU.PERPLLCON1.U?=?ScuPerPllCon1.U;

????TimeoutCount = 0x5000;

????while((MODULE_SCU.SYSPLLSTAT.B.K2RDY == 0U) ||

???????????????(MODULE_SCU.PERPLLSTAT.B.K2RDY == 0U) ||

???????????????(MODULE_SCU.PERPLLSTAT.B.K3RDY?==?0U))???????????????????????????????????????

????{

????????if?(((--(TimeoutCount))?<=?0)

????????{

????????????(Error?)?=?1;

????????????break;

????????}

????} ?

/*?Start?PLL?locking?for?latest?set?values*/

????MODULE_SCU.SYSPLLCON0.B.RESLD?=?1;??

????MODULE_SCU.PERPLLCON0.B.RESLD = 1;

???/*Wait?for?PLL?lock?to?be?set*/

????TimeoutCount?=?0x3000;

????while((MODULE_SCU.SYSPLLSTAT.B.LOCK?==?0U)?||?(MODULE_SCU.PERPLLSTAT.B.LOCK?==?0U))?????????????????????????????????????????

????{

????????if (((--(TimeoutCount)) <= 0)

????????{

????????????(Error ) = 1;

????????????break;

????????}

????}??

????UnlockEndinit_Core0();

}

Note:下一篇文章介紹TC3xx芯片時鐘系統(tǒng)的時鐘分配CCU.

審核編輯:湯梓紅

-

mcu

+關注

關注

146文章

17984瀏覽量

367184 -

鎖相環(huán)

+關注

關注

35文章

598瀏覽量

89674 -

pll

+關注

關注

6文章

889瀏覽量

136445 -

時鐘系統(tǒng)

+關注

關注

1文章

110瀏覽量

12198

原文標題:TC3xx芯片Clock System功能詳解-鎖相環(huán)PLL

文章出處:【微信號:汽車電子嵌入式,微信公眾號:汽車電子嵌入式】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

TC3xx芯片的Endinit功能詳解

LabVIEW鎖相環(huán)(PLL)

鎖相環(huán)原理

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

鎖相環(huán)(PLL)的工作原理及應用

TC3xx芯片DMU介紹

pll鎖相環(huán)倍頻的原理

用FPGA的鎖相環(huán)PLL給外圍芯片提供時鐘

TC3xx芯片的MPU功能詳解

TC3xx芯片時鐘系統(tǒng)的鎖相環(huán)PLL詳解

TC3xx芯片時鐘系統(tǒng)的鎖相環(huán)PLL詳解

評論