繼實現(xiàn)振蕩器閃爍相噪理論統(tǒng)一后,我們再次實現(xiàn)頻率綜合器的相噪理論一統(tǒng)。

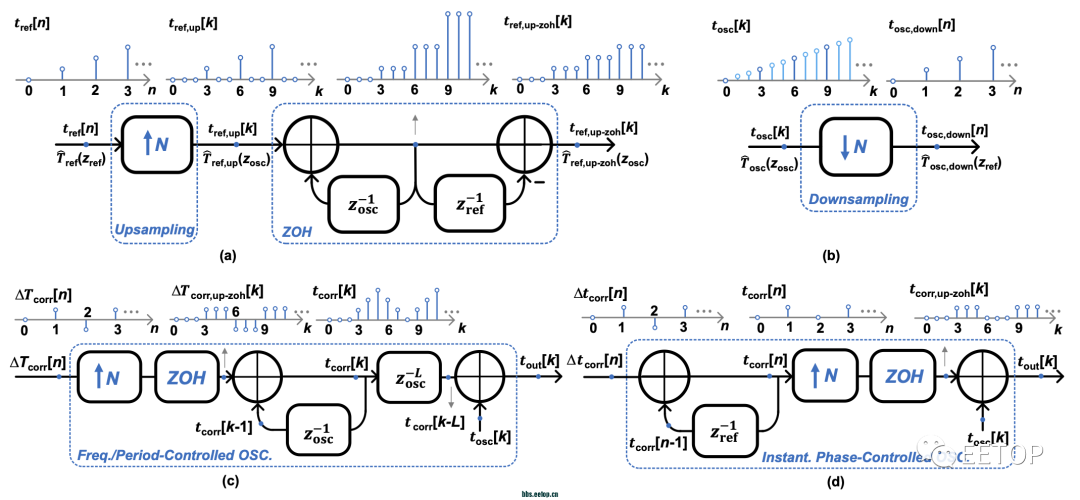

引入全新的 “雙z變量多速率時間戳建模”,將幾乎全部頻率鎖定技術(特別是極低抖動,高帶寬),如:亞/采樣模擬PLL,全數(shù)字PLL,注入鎖定/電荷分享鎖定,納入到統(tǒng)一的理論框架,為設計6G通信所需的sub-50fs抖動頻綜,提供系統(tǒng)的理論指導。

我們認為,基于ADC的ADPLL和電荷分享鎖定技術,將是極低抖動的先進CMOS工藝頻綜的重要發(fā)展趨勢。

(特別地,基于新模型,我們厘清了經(jīng)典架構 “亞采樣鎖相環(huán)” 中長期存在的關于 “電荷泵噪聲不被放大N^2倍” 的理論迷思(myth)。)

1.雙z變量多速率時間戳建模基礎

2.極低抖動,高帶寬APLL建模

3.電荷分享鎖定,注入鎖定建模

4.計算結果和時域仿真結果驗證

-

振蕩器

+關注

關注

28文章

3975瀏覽量

140578 -

CMOS工藝

+關注

關注

1文章

59瀏覽量

15904 -

PLL電路

+關注

關注

0文章

92瀏覽量

6745 -

頻率綜合器

+關注

關注

1文章

14瀏覽量

6410 -

時域仿真

+關注

關注

0文章

2瀏覽量

4617

發(fā)布評論請先 登錄

極低抖動頻率綜合器的多速率時間戳建模

極低抖動頻率綜合器的多速率時間戳建模

評論