1 簡介

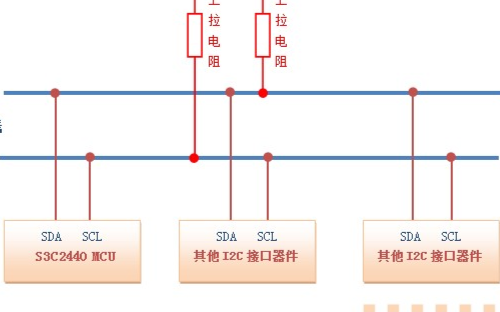

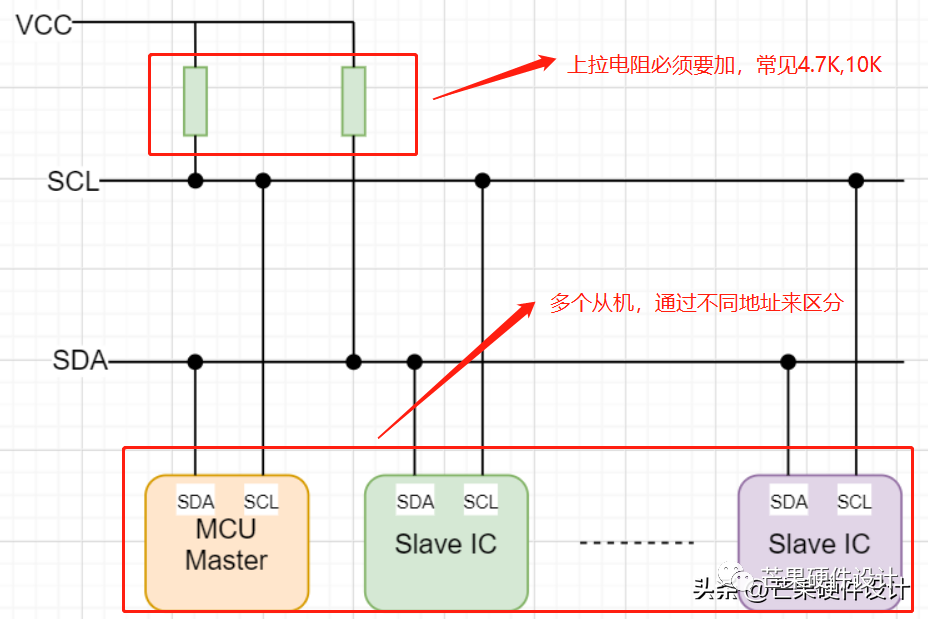

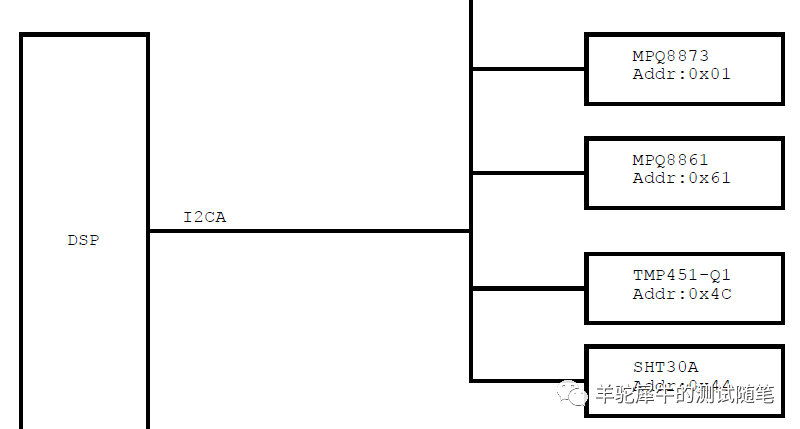

IIC-BUS的英文全稱是Inter-Integrated Circuit Bus,其主要的目的是實現微控制器與外圍設備進行數據傳輸。它是一種半雙工通信方式,通信方式簡單,僅包含SDA(數據總線)和SCL(時鐘總線)組成。通信總線通常由主設備和從設備組成,從設備是通過設備地址來進行區分,在同一時刻,設備之間數據傳送只能由一個設備傳送給對應地址的設備。

什么是I2C總線主設備和從設備?

主設備 :I2C總線的主導者,能向從西安發送起始信號和中止信號,且能決定總線數據的發送與接收。另外,主設備能發送指令,同時既能向從設備讀取數據也能向從設備寫入數據。

從設備 :I2C總線的被動者,對主設備發送的數據做出及時響應。從設備的類型比較多,具體可以是EEROM、各種傳感器等。

I2C總線最大可以掛在多少個設備?

最大電容限制(標準模式和快速模式為400pF,高速模式為500pF)。且在實際的應用過程中最好保證I2C設備不超過8個(經驗之談)。

有些設備預留地址線的僅3位(相同設備最多掛在8個,2^3=8),甚至更少。

I2C總線最大的傳輸速率為多少?

| 序號 | 模式 | 最大速率 |

|---|---|---|

| 1 | 標準模式 | 100kb/s |

| 2 | 快速模式 | 400kbit/s |

| 3 | 高速模式 | 3.4Mbit/s |

之前在講串口電路時,有講過一個“波特率”概念,不知道是否有人知道波特率和比特率的區別?

波特率:單位時間內傳輸的碼元個數。

比特率:單位時間內傳輸的二級制位數。

二者換算關系為:比特率=波特率×log2n,此處分享一個計算的案例:

2 I2C總線特點

- 簡單和靈活 :僅包含數據線和時鐘線,物理通信鏈路簡單。

- 雙向傳輸 :主設備既能向從設備發送數據,從設備也能向主設備發送數據。

- 時鐘同步 :采用串行時鐘總線,能有效保證數據的準確性。

- 多種設備支持 :總線上掛載的設備,可以掛在多種不同設備,不受設備類型的影響。

3 編碼規則

- 起始信號和停止信號

- 起始信號:當時鐘信號為高電平時,數據線由高電平變為低電平的過程。

- 停止信號:當時鐘信號為高電平時,數據線由低電平變為高電平的過程。

注意: 在IIC空閑時,SDA、SCL都是保持高電平 。(I2C信號出現故障時,先查看SCL和SDA的電平)

- 應答信號和非應答信號

- 應答信號:當主設備傳送8位數據結束后,主機會將SDA線拉高,此時如果從設備正確接收數據則會將SDA拉低并在SCL高電平時保持低電平,這個信號為ACK信號

- 非應答信號:如果在傳輸8位數據后從機沒有將SDA拉低則該信號為NACK。

4 信號傳輸

IIC總線上面的每一個設備都有唯一的地址與之對應,信號傳輸時也是根據指定的地址找到設備來傳輸信號。

- 寫操作

- 主設備確定從設備地址,發送起始信號;

- 向總線設備的地址以及數據傳輸方向;

- 從設備收到主設備的信號后沒回復一個應答信號;

- 主設備向從設備以字節為單位發送數據,且每發送一個數據,都會接收來自從設備的應答信號;

- 數據發送完成后,從設備發送一個停止信號,表明此次數據傳輸結束。

- 讀數據

- 主設備確認從設備地址,發送起始信號;

- 向總線上發送從設備的地址以及讀取數據的命令;

- 對應的從設備回復應答信號;

- 從設備向主設備回復主設備要讀取的數據;

- 從設備數據發送給完成后,主機向從設備發送一個非應答信號,然后中止數據的讀取。

5 總線仲裁

總線上存在兩個及兩個以上主設備時,每個節點都可以作為主設備向總線上發送命令或者數據。當總線上同時存在兩個或者兩個以上主設備發送信號時,就會造成總線沖突。此時,就需要進行I2C總線仲裁。分以下兩個方面來說:

時鐘同步

時鐘總線(SCL)具有“線與”的邏輯功能,就是當總線有任意一個節點向總線發送低電平時,總線就會呈現低電平的狀態。(所有節點呈現高電平時,總線表現為高電平)

SDA仲裁

SDA仲裁也是基于“線與”的邏輯功能,節點發送數據后,比較總線與發送的數據是否一致,保持一致則繼續發送,否則退出競爭。SDA仲裁這種機制保證了I2C中線上即使有多個主設備,也不會造成數據丟失。

仲裁過程

- 設備1和設備2同時向設備發送起始信號,總線上電平與發送電平一致,繼續發送數據;

- 設備1和設備2同時向設備發送低電平,總線上電平與發送電平一致,繼續發送數據;

- 設備1發送高電平。設備2發送低電平。此時,總線呈現低電平狀態。總線的電平與設備1發送的電平不一致,退出競爭,且變為從設備。設備2繼續發送數據。

5 上拉電阻計算

由于I2C總線端口的高電平是通過上拉電阻實現,線上的電平從低變高時,電源通過上拉電阻對線上負載電容CL充電,這需要一定的上升時間。

電容充電一般公式:

整理可得:

I2C規范將低于VIL或0.3VDD的電壓定義為邏輯低電平,同樣將高于VIH或0.7VDD的電壓定義為邏輯高電平。由上式可以求得:

即T1=0.356675*CL

所以最大上拉電阻為:

結論:電源電壓決定上拉電阻的最小值,總線負載電容決定上拉電阻的最大值。

當Tr取最大值,CL取最小值時,R有最大值。

| 模式 | 上升沿的最大時間 | 總線負載最大容限 |

|---|---|---|

| 標準模式 | 1000ns | 400pF |

| 快速模式 | 300ns | 400pF |

| 高速模式 | 120ns | 550pF |

所以快速模式下,負載電容為50pF:

-

微控制器

+關注

關注

48文章

7925瀏覽量

153868 -

電路設計

+關注

關注

6701文章

2530瀏覽量

213555 -

總線

+關注

關注

10文章

2956瀏覽量

89450 -

I2C

+關注

關注

28文章

1537瀏覽量

127228 -

I2C總線

+關注

關注

8文章

408瀏覽量

61984

發布評論請先 登錄

虛擬I2C總線串行顯示電路介紹

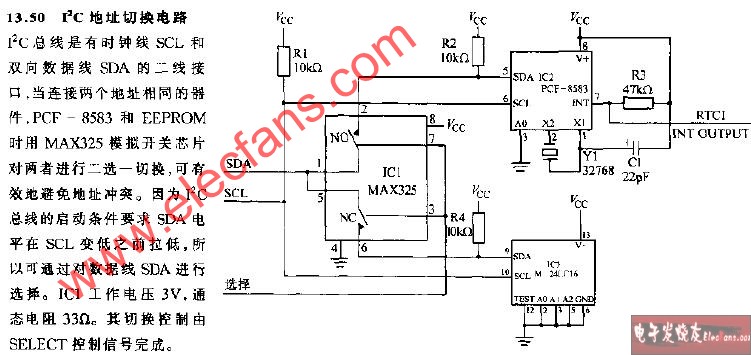

I2C總線的電路設計

怎么成為硬件電路設計高手?

I2C總線硬件電路設計

使用GPIO模擬I2C的電路設計

基于CP2120的SPI與I2C總線接口轉換電路設計

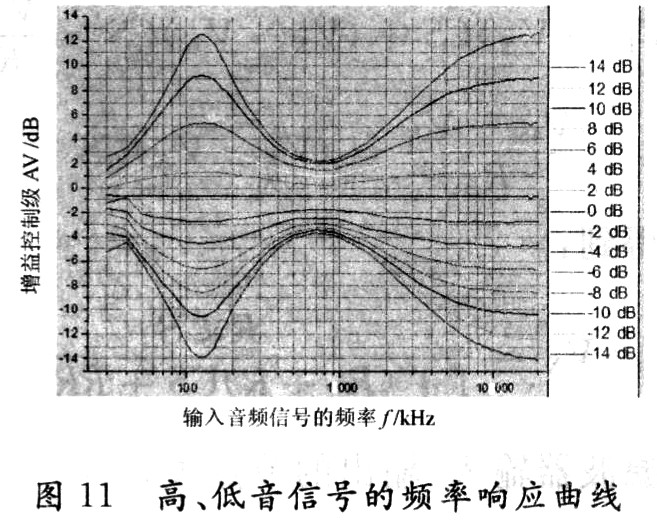

基于I2C總線控制的音頻處理電路設計

基于I2C總線控制的音頻處理電路設計

基于CPLD的I2C總線接口設計

硬件設計:接口--不同電源系統下I2C總線電平轉換電路(電橋)設計

硬件電路設計之I2C電路設計

硬件電路設計之I2C電路設計

評論