DFX設計中有4類Bitstream文件,包括:

Partialbitstreams

Blanking bitstreams

Clearingbitstreams

Full configuration bitstreams

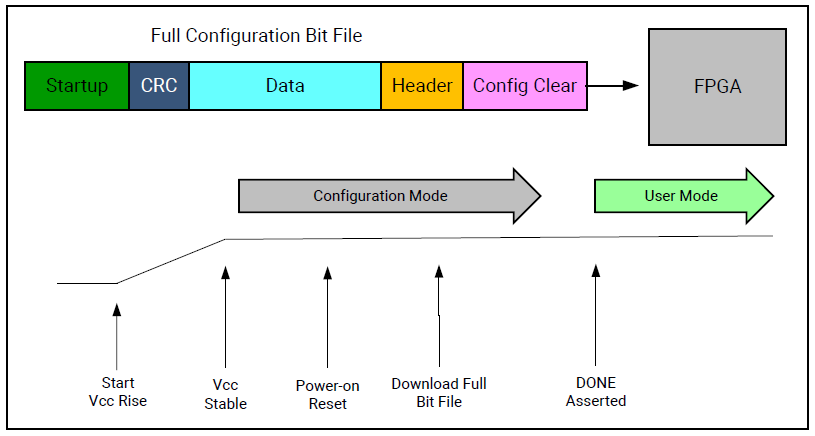

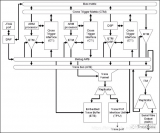

Fullconfiguration bitstreams對應的是靜態區加動態區的完整設計,因此,該文件與傳統的非DFX工程生成的bitstream從文件格式到文件結構均是一致的。同時使用方法也是一致的。另外,一些特征如對bitstream文件進行加密和壓縮也是支持的。另一方面,這里的RP可以是黑盒子,即RP沒有任何功能,這樣可以最大程度縮減bitstream大小,如果再結合bitstream的壓縮特性,那么就可以進一步提升FPGA初始配置時間。Fullconfiguration bitstreams的加載過程如下圖所示。加載完成且驗證通過,DONE信號就會抬高,FPGA就進入用戶模式,圖中綠色標記。

Partial bitstreams

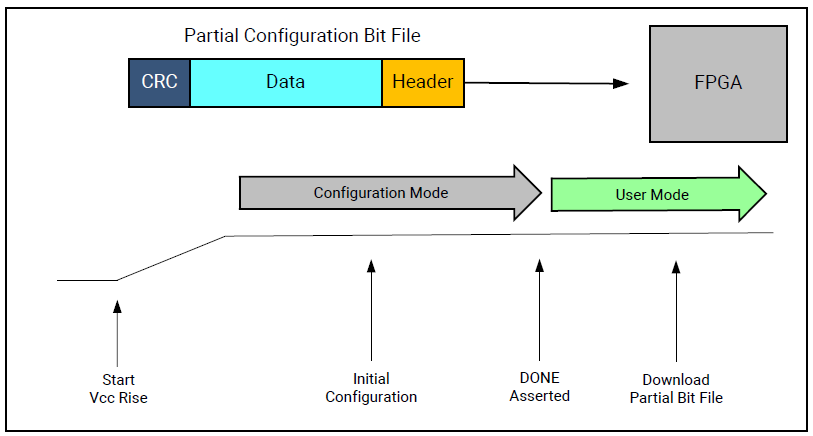

當Full configuration bitstreams加載完成之后,就可以根據需要加載Partialbitstreams已切換動態區的功能,這正是DFX的本質。Partialbitstream有著和Full configuration bitstreams相同的文件結構,不同之處在于Partial bitstream僅針對FPGA指定區域也就是動態區。此外,針對DFX,Partial bitstreams還具有幀CRC檢測和自動初始化(加載Partial bitstream后動態區可以進入已知狀態)功能,同樣也支持加密和壓縮功能。Partial bitstream文件的大小和動態區的大小是成正比的,例如:RP大小是整個FPGA大小的20%,那么基本上Partial bitstream的大小也是Full configuration bitstream大小的20%。Partial bitstream是獨立的,包含了地址、頭、尾等具體信息,需要采用從模式加載如JTAG,Slave Serial或者Slave SelectMap,ICAP,PCAP(針對Zynq7000 SoC)和MCAP(針對UltraScale和UltraScale+)。Partial bitstream可通過命令write_bitstream自動生成,也就是在生成Fullconfiguration bitstream的時候會自動生成Partial bitstream文件,而無需額外操作。Partial bitstream的文件名也是有特定的規律的,假如

Fullconfiguration bitstream文件為

top_first.bit,

RP對應的Pblock名字為pblock_red,

那么Partial bitstream文件名就為

top_first_pblock_red_partial.bit。

當FPGA進入用戶模式時就可以加載Partial bitstream文件,如下圖所示。對于UltraScale,在加載Partialbitstream之前先要加載Clearing bitstream,這時DONE信號為低,加載完Clearing bitstream之后,DONE信號依然保持低電平,之后加載Partial bitstream,完成之后DONE信號才會抬高。

Blankingbitstream

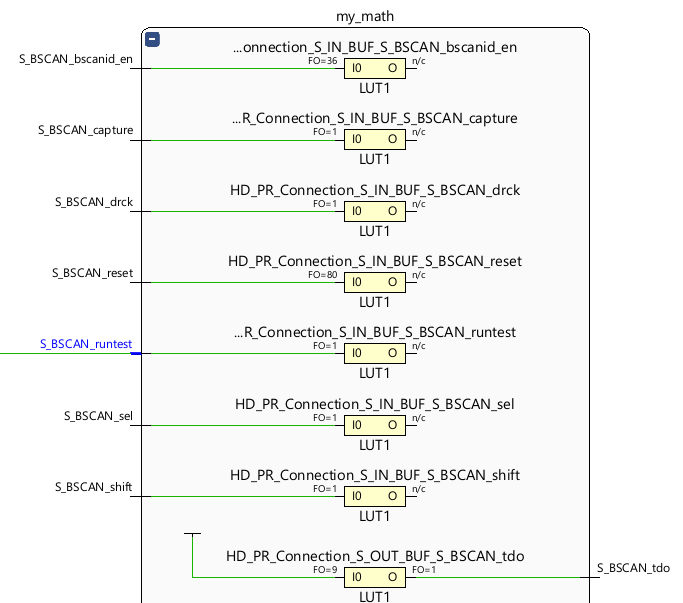

Blankingbitstream是一種特定的partial bitstream,它是在初始Configuration(靜態區+完整動態區)的基礎上,將靜態區替換為黑盒子,同時將相應I/O插入LUT,這被稱為會盒子(Greybox,注意和Blackbox是不同的)如下圖所示。盡管這時動態區的邏輯功能已經被移除,但需要注意如果靜態區要從動態區穿過也就是靜態區使用了動態區的一些布線資源,那么這些布線資源仍然會被保留。

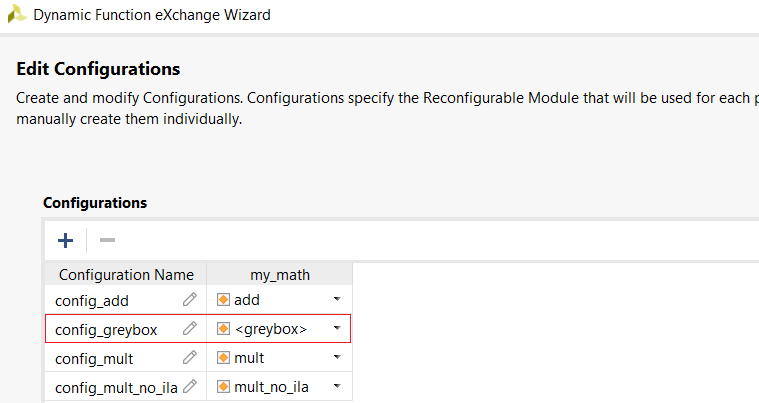

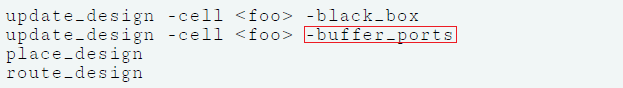

在Vivado圖形界面方式下,可以很容易將動態區配置為Greybox,如下圖所示。如果采用Tcl腳本則需要注意使用兩次update_design命令,前者將動態區替換為Blackbox,后者對動態區相應I/O插入LUT。

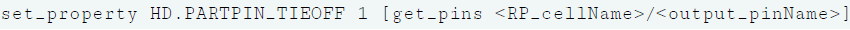

當對輸出端口插入LUT時,默認情況下LUT輸出為低電平,但可通過如下Tcl腳本修改其輸出值,這里用到了屬性HD.PARTPIN_TIEOFF。

Clearing bitstreams

Clearingbitstreams只是針對UltraScale芯片(不包括UltraScale+芯片),這是器件結構本身需求所決定的。Clearing bitstreams本身并不是Partialbitstreams,它只包含了動態區小于10%的Frame,因此其大小也就小于對應動態Partial bitstreams的10%。它需要和相應的Partial bitstream一起使用。例如設計中有一個RP,該RP下有兩個RM,分別為RM1和RM2,那么就會生成兩個Clearing bitstream文件:

rm1_rp1_partial_clear.bit

rm2_rp1_partial_clear.bit

也會生成兩個Partial bitstream文件:

rm1_rp1_partial.bit

rm2_rp1_partial.bit

當由RM1切換到RM2時,先加載rm1_rp1_partial_clear.bit,緊隨其后加載rm2_rp1_partial.bit。反之,由RM2切換到RM1時,需要先加載rm2_rp1_partial_clear.bit,再加載rm1_rp1_partial.bit。工具會自動生成Clearingbitstream文件,它和Partial bitstream文件的名字不同之處是在結尾多了“_clear”。

Copyright@FPGA技術驛站 轉載事宜請私信|獲得授權后方可轉載

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22034瀏覽量

618035 -

文件

+關注

關注

1文章

579瀏覽量

25355 -

bit

+關注

關注

0文章

48瀏覽量

32440 -

dfx設計

+關注

關注

0文章

6瀏覽量

185

原文標題:DFX設計中有哪些bit文件?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

write_bitstream日志出現錯誤

請問怎么在Vivado中保存Bitstream文件?

請問如何在Vivado中更改比特流文件的位置?

硬件電路常見的DFX設計環節詳解

DFX設計中Bitstream文件詳解

DFX設計中Bitstream文件詳解

評論