電源抑制比怎么提高

電源抑制比是衡量電源噪聲抑制效果的重要指標。提高電源抑制比可以有效降低電源噪聲對電子設備的影響,提升設備的穩定性和性能。本文將從信號處理、濾波器設計、抑制電路、電源線布局等多個方面詳細介紹提高電源抑制比的方法。

一、信號處理:

信號處理是提高電源抑制比的重要手段之一。以下是幾種常用的信號處理方法:

1. 數字濾波器:

數字濾波器可以通過濾除不需要的頻率成分來抑制電源噪聲。常見的數字濾波器包括低通濾波器、高通濾波器和帶通濾波器,根據噪聲頻譜分布的不同選擇合適的數字濾波器。

2. 自適應濾波器:

自適應濾波器可以根據濾波器輸入和輸出之間的差異自動調整濾波器參數,從而提高濾波效果。自適應濾波器適合應對噪聲頻譜分布寬泛或快速變化的情況。

3. 信號平均:

信號平均可以通過多次采樣和平均來降低噪聲干擾,提高信噪比。在電源測量等領域常用的平均方法有算術平均、遞推平均和循環平均等。

二、濾波器設計:

濾波器是提高電源抑制比的核心設備。以下是濾波器設計及應用中需要注意的細節:

1. 濾波器類型選擇:

根據電源噪聲頻譜分布情況及應用領域需求,選擇合適的濾波器類型。常見的濾波器類型有LC濾波器、RC濾波器、帶通濾波器等,根據具體情況進行選用。

2. 濾波器參數調整:

濾波器參數的調整會直接影響濾波器的頻率特性和抑制效果。通過優化濾波器的通帶、阻帶等參數,可以提高濾波器的性能。

3. 濾波器連接方式設計:

多級濾波器和平行濾波器是常用的組合方式,通過合理設計濾波器的連接方式和級數可以達到較好的抑制效果。

三、抑制電路:

電源抑制電路是一種主動抑制電源噪聲的技術手段。以下是幾種常用的抑制電路:

1. 電源線濾波器:

電源線濾波器通過在電源線上串聯電感、電容等元件,形成對電源噪聲的阻抗匹配和抑制作用,有效濾除電源噪聲。

2. 噪聲補償電路:

噪聲補償電路利用電源噪聲的特性,通過采集噪聲信號進行主動補償,抵消噪聲的影響。

3. 電源線路開關:

電源線路開關可以將電源與負載進行隔離,減少噪聲傳遞。采用高速開關可以進一步提高電源抑制比。

四、電源線布局:

合理的電源線布局對于提高電源抑制比也是至關重要的。以下是幾個需要注意的細節:

1. 電源線長短:

盡量縮短電源線的長度,減少電源線上的電壓降和串擾。

2. 電源線走向:

避免將電源線與其他信號線走向交叉,減少干擾。

3. 電源線絕緣:

采用絕緣好的電源線,減少電壓漏泄及噪聲干擾。

結論:

提高電源抑制比的方法主要包括信號處理、濾波器設計、抑制電路和電源線布局等。通過選擇適當的信號處理方法,設計合理的濾波器參數,應用有效的抑制電路以及合理布局電源線,可以有效提高電源抑制比,降低電源噪聲對電子設備的影響,提升設備的穩定性和性能。

-

電源抑制比

+關注

關注

0文章

78瀏覽量

13856 -

電源噪聲

+關注

關注

3文章

155瀏覽量

17746

發布評論請先 登錄

海洋儀器電源抑制比測試方案26800元起

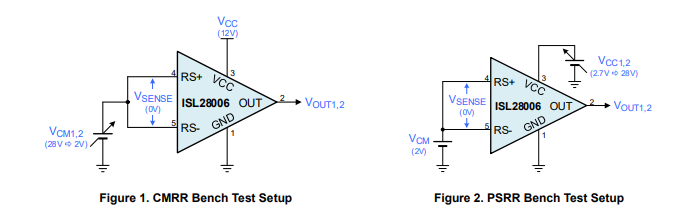

ISL28006:測量共模和電源抑制比

怎么測ADS1299芯片的共模抑制比?

詳解LDO電路的電源抑制比

如何準確計算電源引起的運放輸出失調電壓?1200字搞定運放電路選型之電源抑制比PSRR

電源抑制比怎么提高

電源抑制比怎么提高

評論