對于UltraScale/UltraScale+芯片,幾乎FPGA內(nèi)部所有組件都是可以部分可重配置的,這包括CLB中的查找表(LUT)、觸發(fā)器(FF)、移位寄存器(采用LUT實現(xiàn))、分布式RAM/ROM等,Block如BRAM、URAM、DSP、GT(高速收發(fā)器)、PCIe、CMAC、Interlaken MAC等,SYSMON(XADC和System Monitor),時鐘單元如BUFG、MMCM和PLL等,I/O相關(guān)單元如ISERDES、OSERDES和IDELAYCTRL等。只有與配置相關(guān)組件必須在靜態(tài)區(qū),包括BSAN、CFG_IO_ACCESS、EFUSE_USR、ICAP、FRAME_ECC、MASTER_JTAG、STARTUP、和USR_ACCESS。

Pblock的大小

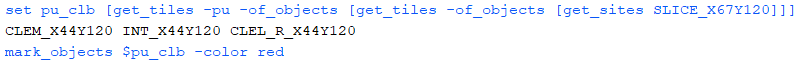

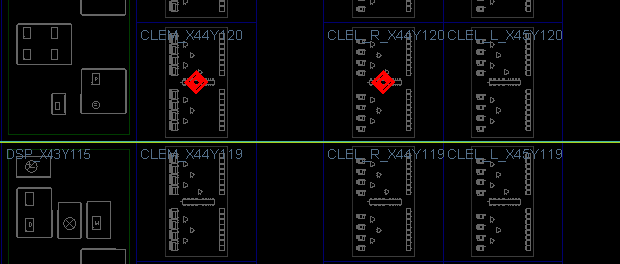

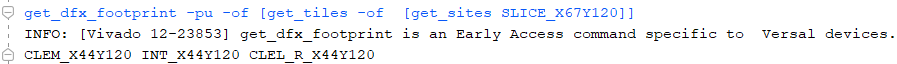

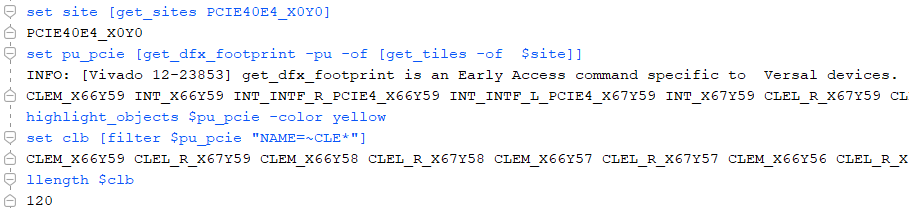

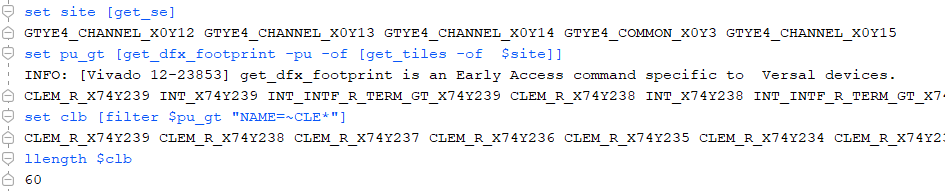

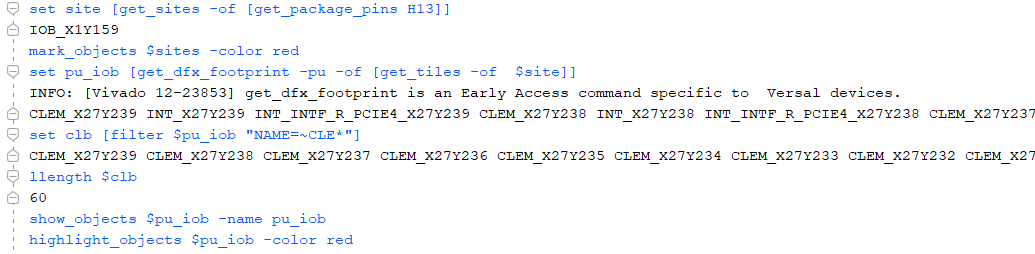

DFX設(shè)計中,動態(tài)區(qū)都有專屬的Pblock。Pblock的最小范圍是由PU(ProgrammableUnit)決定的,而一個PU的大小是跟資源類型緊密相關(guān)的。例如,對于SLICE,其PU為所屬的CLB以及與之相鄰的一個CLB,同時還包括這兩個CLB共享的Interconnect,這可通過如下Tcl命令獲取,注意最外層的Tcl命令get_tiles需要添加選項-pu。如果Vivado版本是2023.1或更高版本,可以使用命令get_dfx_footprint外加選項-pu實現(xiàn)同樣功能。

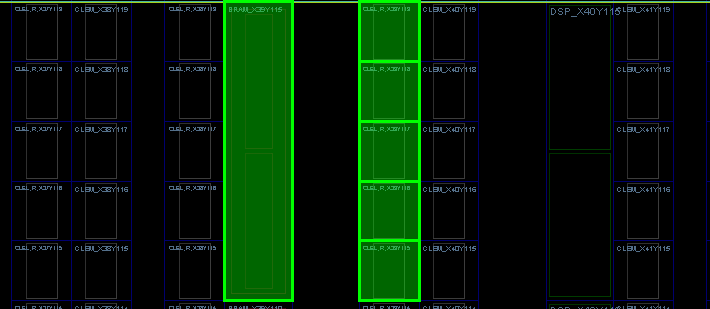

對于BRAM(36Kb),其PU包含自身之后還包含與之相鄰的5個CLB以及共享的Interconnect,如下圖所示。

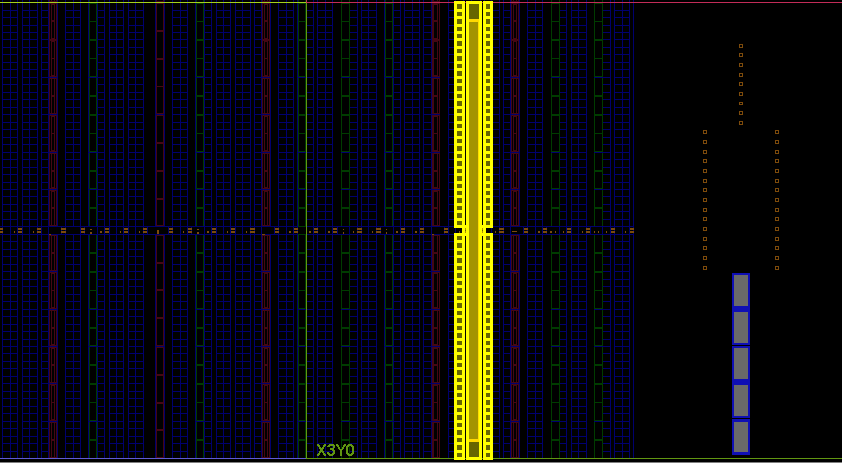

對于PCIE,其PU包含自身之后還包含兩側(cè)各60個共120個CLB以及共享的Interconnect,如下圖所示。

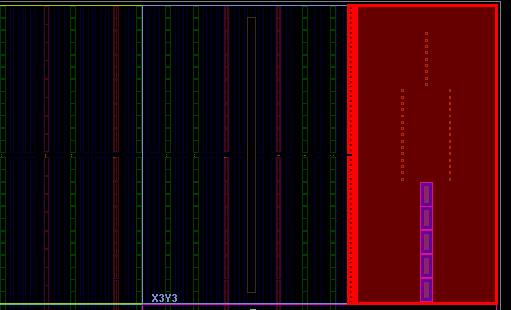

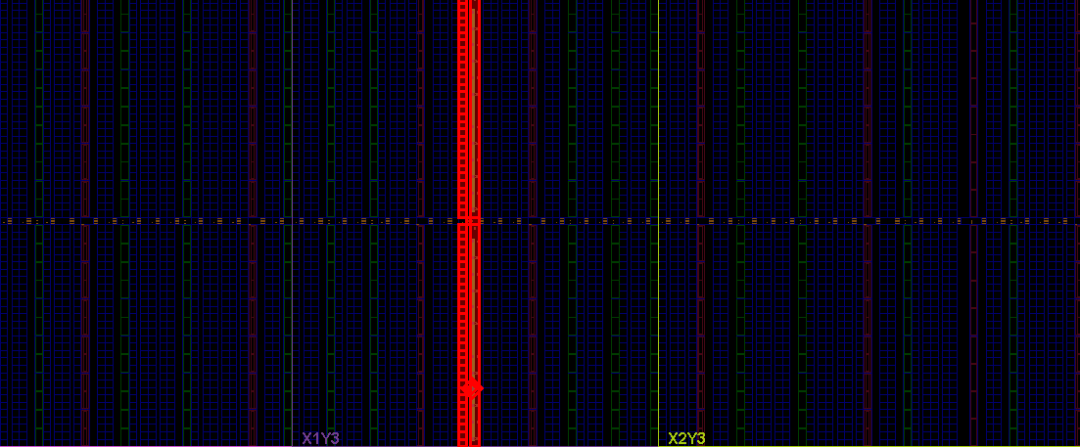

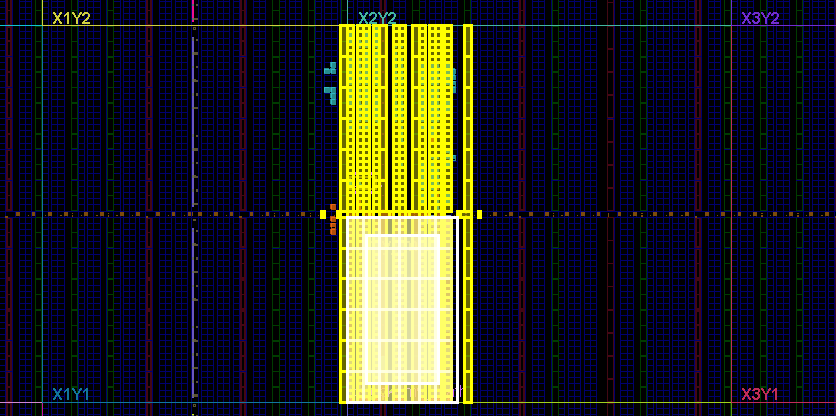

對于高速收發(fā)器,其PU包含自身之外還包含與之相鄰的60個CLB以及共享的Interconnect,如下圖所示。

對于PackagePin,其PU包含其所在IO Bank的所有資源,如下圖所示,這也表明了同一個IO Bank內(nèi)的管腳要么均在靜態(tài)區(qū),要么均在動態(tài)區(qū)。

在UltraScale/UltraScale+ FPGA中,Pblock不再需要設(shè)置屬性RESET_AFTER_RECONFIG,但需要將屬性SNAPPING_MODE設(shè)置為on。這樣工具給了用戶足夠的靈活性去畫Pblock,但為了保證Pblock不違反PU的要求,工具又會在已畫Pblock的基礎(chǔ)上自動調(diào)整,這正是SNAPPING_MODE的作用。

對于DFX工程,在執(zhí)行完布局布線之后,會生成一個名為hd_visual的文件目錄,在此文件夾下有兩個Tcl文件,如下圖所示,文件名為pblock__Placement/Routing_AllTiles.tcl。

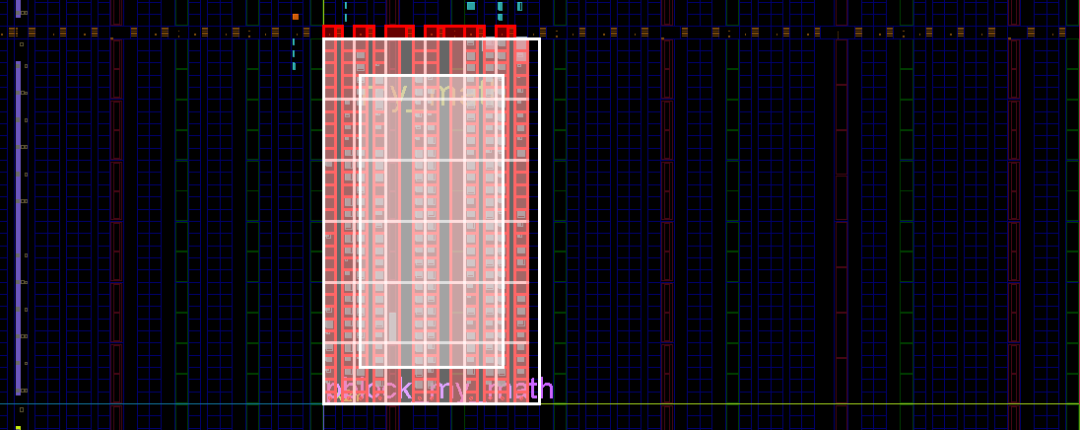

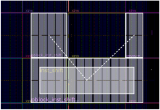

打開布線后的網(wǎng)表文件,執(zhí)行source命令即可看到整個Pblock的實際布局范圍和布線范圍。圖中白色高亮標(biāo)記為原始Pblock范圍,紅色標(biāo)記為實際Pblock的布局范圍,黃色標(biāo)記為實際Pblock的布線范圍,包括了擴展的布線區(qū)域。對于Vivado2023.1及之后版本,可直接使用命令get_dfx_footprint實現(xiàn)同樣功能。

sourcepblock_my_math_placement_AllTiles.tcl

對于UltraScale/UltraScale+ FPGA,動態(tài)區(qū)Pblock的高度可以不是以Clock Region對齊,這在上述案例中已有體現(xiàn)。換言之,上圖中Pblock所在Clock Region的其他區(qū)域仍然可以供靜態(tài)區(qū)使用,但不能供其他動態(tài)區(qū)使用。這意味著同一個ClockRegion只能擁有一個RP,所以可以看到“可重構(gòu)”仍然是按照ClockRegion作為基礎(chǔ)幀執(zhí)行的。

擴展的布線區(qū)域

對于動態(tài)區(qū)的Pblock,其屬性CONTAIN_ROUTING的值為TRUE,意味著動態(tài)區(qū)的布線也在劃定的Pblock內(nèi)。但實際上,最終的布線區(qū)域是可擴展的,不僅是已畫好的Pblock,還包括Pblock之外的布線資源。從而,與RM輸入/輸出端口相連的網(wǎng)線就可能出現(xiàn)擴展的布線區(qū)域內(nèi)(Pblock之外),但只要Partition Pin落在擴展區(qū)域內(nèi),就可以不用限定PartitionPin的位置。這里并不是說Pblock的形狀不規(guī)范才導(dǎo)致布線區(qū)域擴展,即使是正規(guī)的矩形Pblock也可能會有擴展的布線區(qū)域。

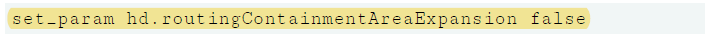

但一個事實是擴展的布線區(qū)域一定是以Clock Region為邊界的。由于動態(tài)區(qū)布線區(qū)域的擴展,動態(tài)區(qū)對應(yīng)的bit文件大小就會增大,但是如果動態(tài)區(qū)對應(yīng)的bit文件大小比設(shè)計性能更為關(guān)鍵,可通過如下命令禁止動態(tài)區(qū)性能擴展。另外,7系列FPGA是不支持動態(tài)區(qū)布線區(qū)域擴展這一功能的。從Vivado2020.2開始,算法的改進促使動態(tài)區(qū)布線擴展區(qū)域更小同時這種更小的布線區(qū)域?qū)Σ季€性能影響也更小。

?

?

審核編輯:劉清

-

移位寄存器

+關(guān)注

關(guān)注

3文章

287瀏覽量

22649 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2032瀏覽量

61880 -

ECC

+關(guān)注

關(guān)注

0文章

97瀏覽量

20962 -

DFx

+關(guān)注

關(guān)注

0文章

35瀏覽量

10801

原文標(biāo)題:針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(1)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(2)

采用UltraScale/UltraScale+芯片的DFX設(shè)計注意事項

賽靈思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

閑話Zynq UltraScale+ MPSoC(連載1)

Xilinx 宣布Vivado設(shè)計套件開始支持16nm UltraScale+產(chǎn)品早期試用

Zynq UltraScale+ MPSoC的發(fā)售消息

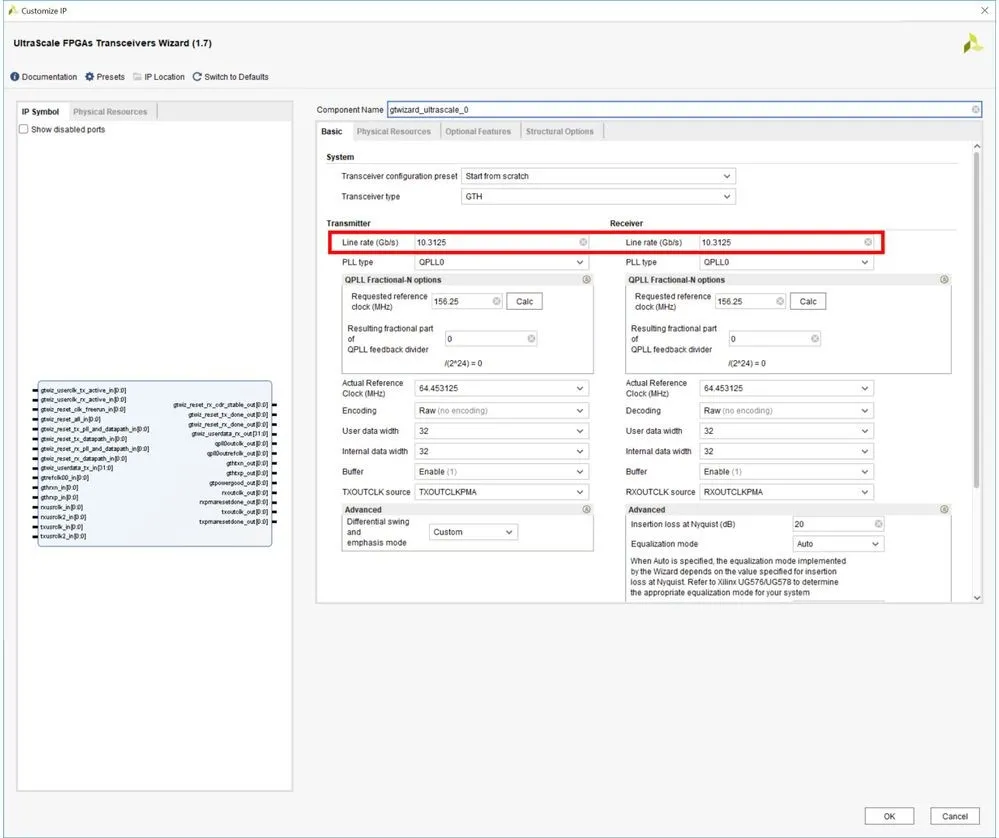

UltraScale/UltraScale+ GTH/GTY 收發(fā)器線速率設(shè)置的方法

UltraScale/UltraScale+的時鐘資源

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設(shè)計

使用加密和身份驗證來保護UltraScale/UltraScale+ FPGA比特流

UltraScale和UltraScale+ FPGA封裝和管腳用戶指南

AMD推出全新Spartan UltraScale+ FPGA系列

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(1)

針對UltraScale/UltraScale+芯片DFX應(yīng)考慮的因素有哪些(1)

評論