BLC,即 Black Level Correction。cmos 在傳出黑色圖像的時(shí)候,由于自身結(jié)構(gòu)的原因,黑色畫面?zhèn)鞒龅南袼刂挡⒉皇?0,為了達(dá)到最大的對(duì)比度,我們需要通過算法將這個(gè)黑色幀的值回歸到 0 的值。

我們可以將它想象成照片的“基準(zhǔn)線”。每張照片都有自己的黑色基準(zhǔn),而BLC 的任務(wù)就是確保這個(gè)基準(zhǔn)是穩(wěn)定的,這樣我們拍攝出來的照片在暗部細(xì)節(jié)上才會(huì)一致。BLC 模塊小,但是魔力巨大。

這是我用 matlab 產(chǎn)生的一張黑幀圖,看著很黑,其實(shí)它是一張 5-15 隨機(jī)數(shù)組成。通常黑幀值的大小與溫度以及增益值相關(guān),不過通常情況下采用減去一個(gè)固定值的方式來平衡黑幀沒有歸零的現(xiàn)象。

運(yùn)算方式:

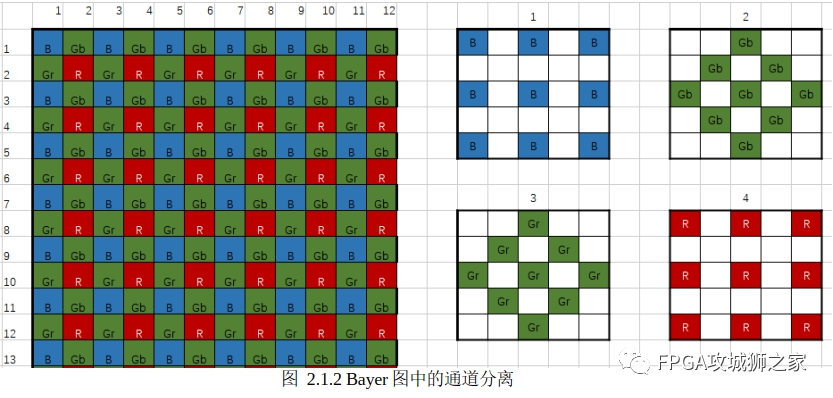

1,分離出四個(gè)通道。

2,求四個(gè)通道的均值。

3,整圖減去相應(yīng)通道的均值。

4,拉升到原來的范圍。

當(dāng)然,這里必須提到,我說的是理想情況下,有些 sensor 非常不理想。

比如黑電平分布非常不均勻,左側(cè)值大右側(cè)值小,或者上邊的值大下邊的值小等情況,還有就是黑電平與增益,曝光時(shí)間都相關(guān)了。

這個(gè)時(shí)候如果想要更理想的圖像效果,就需要改進(jìn)算法。此處我的重點(diǎn)是算法的初步了解和 FPGA 實(shí)現(xiàn),更復(fù)雜的算法就不作為開源部分了。

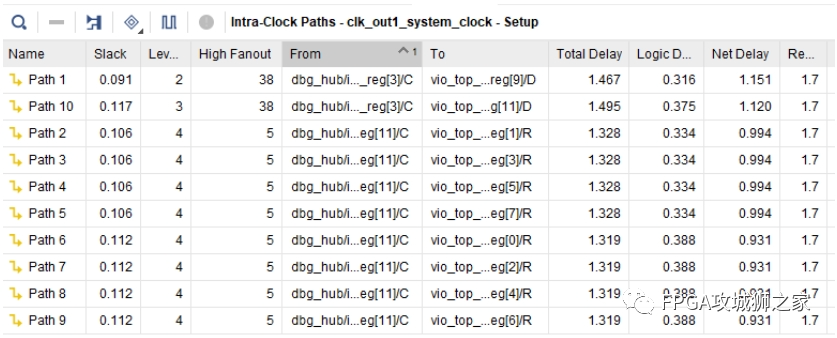

此時(shí)需要收斂的,不僅僅是 BLC ,還有 DPC 一起了,目前還是將項(xiàng)目約束到 600M,呈現(xiàn)的效果如下:

目前看到最差的十條路徑中,來自于 VIO ,所以算法代碼似乎還是有一定的裕量可以爭(zhēng)取一下。也就是可以跑到 600M 以上了。

最后別忘了仿真,將FPGA輸出的數(shù)據(jù)輸出到txt,再在matlab中將txt轉(zhuǎn)換成image。此處的方法就是和上一節(jié)的DPC雷同,就不做重復(fù)解釋。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615316 -

matlab

+關(guān)注

關(guān)注

189文章

2999瀏覽量

233493 -

圖像處理

+關(guān)注

關(guān)注

27文章

1326瀏覽量

57811 -

ISP

+關(guān)注

關(guān)注

6文章

491瀏覽量

52897

原文標(biāo)題:FPGA圖像處理_ISP算法BLC

文章出處:【微信號(hào):gh_99a29eb83412,微信公眾號(hào):FPGA攻城獅之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一文詳解FPGA的圖像處理技術(shù)

FPGA設(shè)計(jì)經(jīng)驗(yàn)之圖像處理

FPGA圖像與視頻處理培訓(xùn)

基于DSP和FPGA的通用圖像處理平臺(tái)設(shè)計(jì)

ECT圖像重建算法的FPGA實(shí)現(xiàn)

基于FPGA的紅外圖像處理系統(tǒng)及算法設(shè)計(jì)

ISP圖像處理芯片

如何使用FPGA實(shí)現(xiàn)圖像的中值濾波算法

FPGA學(xué)習(xí)-基于FPGA的圖像處理

國(guó)內(nèi)圖像信號(hào)處理(ISP)廠商名錄

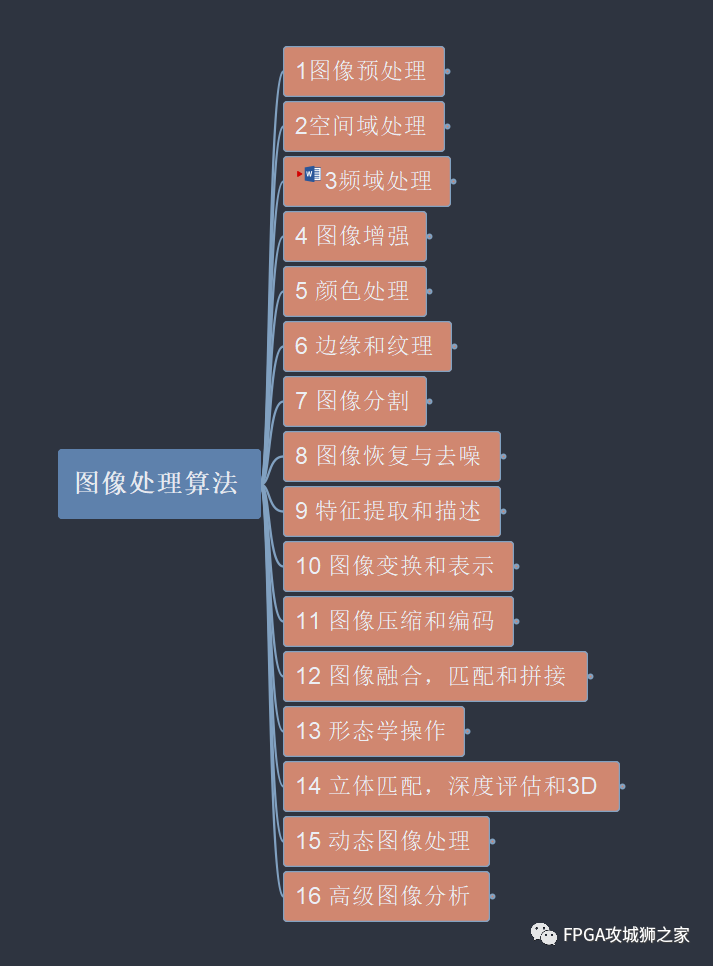

FPGA圖像處理算法有哪些

基于FPGA的常見的圖像算法模塊總結(jié)

FPGA圖像處理—ISP算法BLC知識(shí)詳解

FPGA圖像處理—ISP算法BLC知識(shí)詳解

評(píng)論