圖像識別和分析對于產品創新至關重要,但需要高工作負載,對服務質量要求嚴格。解決方案如GPU無法滿足低延遲和高性能要求。DLP FPGA是一種可行的選擇,本文將探討如何實現這種技術。

圖像識別和分析在各種產品創新中具有重要作用。然而,這些應用通常涉及高工作負載,對服務質量有嚴格要求。目前的解決方案,如GPU,無法同時兼顧低延遲和高性能要求。

為了在應用深度學習的同時提供良好的用戶體驗,可以在FPGA上架構一個超低延遲和高性能的DLP(深度學習處理器)。

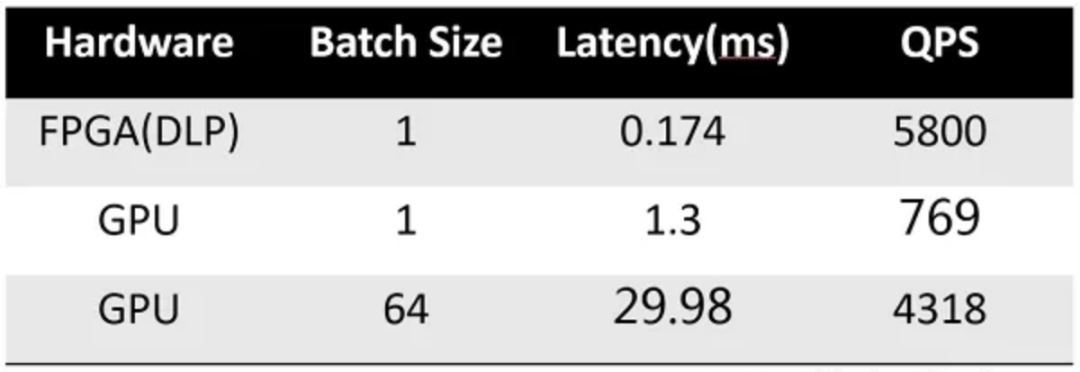

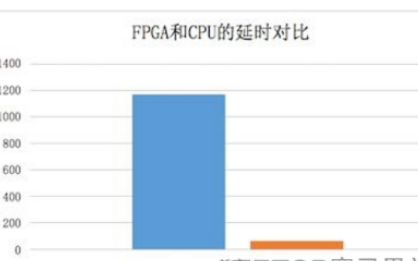

DLP FPGA可以同時支持稀疏卷積和低精度數據計算,同時定義了一個定制的ISA(指令集架構),以滿足對靈活性和用戶體驗的要求。使用Resnet18(稀疏內核)的延遲測試結果顯示,FPGA的延遲只有0.174ms。

在本文中,我們將簡要討論如何通過新的DLP FPGA實現這樣的結果。

1 架構

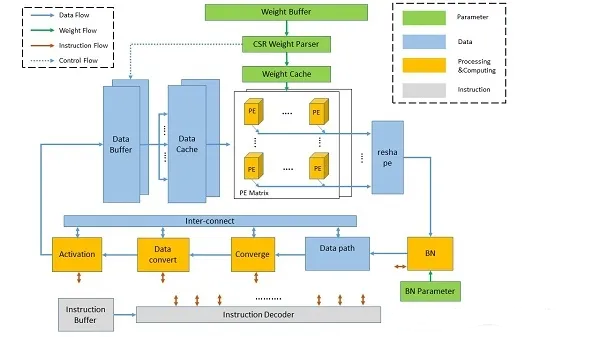

新開發的DLP有4種模塊,根據其功能進行分類:

計算:卷積、批量歸一化、激活和其他計算

數據路徑:數據存儲、移動和重塑

參數:存儲權重和其他參數,解碼

指令:指令單元和全局控制

DLP中的Protocal Engine(PE)可以支持:

Int4數據類型輸入。

Int32數據類型輸出。

Int16量化

這種PE能提供超過90%的效率。此外,DLP的重量加載支持CSR解碼器和數據預取。

2 訓練

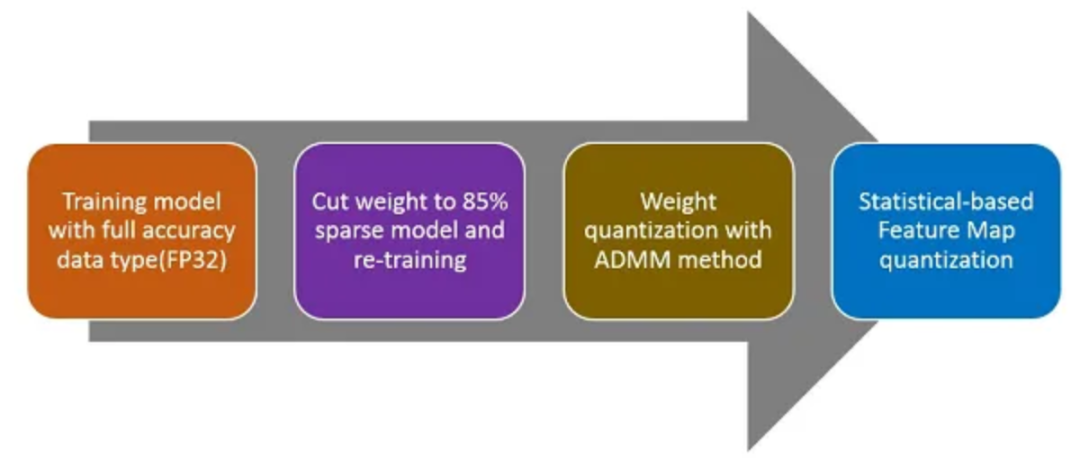

需要重新訓練來開發一個高精確度的模型。下面有4個主要步驟來獲得稀疏權重和低精度數據特征圖。

我們用一種有效的方法將Resnet18模型訓練到稀疏和低精度(1707.09870)。我們方法中的關鍵部分是離散化。我們專注于壓縮和加速深度模型,其網絡權重由非常小的比特數表示,被稱為極低比特神經網絡。然后我們將這個問題建模為一個離散約束的優化問題。

借用乘法交替方向法(ADMM)的思想,我們將連續參數與網絡的離散約束解耦,并將原來的硬問題鑄成幾個子問題。我們建議使用梯度外算法和迭代量化算法來解決這些子問題,與傳統的優化方法相比,這些算法會導致更快的收斂。

在圖像識別和物體檢測方面的大量實驗證明,當涉及到極低比特的神經網絡時,所提出的算法比最先進的方法更有效。

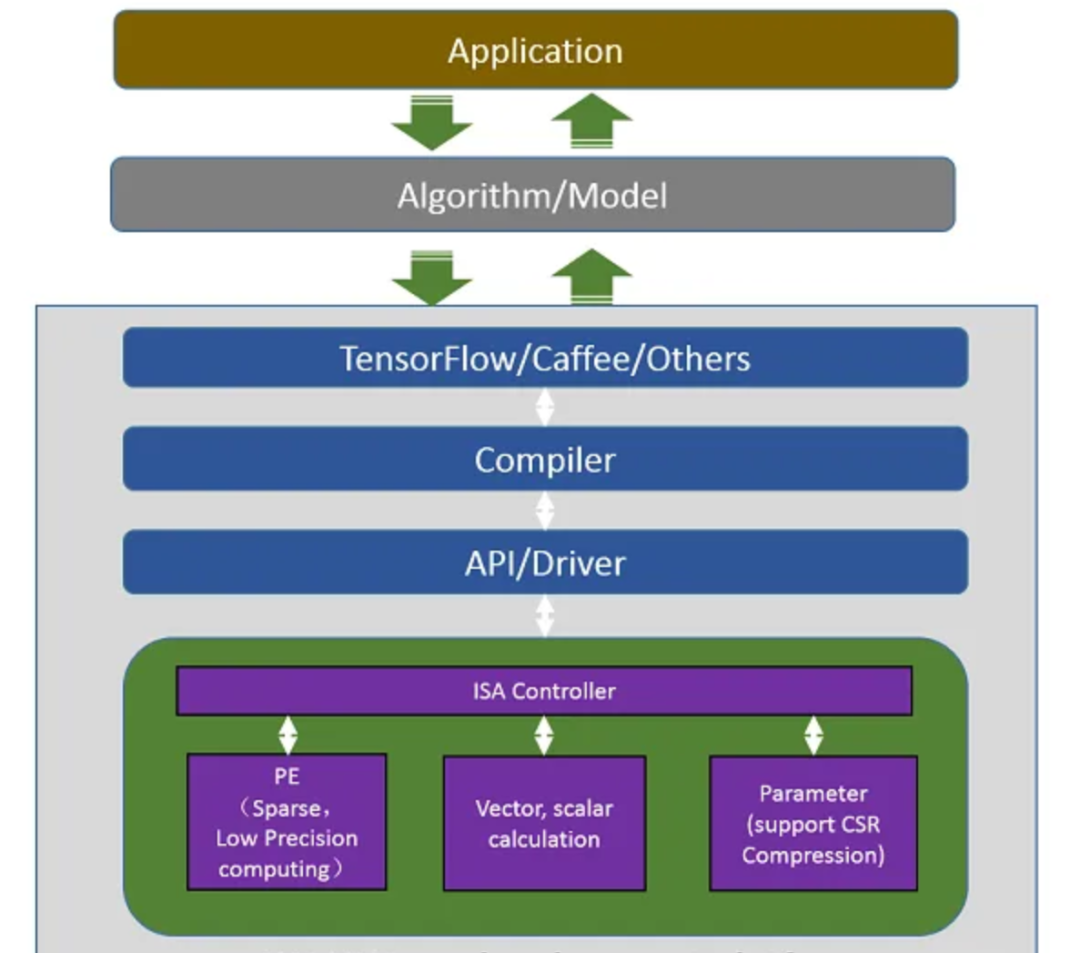

3 ISA/編譯器

如前所述,對于大多數在線服務和使用場景,僅有低延遲是不夠的,因為算法模型會經常變化。正如我們所知,FPGA的開發周期非常長;通常需要幾周或幾個月的時間來完成一個定制的設計。為了解決這一挑戰,我們設計了工業標準架構(ISA)和編譯器,以減少模型升級的時間,使之僅為幾分鐘。

SW-HW共同開發平臺由以下項目組成:

編譯器:模型圖分析和指令生成。

ISA控制器:指令解碼、任務調度、多線程流水線管理。

4 硬件卡

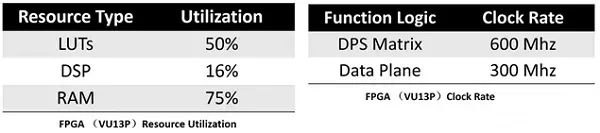

DLP是在FPGA卡上實現的,它有PCIe和DDR4內存。DLP與該FPGA卡相結合,可以使在線圖片搜索等應用場景更高效用戶體驗更好。

5 結果

使用Resnet18的FPGA測試結果表明,我們的設計實現了超低水平的延遲,同時在低于70W的芯片功率下保持了非常高的性能。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19896瀏覽量

235255 -

FPGA

+關注

關注

1645文章

22050瀏覽量

618531 -

圖像識別

+關注

關注

9文章

527瀏覽量

39115 -

dlp

+關注

關注

6文章

386瀏覽量

62209 -

深度學習

+關注

關注

73文章

5561瀏覽量

122795

原文標題:使用FPGA制作低延時高性能的深度學習處理器

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA做深度學習能走多遠?

FPGA構建高性能DSP

【FPGA干貨分享六】基于FPGA協處理器的算法加速的實現

用FPGA 嵌入式處理器實現高性能浮點元算

【詳解】FPGA:深度學習的未來?

采用Sitara處理器PRU-ICSS的高性能脈沖序列輸出 (PTO)

飛思卡爾高性能ColdFire微處理器簡介

什么是深度學習?使用FPGA進行深度學習的好處?

通過利用FPGA協處理器實現對汽車娛樂系統進行優化設計

如何通過DLP FPGA實現低延時高性能的深度學習處理器設計呢?

如何通過DLP FPGA實現低延時高性能的深度學習處理器設計呢?

評論