FPGA(可編程邏輯門陣列)是一種集成電路芯片,具有可編程的數字邏輯功能。多功能數字鐘系統利用FPGA技術實現了時鐘的顯示、計時、報時等功能。本文將詳細介紹FPGA多功能數字鐘系統的原理。

一、FPGA基本原理

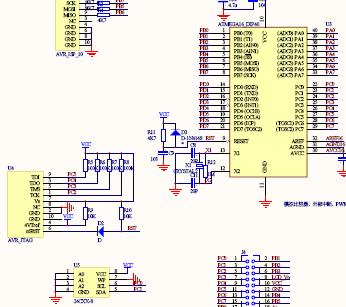

FPGA是一種基于可編程邏輯門陣列的集成電路芯片。其主要由邏輯元件和I/O(輸入輸出)元件組成。邏輯元件通常包括可編程門陣列(PLA)和可編程觸發器陣列(PTA),用于實現數字邏輯運算和時鐘處理。I/O元件用于與外部設備進行通信。

FPGA的工作原理是通過內部配置存儲器存儲的邏輯功能表,將輸入信號轉換為輸出信號。這種可編程性讓FPGA適用于多種應用場景,包括數字鐘系統。

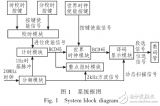

二、多功能數字鐘系統組成

- 時鐘模塊

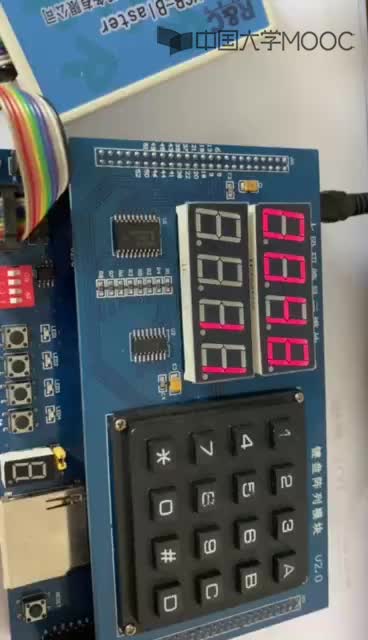

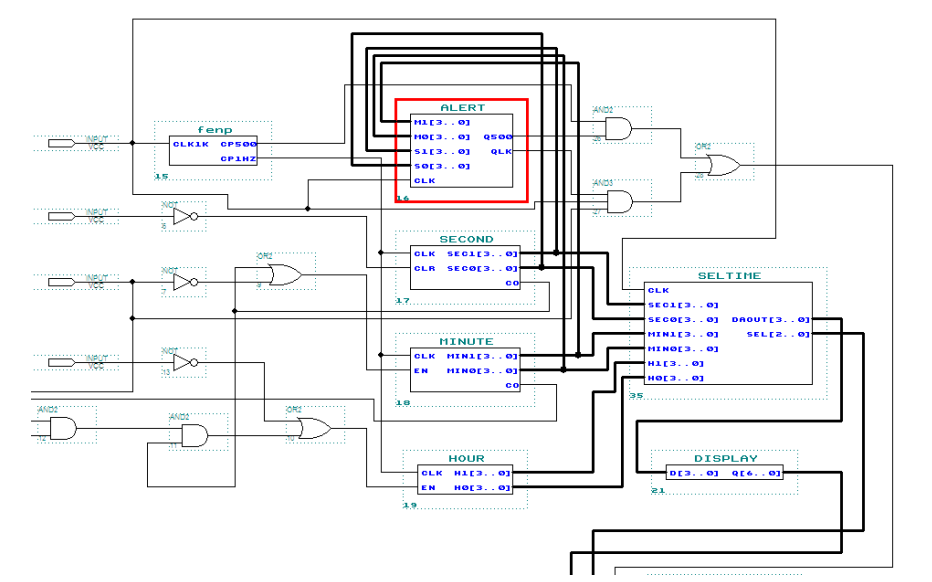

時鐘模塊是多功能數字鐘系統的核心模塊,用于控制時鐘的計時和顯示。時鐘模塊通常由一個計數器和數碼管顯示模塊組成。

計數器用于計時,通過遞增計數器的值來表示時間。計數器可以設置為24小時制或12小時制,并可以設置鬧鐘的時間。

數碼管顯示模塊將計數器的值轉換為數碼管顯示的數值。該模塊通常由七段數碼管驅動器和數碼管組成。七段數碼管驅動器將計數器的十進制值轉換為對應的數碼管段驅動信號,從而實現數碼管的顯示。

- 報時模塊

報時模塊用于根據當前時間進行報時。該模塊通常由語音播放器和時鐘控制器組成。語音播放器用于播放預存的語音報時內容,時鐘控制器用于控制報時的時間間隔。 - 按鍵模塊

按鍵模塊用于用戶對多功能數字鐘系統的操作。按鍵模塊由多個按鍵和按鍵掃描電路組成。按鍵掃描電路將按鍵狀態轉換為數字信號,并傳遞給FPGA芯片。 - 蜂鳴器模塊

蜂鳴器模塊用于報警和鬧鐘功能。蜂鳴器接收來自FPGA芯片的控制信號,當出現報警或鬧鐘時,發出相應的聲音信號。

三、多功能數字鐘系統工作流程

多功能數字鐘系統的工作流程主要包括時鐘顯示、計時、報時和鬧鐘功能。

- 時鐘顯示

時鐘顯示是多功能數字鐘系統的基本功能。時鐘模塊中的計數器根據當前時間不斷遞增,并將其轉換為數碼管顯示。數碼管顯示模塊將計數器的十進制值轉換為對應的數碼管段驅動信號,從而實現時鐘的顯示。 - 計時功能

計時功能是指可以通過多功能數字鐘系統進行時間的累加和顯示,通常用于計時比賽、烹飪等需要計時的場合。用戶可以通過按鍵模塊設置計時開始和結束時間,并將計時結果顯示在數碼管上。 - 報時功能

報時功能是多功能數字鐘系統的一個重要功能。報時模塊會根據設置的時間間隔,定時進行語音報時。報時模塊會根據當前時間判斷是否需要進行報時,若需要報時,則會觸發語音播放器播放預存的報時內容。 - 鬧鐘功能

鬧鐘功能是多功能數字鐘系統的常見功能。用戶可以通過按鍵模塊設置鬧鐘的時間,當時間到達設置時間時,蜂鳴器模塊會發出聲音信號作為提醒。

四、總結

FPGA多功能數字鐘系統是利用FPGA技術實現的,具有時鐘顯示、計時、報時和鬧鐘等功能。時鐘模塊用于計時和顯示,報時模塊用于定時播放報時內容,按鍵模塊用于用戶的操作,蜂鳴器模塊用于報警和鬧鐘功能。通過這些組件的精密配合,多功能數字鐘系統能夠滿足用戶對時間的顯示和管理需求。

本文詳細介紹了FPGA多功能數字鐘系統的原理和工作流程,并通過對每個組件的分析,說明了其功能和作用。通過對FPGA多功能數字鐘系統的原理了解,可以更好地了解其工作原理和應用場景,進一步提高其性能和功能。

-

FPGA

+關注

關注

1644文章

22000瀏覽量

615769 -

邏輯運算

+關注

關注

0文章

57瀏覽量

9937 -

數字鐘

+關注

關注

9文章

160瀏覽量

31761 -

集成電路芯片

+關注

關注

0文章

62瀏覽量

9776

發布評論請先 登錄

如何設計基于FPGA的多功能數字鐘?

怎樣去設計一種多功能數字鐘

基于FPGA和Quartus II的多功能數字鐘設計與實現

基于fpga的數字鐘設計的兩款方案(含程序)

基于Quartus II平臺的多功能數字鐘的設計

FPGA多功能數字鐘系統原理

FPGA多功能數字鐘系統原理

評論