大家好,我是痞子衡,是正經搞技術的痞子。今天痞子衡給大家分享的是i.MXRT1170內部RAM的ECC初始化工作可全部由ROM完成。

痞子衡之前寫了三篇文章 《M7 FlexRAM ECC》、《M4 L-MEM ECC》、《MECC64》 分別介紹了 i.MXRT1170 片上 2MB RAM 的不同 ECC 控制器用法,尤其是第三篇文章最后介紹了當 MECC64 特性被激活之后,BootROM 雖然使能了 MECC1&2 但并沒有一步到位初始化相應的全部 RAM 區域(僅初始化了 48KB ROM RW 區),這給后續調試和應用開發帶來了一定隱患。

難道 BootROM “挑了事”就這么不負責任嗎?當然不是!我們需要主動讓 BootROM 負全責,今天痞子衡就聊一聊這個話題:

一、RAM ECC初始化相關Fuse位

前面的文章講了 Fuse MECC_ENABLE bit 主要控制 MECC64 模塊是否被激活,但其實它還有另外一層關于 RAM ECC 初始化控制。痞子衡在此列出了如下跟 RAM ECC 初始化相關的全部 Fuse bit,其中最核心的是 ROM_ECC_PRELOAD_POR bit,這個 bit 決定是否在芯片 POR 上電時讓 ROM 去做額外的 RAM ECC 初始化工作。

Fuse 0x840[2] - MECC_ENABLE bit, 是否開啟MECC模塊(默認0即不開啟)

ROM做ECC初始化是否包括M7 FlexRAM OCRAM、M4 TCM、M4 OCRAM(默認0即不包含)

Fuse 0x840[15] - TCM_ECC_ENABLE bit, ROM做ECC初始化是否包括M7 TCM(默認0即不包含)

Fuse 0x850[7] - OCRAM1_DISABLE bit, ROM做ECC初始化是否包括扣去ROM RW區之后的OCRAM1(默認0即包含)

Fuse 0x850[6] - OCRAM2_DISABLE bit, ROM做ECC初始化是否包括OCRAM2(默認0即包含)

Fuse 0x950[0] - ROM_ECC_PRELOAD_POR bit,是否在POR時讓ROM去初始化RAM ECC(默認0即不做)

上述區域里關于 OCRAM1 ECC 初始化需要特別說一下,因為前 48KB 是 ROM RW 區,其在 ROM 剛執行就被初始化過了,這里 ROM_ECC_PRELOAD_POR bit 控制的初始化就不再重復操作 ROM RW 區了。因為如果包含這個區域,那就會破壞 ROM 程序的正常執行了。

二、檢驗ROM做RAM ECC初始化工作

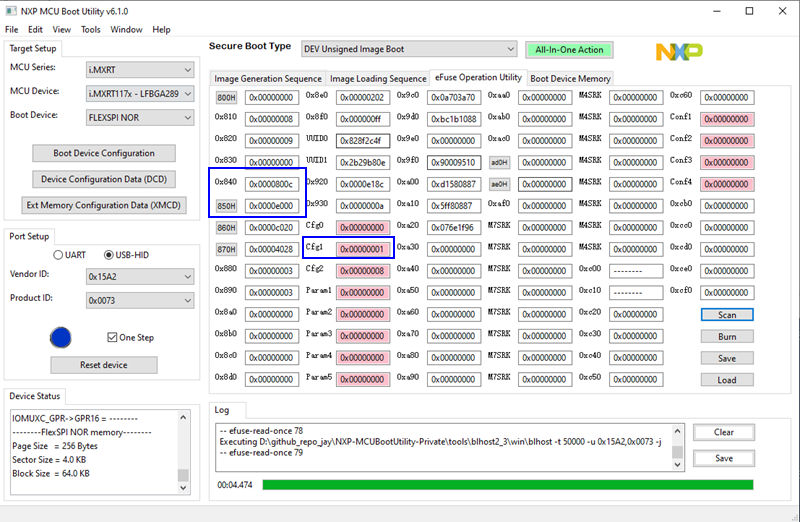

為了檢驗 BootROM 是否很好地完成了 RAM ECC 初始化工作,痞子衡找了塊 RT1170 板卡使用 MCUBootUtility 工具將 Fuse 0x840、0x850、0x950 全部設成 RAM ECC 初始化使能狀態:

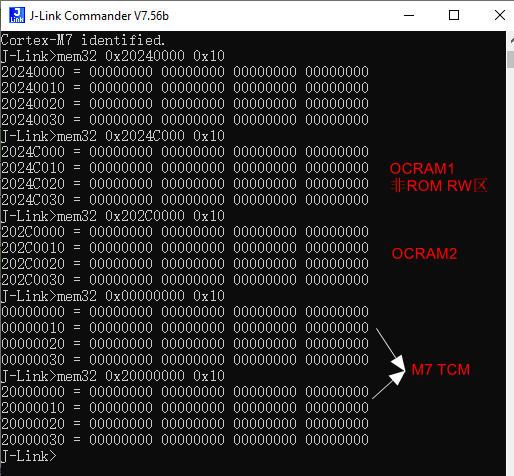

芯片保持 Serial Downloader 模式,掛上 JLink 讀取內存,好家伙,內部 RAM 全部整齊劃一地保持全 0 隊形,不再是隨機值了,看起來 ROM 很好地完成了 ECC 初始化工作。

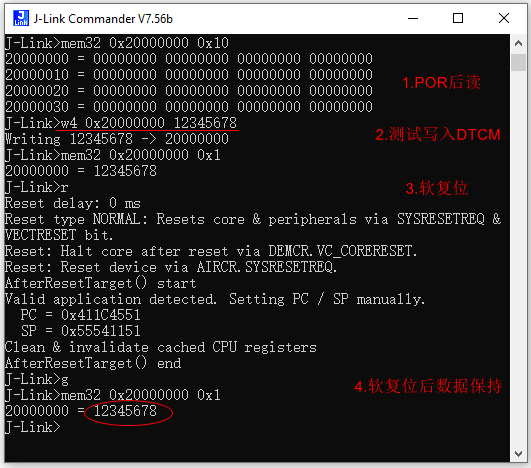

這時候嘗試在 DTCM 里寫入一些測試數據,然后做軟件復位,再回讀發現測試數據依然保持著,這說明 ROM 只在 POR 硬復位時做一次 RAM ECC 初始化,其后發生軟復位導致 ROM 再執行時就會跳過 ECC 初始化。

至此,i.MXRT1170內部RAM的ECC初始化工作可全部由ROM完成痞子衡便介紹完畢了,掌聲在哪里~~~

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52498瀏覽量

440712 -

mcu

+關注

關注

146文章

17980瀏覽量

366743 -

ROM

+關注

關注

4文章

578瀏覽量

87352 -

初始化

+關注

關注

0文章

50瀏覽量

12109

原文標題:MCU內部SRAM的ECC初始化竟可由ROM完成!

文章出處:【微信號:pzh_mcu,微信公眾號:痞子衡嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MCU重新上電后,如何進行ECC初始化?

關于ISE調用ROM IP核并初始化的問題?

FPGA片內ROM初始化文檔創建

SRAM上的ECC是否默認啟用?哪些代碼使SRAM上的ECC啟用?

是否沒有必要初始化SRAM_L因為它不受ECC保護?

求助,MCU重新上電后如何進行ECC初始化?

FPGA的ROM初始化問題討論

四種常見的ROM、RAM初始化文件格式

如何使用FPGA內部的ROM以及程序對該ROM的數據讀操作

根據MATLAB中的偽隨機交織器產生的交織圖案初始化到ROM的實驗

MCU初始化流程——從上電到main()之間

MCU單片機GPIO初始化該按什么順序配置?為什么初始化時有電平跳變?

MCU內部SRAM的ECC初始化竟可由ROM完成

MCU內部SRAM的ECC初始化竟可由ROM完成

評論