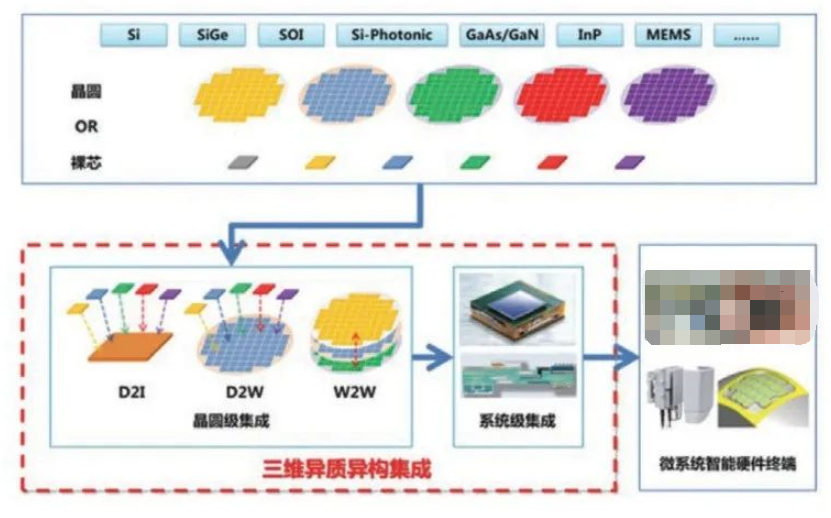

近年來,三維異質(zhì)集成技術(shù)正在嶄露頭角,通過協(xié)同設(shè)計和微納制造工藝,將不同材料和功能的電子器件堆疊在一起。其獨(dú)特之處在于,不同類型的器件垂直組合,形成了更小巧且高效的器件單元。然而,器件層與層之間的連接一直是該技術(shù)的巨大挑戰(zhàn),將器件從襯底剝離極容易發(fā)生機(jī)械故障。此時,基于二維材料的電子器件展現(xiàn)出巨大潛力,這些材料具有極低的剛度和幾乎為零的內(nèi)應(yīng)力,或許能夠完全擺脫傳統(tǒng)剛性三維材料在三維異質(zhì)集成技術(shù)中的物理限制。

三維異質(zhì)集成示意圖

近日,圣路易斯華盛頓大學(xué)Sang-Hoon Bae、麻省理工學(xué)院Jeehwan Kim、韓國延世大學(xué)Jong-Hyun Ahn等研究者合作在Nature Materials雜志上發(fā)表論文,展示了基于二維材料的晶體管和憶阻器的三維單片異構(gòu)集成,可作為高效率人工智能(AI)處理器執(zhí)行AI任務(wù)。

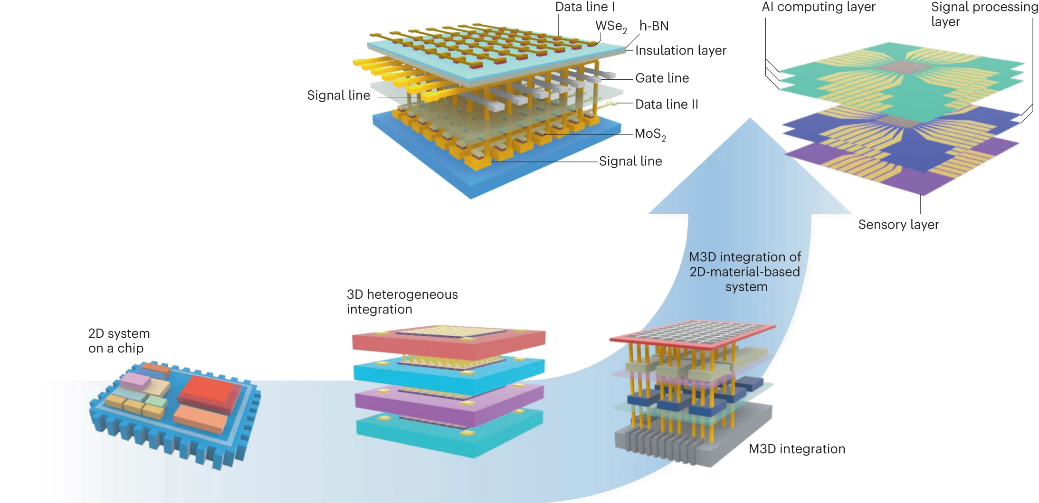

三維單片異構(gòu)集成的發(fā)展歷程示意圖 總共六層器件垂直堆疊,整體厚度不到2微米,為了驗(yàn)證3D異質(zhì)集成的器件性能,研究者利用AI處理器進(jìn)行了DNA測序計算,憶阻器顯示數(shù)值與軟件模擬結(jié)果相匹配,顯示出良好的并行計算能力。此外,隨著3D集成層數(shù)量的增加,每層陣列的電壓降減小,減少了冗余數(shù)據(jù)傳輸,可以降低器件功耗,縮短預(yù)測的處理時間和延遲。

基于2D材料的3D單片異質(zhì)集成策略為下一代芯片制備鋪平了道路。中國科學(xué)院大學(xué)胡偉達(dá)研究員在同期Nature Materials 雜志上評論道,“非馮?諾依曼體系結(jié)構(gòu)與3D單片異質(zhì)集成的融合,極大地降低了處理時間延遲和功耗……AI處理器具有處理更快速、電壓降更低、單元面積更小等優(yōu)勢,這得益于垂直集成技術(shù)”。Sang-Hoon Bae教授也表示,“你可以把芯片集成想象成建造一座房子,3D單片異質(zhì)集成有利于開發(fā)出更緊湊、更強(qiáng)大和更節(jié)能的設(shè)備,重塑整個微電子和計算行業(yè),從自動駕駛汽車到醫(yī)療診斷和數(shù)據(jù)中心,該技術(shù)的應(yīng)用可能性是無限的”。

審核編輯:黃飛

-

電子器件

+關(guān)注

關(guān)注

2文章

598瀏覽量

32486 -

AI

+關(guān)注

關(guān)注

87文章

33236瀏覽量

273492 -

AI處理器

+關(guān)注

關(guān)注

0文章

92瀏覽量

9662 -

異質(zhì)集成

+關(guān)注

關(guān)注

1文章

6瀏覽量

754

原文標(biāo)題:Nature子刊:三維單片異構(gòu)集成,可執(zhí)行AI任務(wù)

文章出處:【微信號:DT-Semiconductor,微信公眾號:DT半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

世界級專家為你解讀:晶圓級三維系統(tǒng)集成技術(shù)

三維曲線加速度

三維逆向工程的成果及應(yīng)用案例

三維快速建模技術(shù)與三維掃描建模的應(yīng)用

廣西掃描服務(wù)三維檢測三維掃描儀

三維設(shè)計應(yīng)用案例

基于LTCC技術(shù)的三維集成微波組件

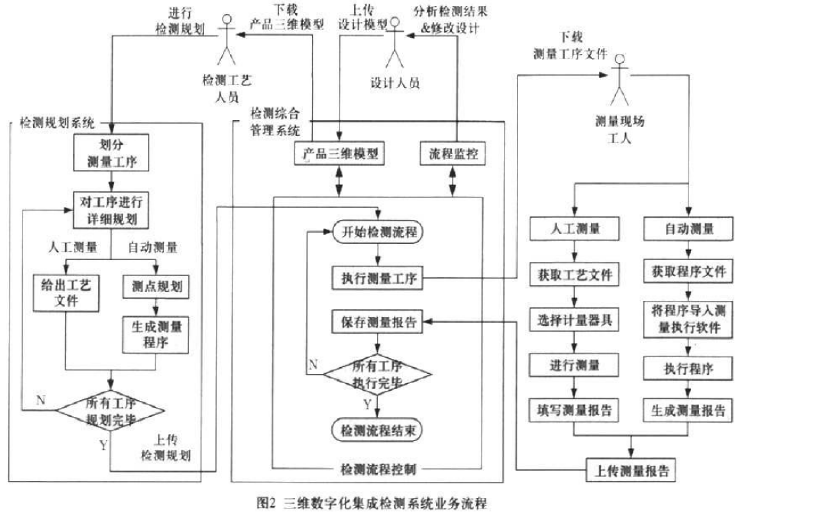

三維數(shù)字化集成檢測系統(tǒng)實(shí)現(xiàn)關(guān)鍵技術(shù)分析

慣性微系統(tǒng)正在朝著三維封裝集成架構(gòu)發(fā)展

蔡堅:封裝技術(shù)正在經(jīng)歷系統(tǒng)級封裝與三維集成的發(fā)展階段

智慧城市_實(shí)景三維|物業(yè)樓三維掃描案例分享_泰來三維

泰來三維|文物三維掃描,文物三維模型怎樣制作

淺談三維單片異構(gòu)集成的發(fā)展歷程

淺談三維單片異構(gòu)集成的發(fā)展歷程

評論