引言:上一篇文章我們簡單介紹了AD9129的基礎知識,包括芯片的重要特性,外部接口相關的信號特性等。本篇我們重點介紹下項目中FPGA與AD9129互聯的原理圖設計,包括LVDS IO接口設計、時鐘電路以、供電設計以及PCB設計。

LVDS數據接口設計

當AD9129作為FPGA外設進行互聯設計時,需要考慮AD9129芯片IO接口電平,DAC芯片與K7芯片互聯的IO Bank。

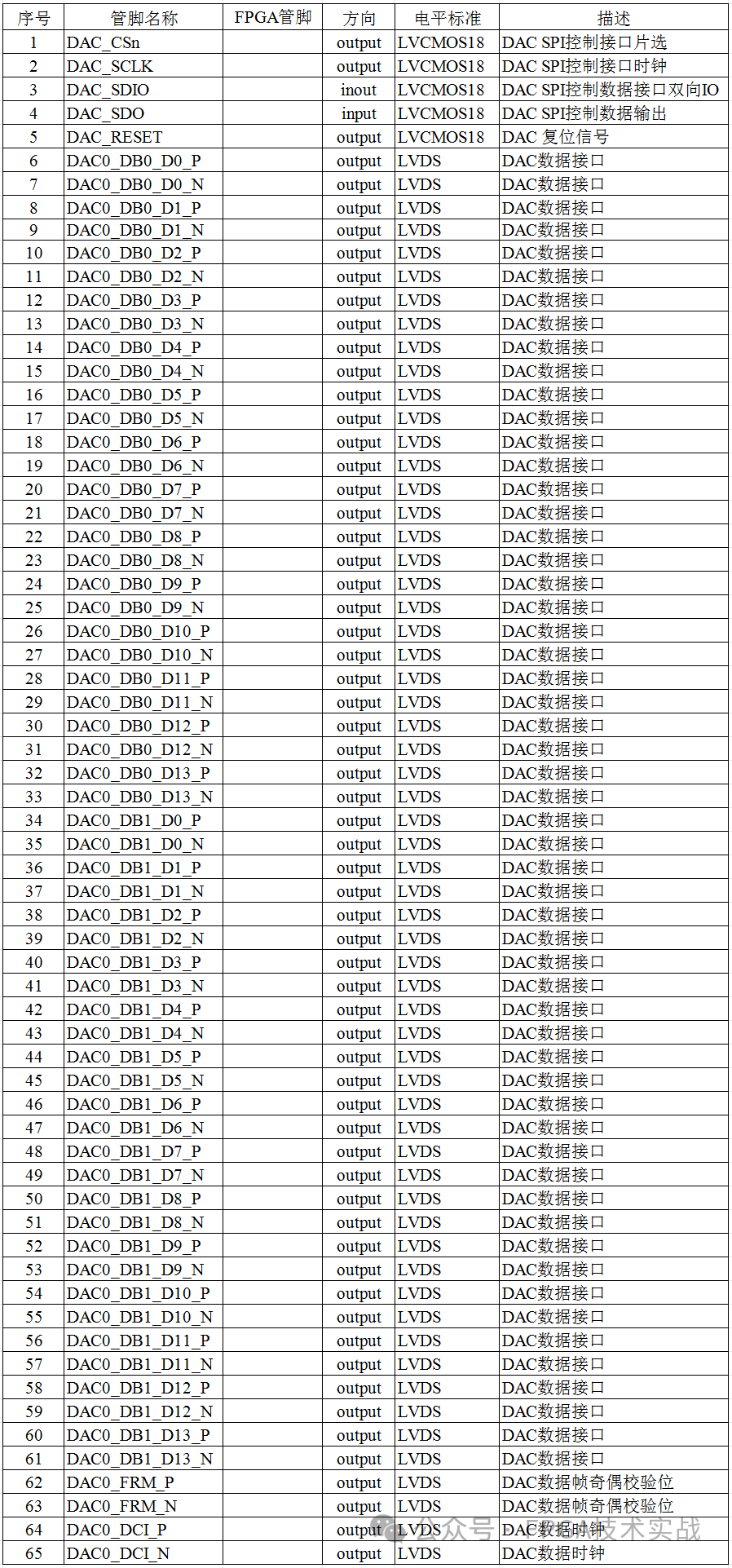

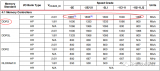

AD9129與FPGA互聯接口特性如下表所示。

表1 AD9129接口特性

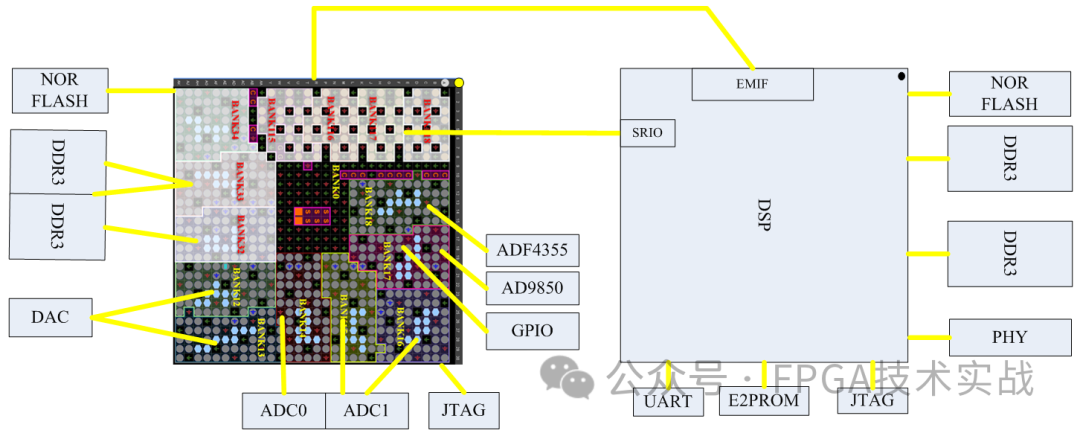

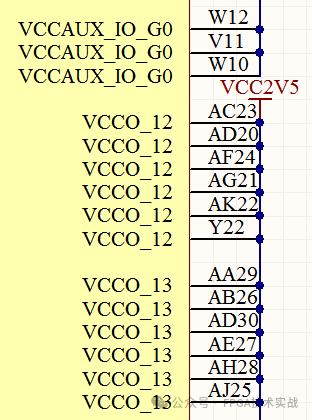

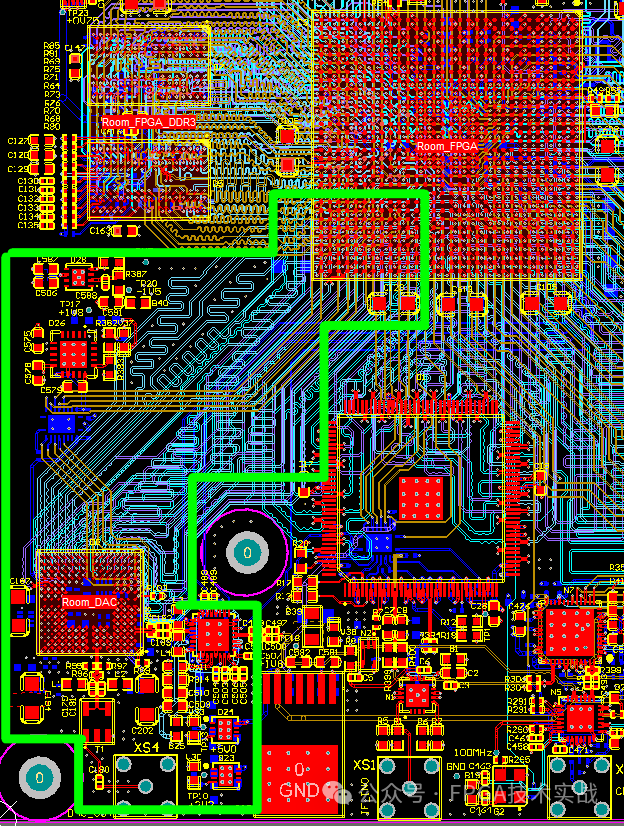

根據FPGA其他外設整體布局規劃,DAC分配至FPGA Bank12和Bank13上,如下圖所示。

圖1:FPGA IO Bank規劃

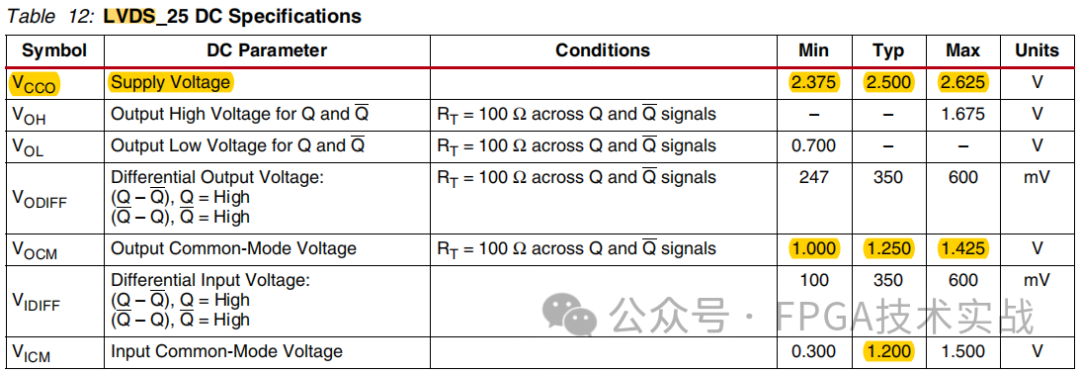

由于Bank12和Bank13為HR IO Bank,FPGA LVDS接口電平標準為LVDS_25,特性如下圖所示,因此這兩個Bank VCCO采用2.5V供電。

表2 LVDS_25 DC特性

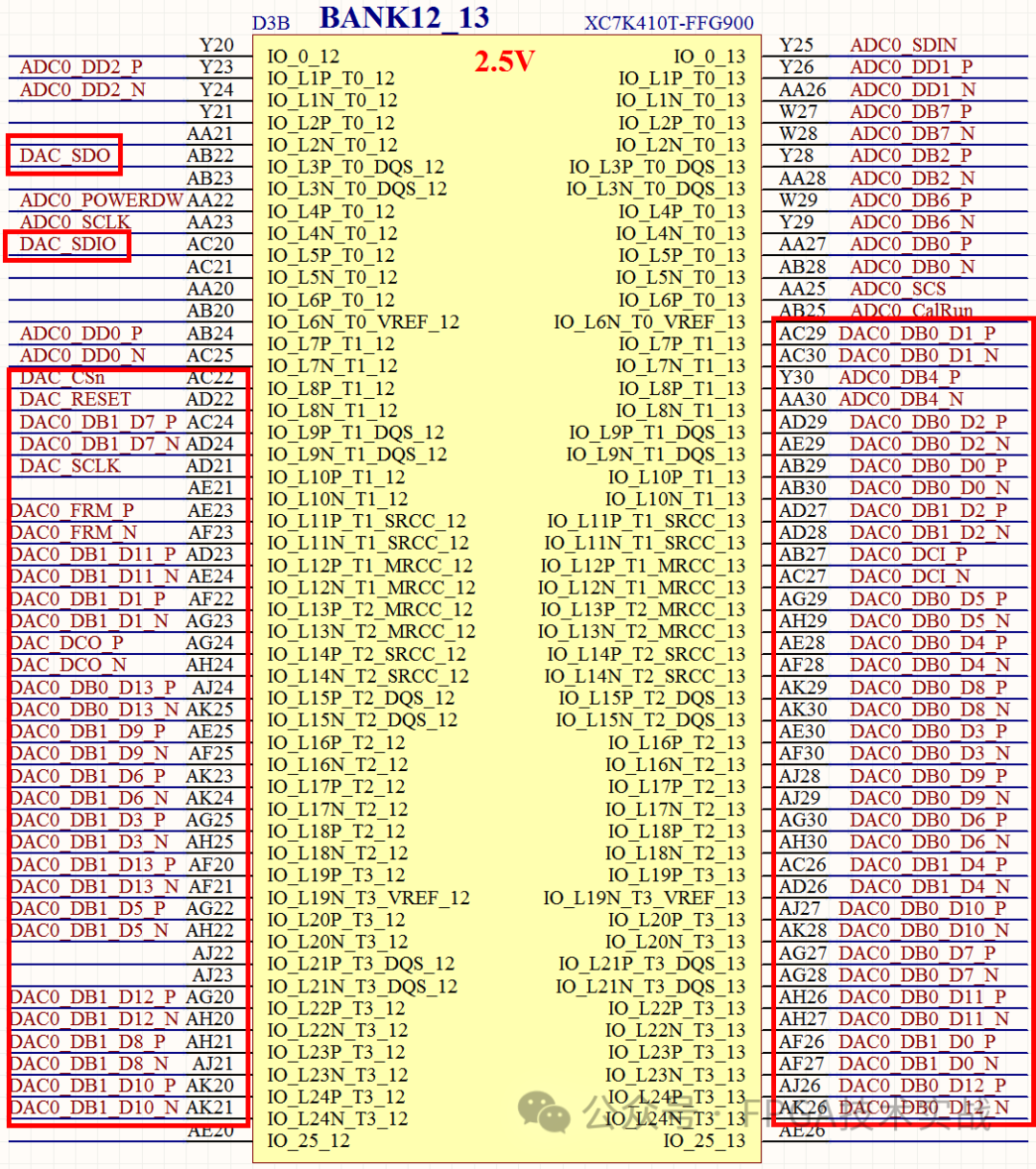

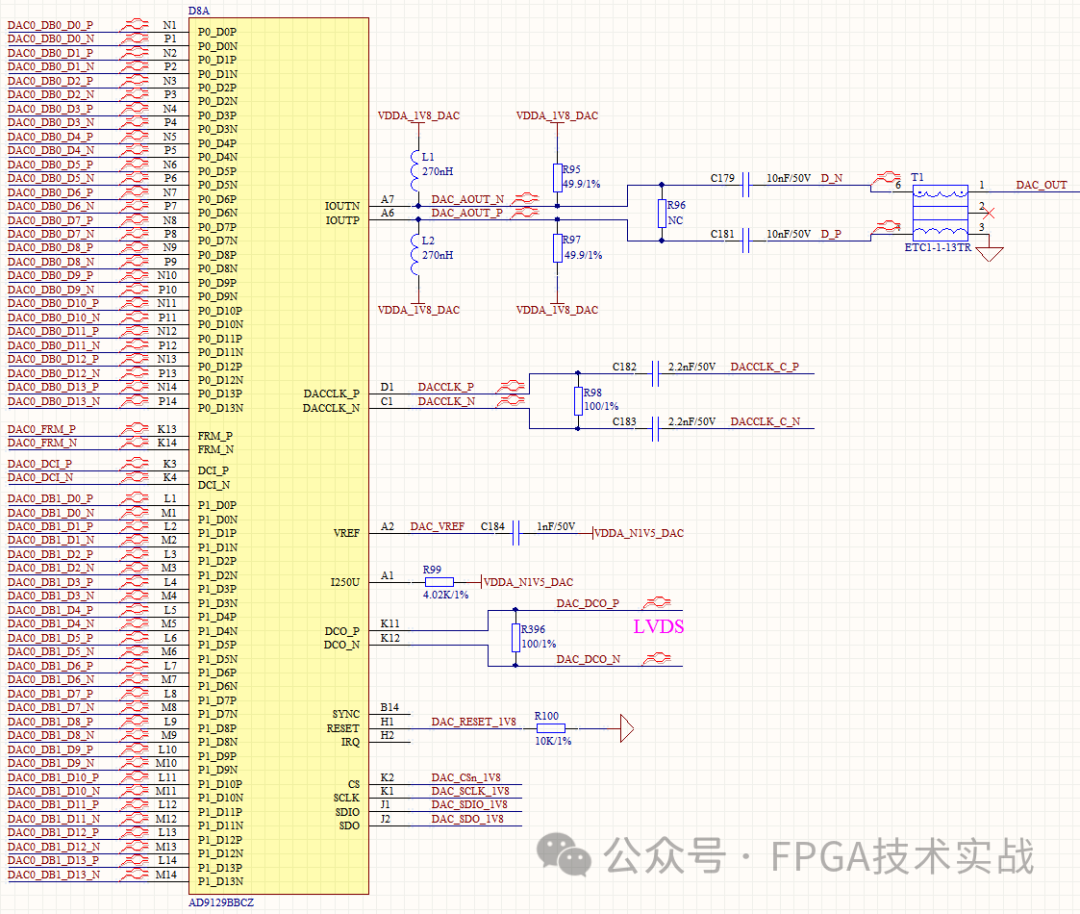

DAC LVDS數據及控制接口設計如下圖所示。

圖2:FPGA與AD9129 LVDS IO分配電路

圖3:AD9129外圍電路設計

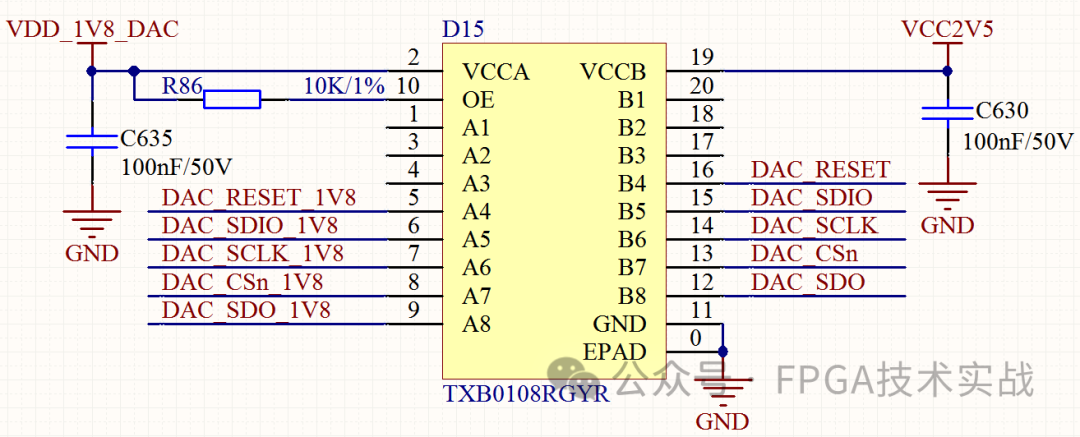

另外,考慮到DAC控制接口電平為LVCMOS18電平標準,當DAC控制接口與FPGA 2.5V VCCO IO互聯時,需要使用電平轉換芯片,以滿足IO Bank電氣兼容要求。詳細原理圖設計如下圖。

圖4:FPGA IO Bank供電 DAC SPI電平轉換電路

2.時鐘電路設計

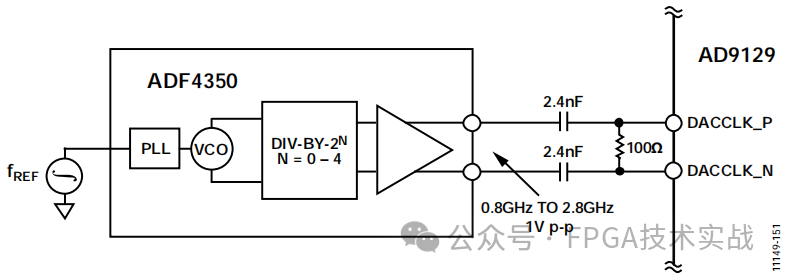

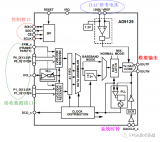

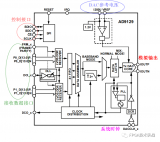

手冊推薦的典型時鐘供電電路如下圖所示。

圖5:AD9129典型時鐘電路

DACCLK_x輸入的峰峰值電壓為0.25~2V,典型值為1V,共模電壓為1.25V。DACCLK_x輸入時鐘頻率范圍為1.4G~2.85GHz。

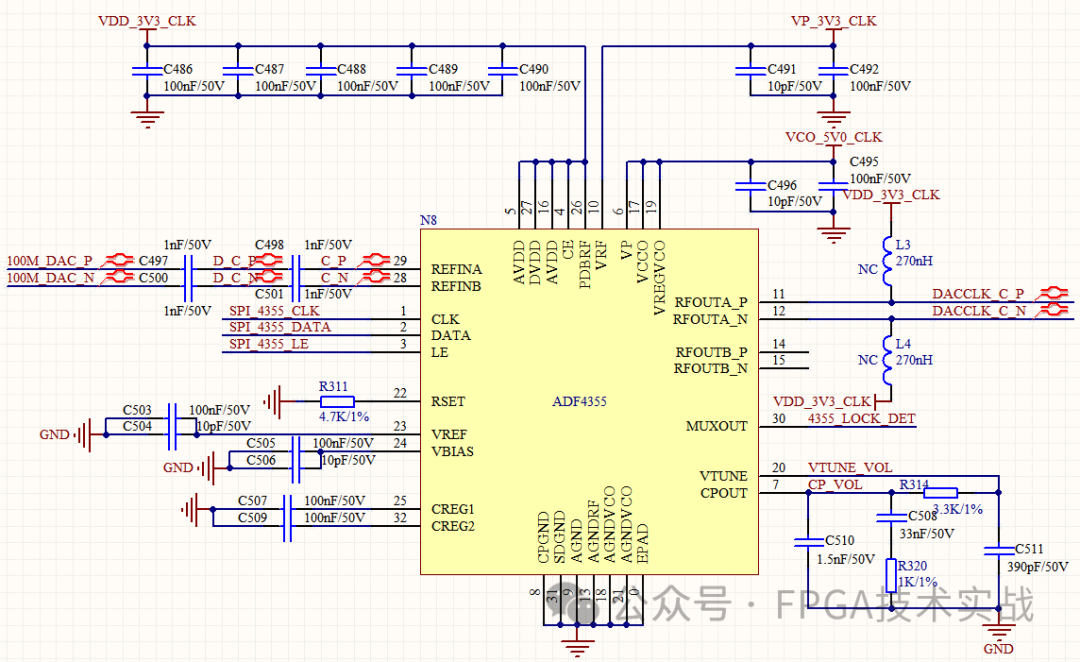

本設計選用ADI ADF4355為AD9129提供時鐘,原理圖如下圖。

圖6:時鐘電路設計

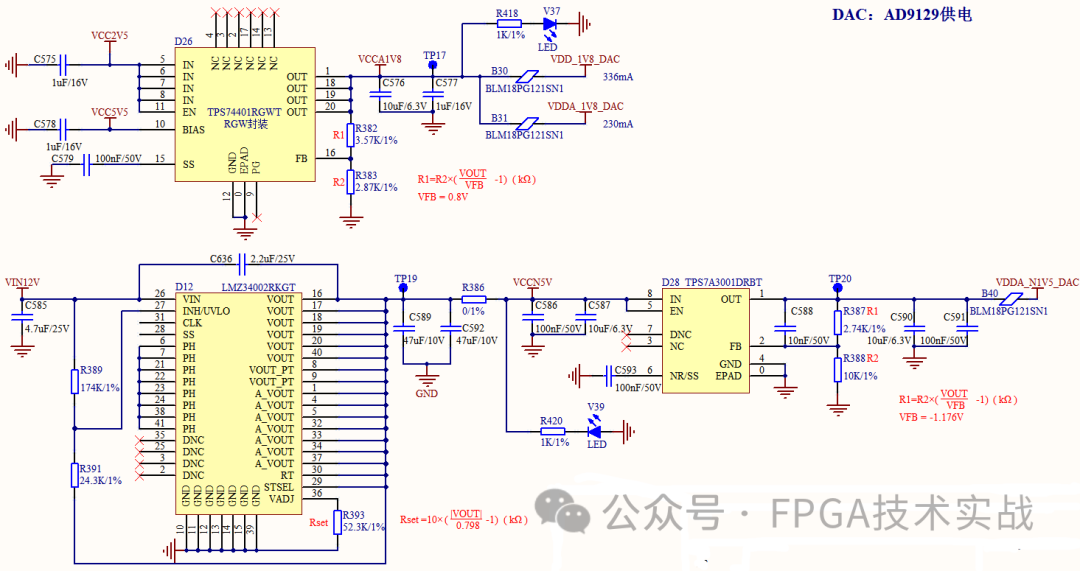

3.電源設計AD9129電源分為模擬電源和數字電源,整個芯片最大功耗在1.1W左右,最大功耗工作時,需要考慮芯片散熱問題。

模擬電源VSSA=-1.5V,Imax=54mA;

模擬電源VDDA=1.8V,Imax=230mA;

數字電源VDD=1.8V,Imax=336mA。

圖7:AD9129供電電路

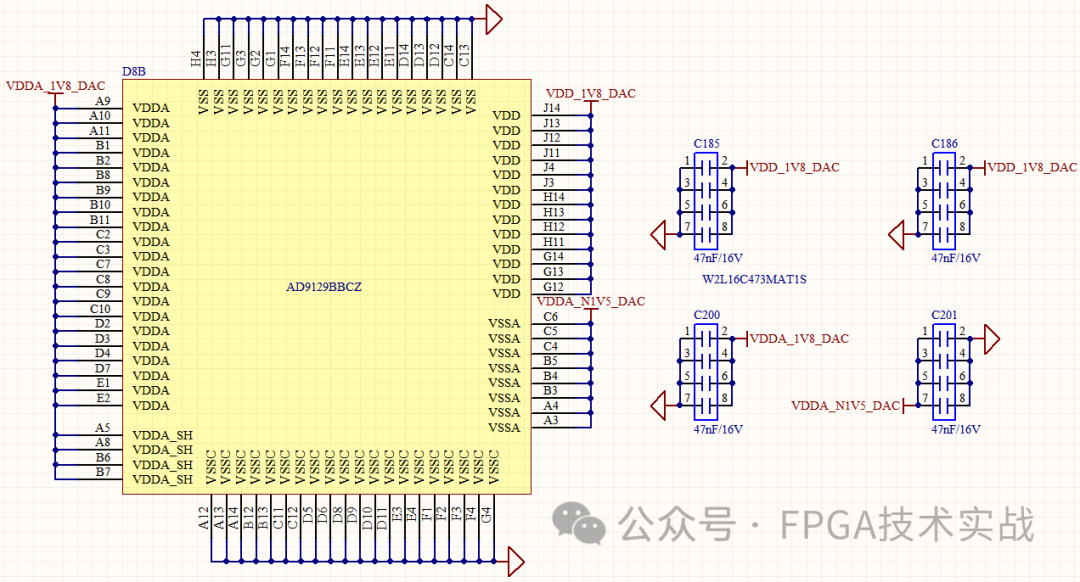

圖8:AD9129濾波電路

4. AD9129 PCB設計

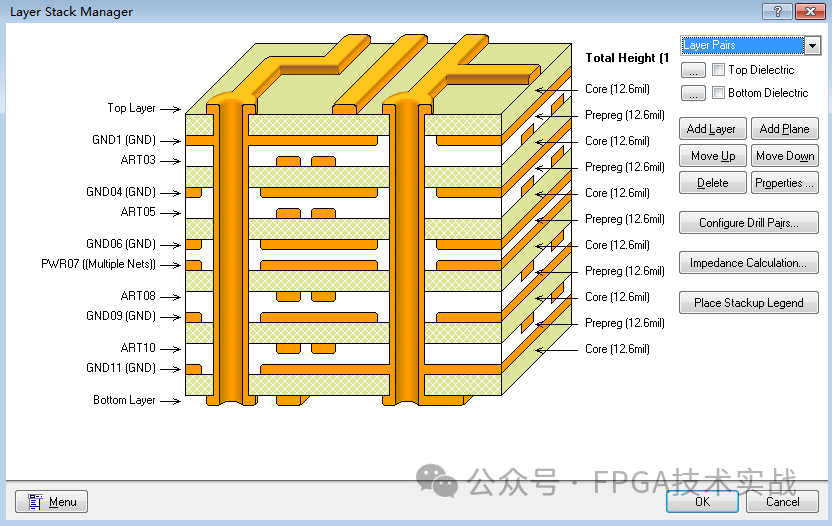

電路板采用12層PCB設計,層疊設計如下圖所示。

圖9:PCB層疊設計

AD9129電路設計完成的PCB版圖如下圖所示。

圖10:AD9129 PCB設計(圖中綠色范圍內)

5. 小結

本篇我們重點介紹了FPGA與AD9129互聯的原理圖設計,包括LVDS IO接口設計、時鐘電路以、供電設計以及PCB設計。下一篇再對AD9129接口SPI接。

-

FPGA

+關注

關注

1644文章

21989瀏覽量

615240 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124574 -

dac

+關注

關注

43文章

2388瀏覽量

193186

原文標題:基于Xilinx K7-410T的高速DAC之AD9129開發筆記(二)

文章出處:【微信號:FPGA技術實戰,微信公眾號:FPGA技術實戰】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ADI發布兩款RF(射頻)DAC AD9129和AD9119

求助,關于AD9129的相關問題求解

Modbus庫開發筆記之十一:關于Modbus協議棧開發的說明

AD9129偶發性底噪過高,請問怎么解決?

壇友經驗分享之STM32的USB程序開發筆記

AD9129偶發性底噪過高怎么解決?

AD9129評估板、DAC-FMC插入器和Xilinx ML-605參考設計

基于Xilinx K7-410T的高速DAC之AD9129開發筆記

基于Xilinx K7-410T的高速DAC之AD9129開發筆記(一)

基于Xilinx K7-410T的高速DAC之AD9129開發筆記(二)

基于Xilinx K7-410T的高速DAC之AD9129開發筆記(二)

評論