FPGA算法是指在FPGA(現場可編程門陣列)上實現的算法。FPGA是一種可重構的硬件設備,可以通過配置和編程實現各種不同的功能和算法,而不需要進行硬件電路的修改。

FPGA算法可以包括各種不同的計算和處理任務,例如數字信號處理(DSP)、圖像處理、機器學習、通信協議處理等。FPGA的特點使得它非常適合實現需要高度并行計算和低延遲的算法。

實現FPGA算法的過程通常涉及以下幾個方面:

1. 硬件描述語言(HDL)編寫:使用硬件描述語言(如VHDL或Verilog)來描述算法的硬件結構和計算邏輯。

2. 綜合和優化:使用綜合工具將HDL代碼轉換為FPGA的可編程邏輯塊和數字信號處理塊。通過優化和資源利用率的考慮,提高算法的性能和效率。

3. 約束與布局:應用約束以滿足時序、時鐘頻率和信號完整性的要求,并使用布局工具進行物理布局以最小化信號傳輸的路徑。

4. 下載與調試:將設計下載到FPGA設備中,利用開發板支持工具進行功能驗證和性能調試。

FPGA算法的優點在于它們可以提供高度的定制化和靈活性,使得算法可以根據實際需求進行優化和調整。此外,FPGA還可以實現硬件加速,提供比傳統處理器更高的計算性能和吞吐量。因此,FPGA算法在許多領域中被廣泛應用,包括嵌入式系統、高性能計算和實時信號處理等。

怎么用FPGA做算法

使用FPGA(現場可編程門陣列)來實現算法是一種常見的方法,它可以提供高效的硬件加速和靈活的算法設計。下面是一般的步驟來用FPGA實現算法:

1. 算法設計與驗證:首先,你需要根據你的需求來設計算法。這包括確定輸入和輸出的數據格式、算法的處理步驟和計算流程等。你還可以使用軟件工具如MATLAB或Python等進行算法驗證,以確保其正確性和效果。

2. 硬件描述語言(HDL)編寫:使用硬件描述語言如VHDL或Verilog,將算法轉換成可在FPGA上實現的硬件描述。通過將算法進行邏輯門級的建模,你可以描述算法的功能和計算結構。

3. 綜合和優化:使用綜合工具,將HDL代碼轉換為對應 FPGA 的可編程邏輯塊(PL)和數字信號處理(DSP)塊。在綜合期間,你可以選擇各種優化選項,以提高資源利用率和性能。

4. 約束與布局:在 FPGA 上實現算法時,你需要考慮電路的物理限制。為了確保正確的時序和信號完整性,你需要應用各種約束,如時鐘頻率、I/O 路由和時序調整等。布局工具可以幫助你對設計進行布局,以使信號傳輸的路徑最短。

5. 時序分析與時序約束:在算法實現的過程中,你需要進行時序分析以驗證設計是否滿足時序要求。通過應用時序約束,你可以確保數據在正確的時間窗口內被傳輸和處理。

6. 下載與調試:當你完成 FPGA 的編程和配置后,將設計下載到 FPGA 開發板中。使用相應的開發板支持工具,你可以進行功能和性能的調試和驗證。

如何在FPGA上實現最大公約數算法

如何在FPGA上實現最大公約數算法,簡單介紹在FPGA上實現算法的基本思想。希望通過本文的介紹,讓各位朋友管中窺豹,初步形成如何用FPGA實現算法的基本概念。

輾轉相除法是求解兩個數的最大公約數最常用的方法,例如,計算a=1071和b=462的最大公約數的過程如下:

用1071除以462得到余數為147:1071 mod 462 = 147

用462除以147得到余數為21:462 mod 147 = 21

用147除以21得到余數為0:147 mod 21 = 0

此時余數為0,所以1071和462的最大公約數為21。

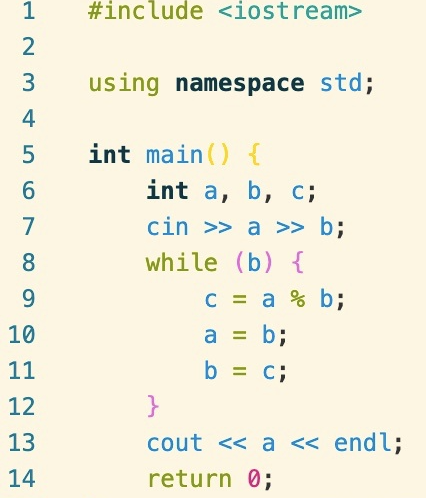

下圖是該過程的C++實現,輸入a和b,當b不為0時,不斷進行上述過程直到b為0,此時a為最大公約數。各位同學有興趣可以自行仿真上述代碼并通過單步調試觀察中間過程。

輾轉相除法求最大公約數的實現

在驗證算法的正確性后,可以進入算法實現階段。在FPGA上實現該算法主要有以下兩個步驟,首先需要優化算法,使算法更容易在硬件上實現。之后便是將算法模型轉化為RTL模型,并用硬件描述語言將模型描述出來。下面分別介紹這兩個步驟。

算法優化

在上述過程中,存在使用除法求余數的步驟。用硬件實現除法開銷較大,一般情況下會考慮將除法替換為其它運算操作。由于除法和減法之間存在等價關系,除法取余數本質上是不斷做減法直到被除數小于除數。在這里可以首先考慮將該使用減法實現求余操作,可以使用以下方式實現輾轉相除法:

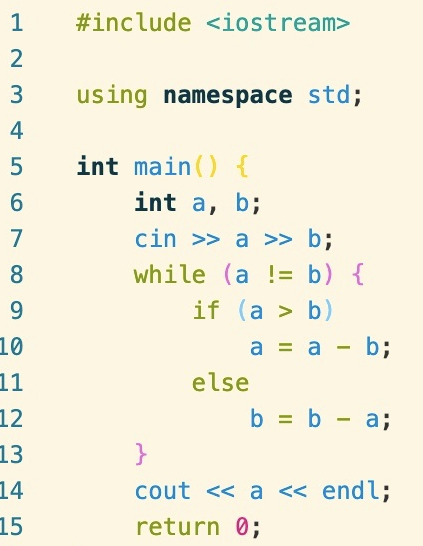

使用減法實現求余操作

當a大于b時不斷用a減去b,最后a的結果就是a mod b。當a小于b時則不斷用b減去a,最后a的結果就是a mod b。當a等于b時,此時無論是a mod b還是b mod a都為0,因此,此時a的值即為a與b的最大公約數。

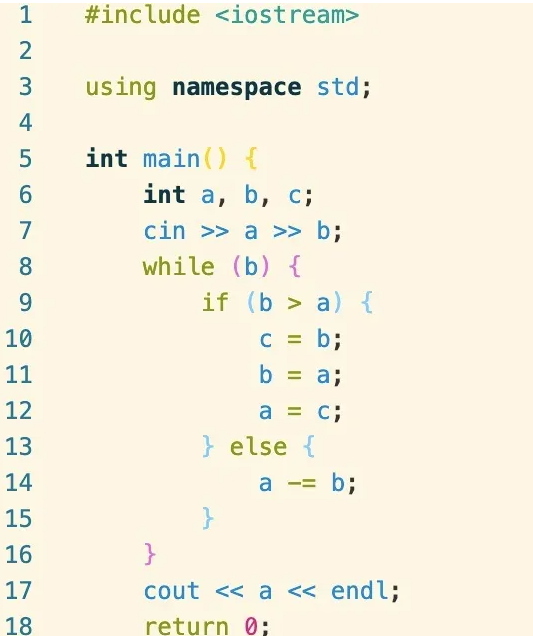

修改后的算法用減法實現取模操作,降低了硬件實現的開銷。但是取模操作始終是用大的數去減小的數得到余數,因此并不需要兩個減法器。如果規定a為a和b中的大數,每次取模運算都都求a mod b的值,則只需要使用到一個減法器。但這需要一個判斷的步驟,在a小于b時交換a和b的值,以維護a始終大于b這一關系。按照這種思路可以寫出如下代碼:

用于最終實現的版本

在以上代碼中,當b大于a時交換a和b,確保a永遠是兩個數中較大的那個數。否則不斷用a減去b得到a mod b,直到b為0,此時a的值即為a和b的最大公約數。至此,我們將算法優化為更易于硬件實現的版本:首先將取模使用減法實現,再減少減法器的數量,得到了用于最終實現的版本。

簡要總結一下,優化算法的目標有以下幾點:

1. 減少硬件開銷

2. 提高吞吐率,降低延遲

3. 降低系統功耗

而要實現這些目標主要可以考慮以下優化方向:

1. 將復雜的計算模塊用簡單的替換,比如使用減法算余數,但可能會帶來計算時間的增加

2. 通過量化等方法減少數據位寬

3. 提高系統的并行度,增加數據處理的并發性

4. 調整計算順序,優化計算過程以更符合硬件結構

在算法優化完成以后,下一步便是設計合適的硬件結構。

-

FPGA

+關注

關注

1639文章

21887瀏覽量

610871 -

算法

+關注

關注

23文章

4675瀏覽量

94194 -

可編程邏輯

+關注

關注

7文章

523瀏覽量

44441

原文標題:怎么用FPGA做算法 如何在FPGA上實現最大公約數算法

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA上的圖像處理算法集成與優化

怎么用FPGA做算法 如何在FPGA上實現最大公約數算法

怎么用FPGA做算法 如何在FPGA上實現最大公約數算法

評論