審核編輯 黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

通信測試

+關注

關注

0文章

64瀏覽量

49799 -

PCIe

+關注

關注

16文章

1342瀏覽量

85183 -

5G

+關注

關注

1360文章

48816瀏覽量

573983 -

創龍科技

+關注

關注

2文章

132瀏覽量

8053 -

RK3566

+關注

關注

0文章

157瀏覽量

5726

發布評論請先 登錄

相關推薦

熱點推薦

【HZ-RK3568開發板免費體驗】合眾HZ-RK3568開發板測評

HZ-RK3568的內存是使用紫光的SCB12Q4G160 DDR4,讀寫速度測試命令如下:

讀速度測試:

# bw_mem 100M rd

寫速度

發表于 07-14 22:24

RK3568內置MCU開發介紹之一

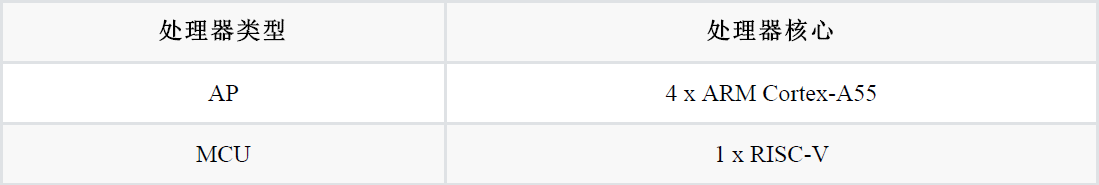

本文介紹RK3568內置的MCU的開發流程,首先介紹MCU程序的構建方法,然后介紹MCU核心與ARM CORTEX A55 AP核心之間的mailbox通信。 RK3568內置有4*cortex

迅為RK3568開發板使用手冊目錄了解

各個應用場合。

底板分為連接器與郵票孔兩種版本,雙路千兆以太網、SATA3.0、PCIE3.0、MIPI、HDM、MIPI、CAMERA、4G、5G等接口一應俱全.

發表于 08-01 11:08

3568F-FPGA案例開發手冊

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 15:35

3568F-MQTT通信協議案例

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 15:27

3568F-基于PTP的時鐘同步測試手冊

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 15:24

3568F-NPU開發案例

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 15:15

3568F-ARM+FPGA通信案例開發手冊

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 15:12

3568F-視頻開發案例

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 15:04

3568F-Linux-RT系統測試手冊

元器件數量占比,數據僅供參考)。

核心板內部RK3568J/RK3568B2與Logos-2通過PCIe 2.0、FSPI、I2C、GPIO連接,經過專業的PCB Layout和高低溫測試

發表于 07-25 14:41

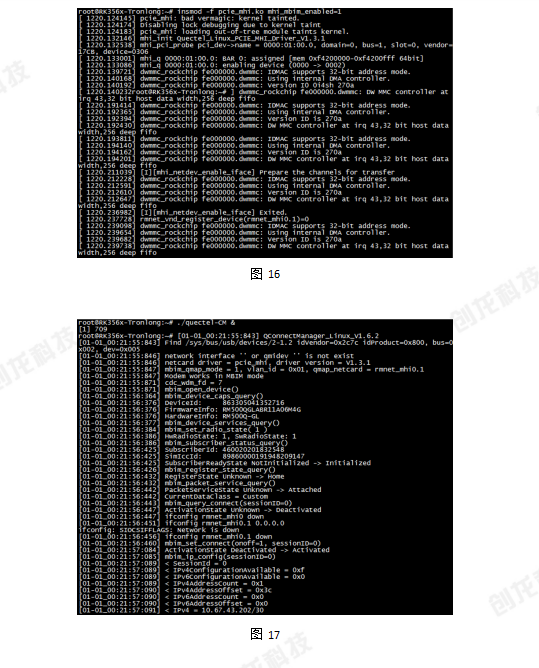

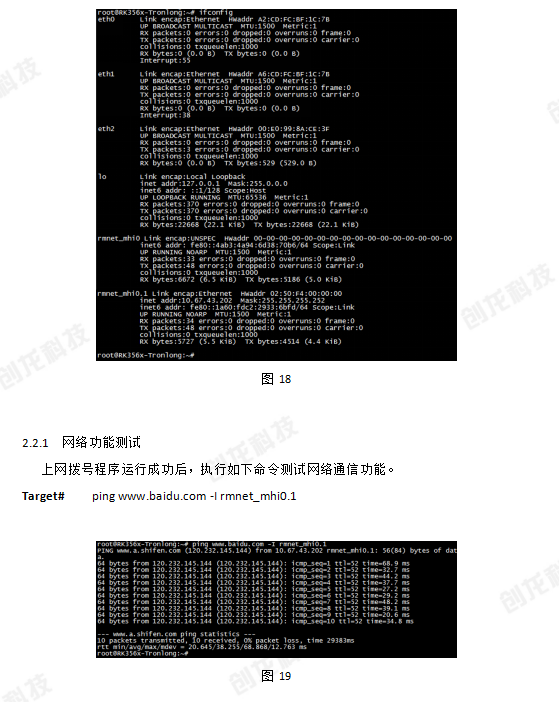

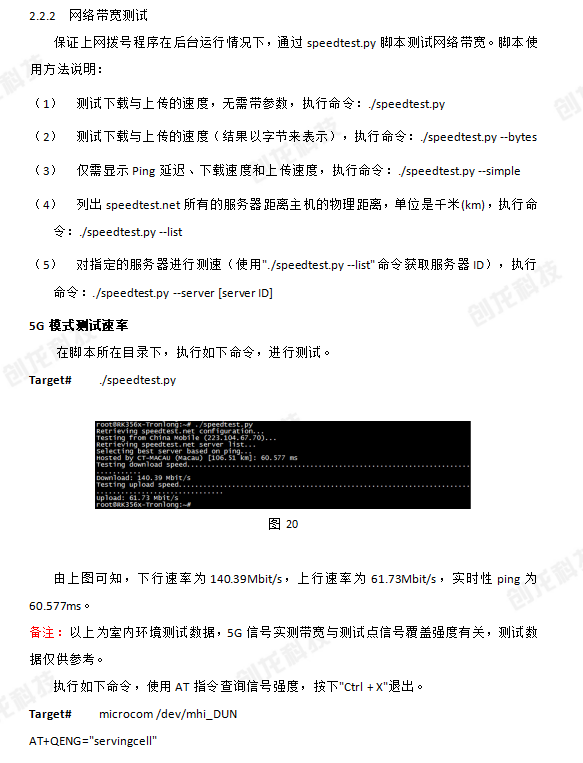

RK3568-PCIe 5G通信測試手冊

RK3568-PCIe 5G通信測試手冊

評論