來(lái)源:德思特測(cè)量測(cè)試德思特干貨|德思特ADC/DAC靜態(tài)參數(shù)測(cè)試系列(一)——什么是ADC轉(zhuǎn)換點(diǎn)?

歡迎關(guān)注虹科,為您提供最新資訊!

#ADC #DAC #信號(hào)處理

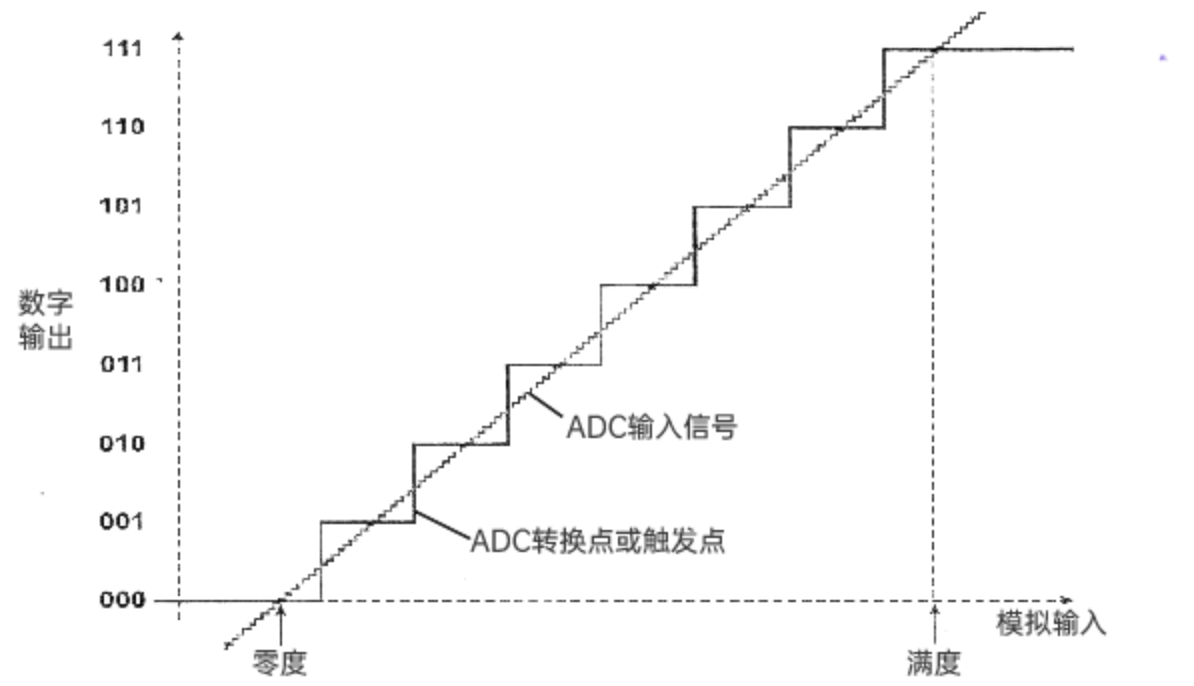

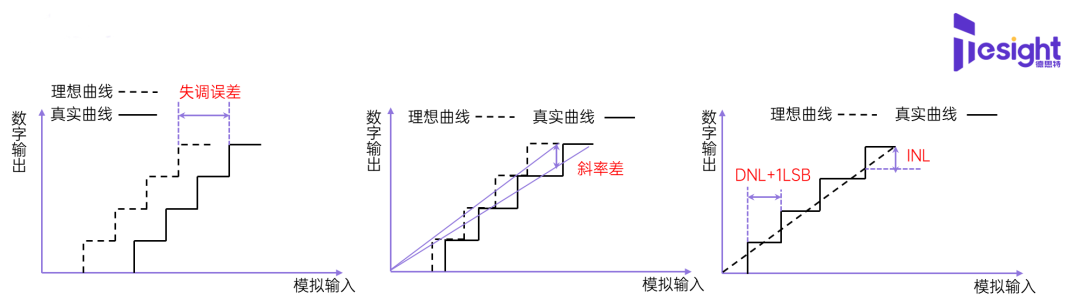

在現(xiàn)代電子系統(tǒng)設(shè)計(jì)與高速通信、信號(hào)處理、雷達(dá)探測(cè)、醫(yī)療成像以及各種工業(yè)自動(dòng)化應(yīng)用中,模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)扮演著至關(guān)重要的角色。ADC負(fù)責(zé)將模擬信號(hào)精確且高效地轉(zhuǎn)換為數(shù)字信號(hào),以便于進(jìn)行數(shù)字信號(hào)處理和數(shù)據(jù)傳輸;而DAC則執(zhí)行相反的功能,它將數(shù)字?jǐn)?shù)據(jù)流還原為高質(zhì)量的模擬信號(hào),以供實(shí)際設(shè)備或系統(tǒng)使用。

隨著技術(shù)的不斷進(jìn)步,尤其是對(duì)于5G通信、航空航天及國(guó)防等領(lǐng)域的嚴(yán)苛要求,高速、高精度、高分辨率以及大動(dòng)態(tài)范圍的ADC和DAC變得越來(lái)越重要。為了深入探究這些關(guān)鍵器件的基礎(chǔ)性能指標(biāo),德思特將引領(lǐng)您走進(jìn)ADC和DAC的靜態(tài)參數(shù)測(cè)試世界。本篇文章將為您介紹ADC中的一個(gè)關(guān)鍵概念——轉(zhuǎn)換點(diǎn)。

介紹

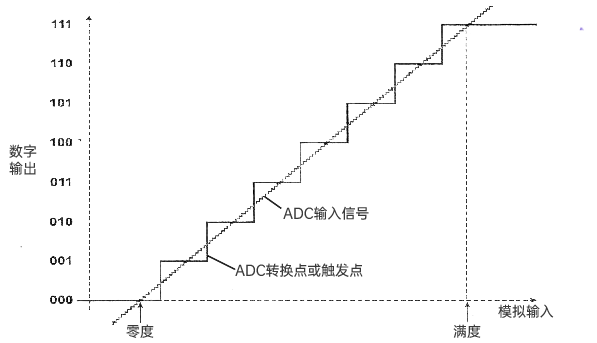

A/D轉(zhuǎn)換器的線性參數(shù)計(jì)算(INLE、DNLE等)基于器件的轉(zhuǎn)變點(diǎn)(或跳變點(diǎn))。為了確定ADC的轉(zhuǎn)變點(diǎn),應(yīng)將具有足夠步長(zhǎng)的模擬斜坡表征器件的吸納后輸入。根據(jù)測(cè)量的代碼可以確定轉(zhuǎn)變點(diǎn)。

德思特ADC測(cè)試系統(tǒng)TS-ATX7006和軟件TS-ATView7006有兩種確定跳變點(diǎn)的方法:

●跳變點(diǎn)搜索方法:算法“搜索”跳變點(diǎn)。考慮測(cè)量代碼在結(jié)果數(shù)組中的位置。

●代碼排序方法:代碼在結(jié)果數(shù)組中出現(xiàn)的次數(shù)是LSB步長(zhǎng)的度量。

跳變點(diǎn)搜索法

搜索從代碼x到代碼x+1(x -> x+1)的跳變點(diǎn),首先搜索數(shù)據(jù)數(shù)組中代碼x的第一次出現(xiàn)以及數(shù)據(jù)數(shù)組中代碼x+1的最后一次出現(xiàn),這就是跳變點(diǎn)的搜索數(shù)組。

代碼x和小于代碼x的出現(xiàn)次數(shù)均計(jì)入該區(qū)域。跳變點(diǎn)位于首次找到代碼x加上該計(jì)數(shù)器值(在該區(qū)域中找到代碼x及更少代碼的次數(shù))的位置。

開(kāi)始和結(jié)束時(shí)丟失的代碼將通過(guò)理想的轉(zhuǎn)換器步驟 (DNLE=0) 進(jìn)行推斷,并以第一個(gè)找到的跳變點(diǎn)作為參考。最后,跳變點(diǎn)是從最后找到的跳變點(diǎn)推斷出來(lái)的。所有其他缺失代碼都會(huì)導(dǎo)致 DNLE為-1:跳變點(diǎn)位于與其前一個(gè)跳變點(diǎn)相同的位置。

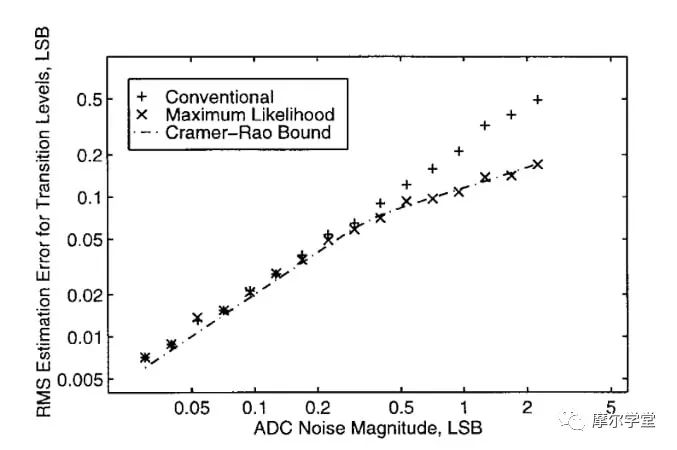

噪聲或測(cè)量分辨率不足可能導(dǎo)致DNLE小于1 LSB。

舉例說(shuō)明

無(wú)噪聲

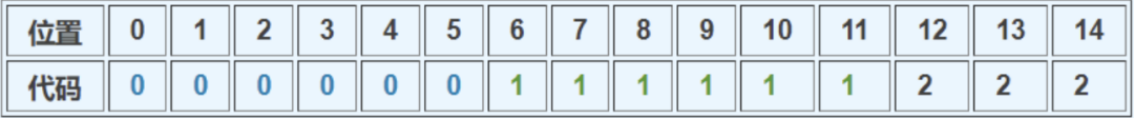

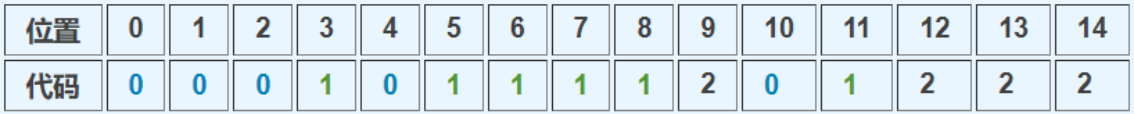

捕獲的數(shù)字?jǐn)?shù)據(jù)陣列:

跳變點(diǎn)0→1:

搜索區(qū)域:位置0-11。

計(jì)數(shù):6

跳變點(diǎn)位于位置5至6。跳變點(diǎn)電壓為:

Vtrp=Vstart+count*Vstep-1/2Vstep

其中:

Vstart=提供的斜坡的起始電壓。

startposition=首次找到代碼的位置,此處為位置0。

count=找到代碼0的次數(shù)

Vstep=提供的斜坡的電壓步長(zhǎng)。

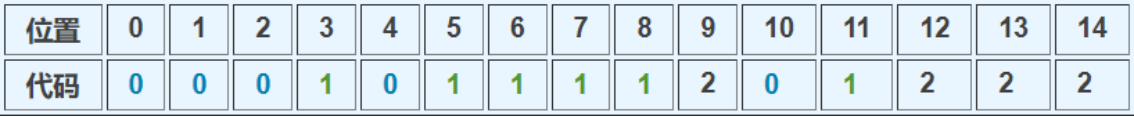

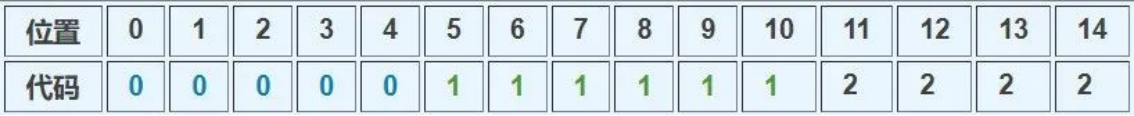

帶有噪聲

捕獲的數(shù)字?jǐn)?shù)據(jù)陣列:

跳變點(diǎn)0→1:

搜索區(qū)域:位置0-11。

計(jì)數(shù):5

跳變點(diǎn)位于位置4至5。

跳變點(diǎn)1→2:

搜索區(qū)域:位置3-14。

計(jì)數(shù):8(6次代碼1+2次代碼0)

跳變點(diǎn)位于位置10至11。

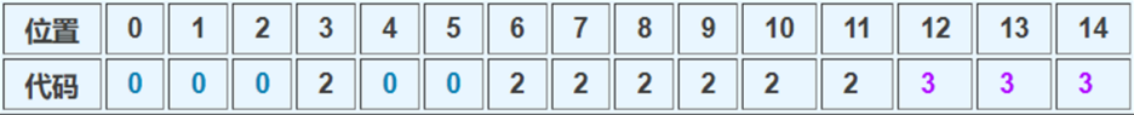

丟失代碼

捕獲的數(shù)字?jǐn)?shù)據(jù)陣列:

跳變點(diǎn)0→1和0→2:

搜索區(qū)域:位置0-11。

計(jì)數(shù):5

兩個(gè)跳變點(diǎn)均位于位置4至5。

排序代碼方法

所有代碼都在數(shù)據(jù)數(shù)組中排序。排序后,數(shù)據(jù)數(shù)組從所有測(cè)量代碼0開(kāi)始,然后是代碼1,依此類推。因此,測(cè)量數(shù)據(jù)中代碼的位置不相關(guān)。使用排序代碼方法不會(huì)發(fā)生小于-1的DNL錯(cuò)誤。

示例

排序前捕獲的數(shù)字?jǐn)?shù)據(jù)數(shù)組:

排序后捕獲的數(shù)字?jǐn)?shù)據(jù)數(shù)組:

審核編輯 黃宇

-

adc

+關(guān)注

關(guān)注

99文章

6646瀏覽量

548352 -

dac

+關(guān)注

關(guān)注

43文章

2380瀏覽量

193096 -

信號(hào)處理

+關(guān)注

關(guān)注

48文章

1055瀏覽量

103930

發(fā)布評(píng)論請(qǐng)先 登錄

如何簡(jiǎn)化測(cè)試系統(tǒng)架構(gòu)?德思特ADC DAC測(cè)試系統(tǒng)開(kāi)箱揭秘!#ADC #DAC #數(shù)模轉(zhuǎn)換器

高速 ADC/DAC 測(cè)試原理及測(cè)試方法

如何實(shí)現(xiàn)對(duì)ADC/DAC的靜態(tài)和動(dòng)態(tài)特性的測(cè)試?

ADC和DAC的靜態(tài)傳輸函數(shù)和DC誤差

ADC/DAC,ADC/DAC的原理是什么?

ADC芯片參數(shù)測(cè)試技術(shù)解析

高速ADC、DAC測(cè)試原理及測(cè)試方法

blog高速ADC、DAC測(cè)試原理及測(cè)試方法

并行接口的ADC、DAC的測(cè)試方法

德思特分享丨一文帶你了解ADC測(cè)試參數(shù)有哪些?

ADC靜態(tài)測(cè)試全流程:以斜坡測(cè)試為例(二)

SPEA—ADC與DAC測(cè)試簡(jiǎn)介

技術(shù)干貨 德思特ADC/DAC靜態(tài)參數(shù)分析系列(一)——什么是ADC轉(zhuǎn)換點(diǎn)?

德思特ADC/DAC靜態(tài)參數(shù)測(cè)試系列(一)——什么是ADC轉(zhuǎn)換點(diǎn)?

德思特ADC/DAC靜態(tài)參數(shù)測(cè)試系列(一)——什么是ADC轉(zhuǎn)換點(diǎn)?

評(píng)論