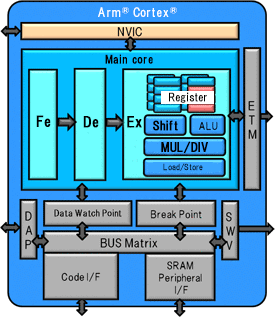

經(jīng)過(guò)前一期的芝識(shí)課堂,我們了解了東芝MCU產(chǎn)品所基于Arm Cortex-M3內(nèi)核的基本結(jié)構(gòu)和寄存器分配的細(xì)節(jié)。大家一定迫不及待地想知道Arm Cortex-M3內(nèi)核的操作模式又有哪些技巧吧?今天芝子就帶大家詳細(xì)學(xué)習(xí)一下吧!

Arm Cortex-M3有兩個(gè)特權(quán)(特權(quán)/非特權(quán))和兩種操作模式(線程/處理者)。對(duì)于嵌入式使用,可以選擇只有特權(quán)級(jí)別的基本配置或在特權(quán)和非特權(quán)之間切換的配置。在特權(quán)/非特權(quán)級(jí)別下,通過(guò)在分配給寄存器R13的主棧指針(MSP)與進(jìn)程棧指針(PSP)之間切換,堆棧區(qū)域可由操作系統(tǒng)內(nèi)核以及用戶例程等處理功能分離和管理。

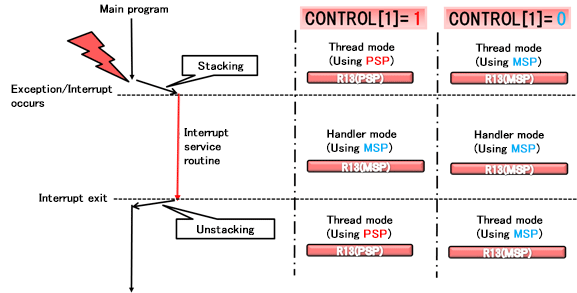

如果發(fā)生異常/中斷的程序,控制寄存器的狀態(tài)以及堆棧指針的切換情況是怎么樣的呢?如圖1所示,當(dāng)發(fā)生異常/中斷時(shí),使用中的堆棧會(huì)隨控制寄存器CONTROL的狀態(tài)而改變。以顯示主棧指針(MSP)和進(jìn)程棧指針(PSP)之間的切換狀態(tài)。

圖1 發(fā)生異常/中斷的程序時(shí)控制寄存器的狀態(tài)

以及堆棧指針的切換

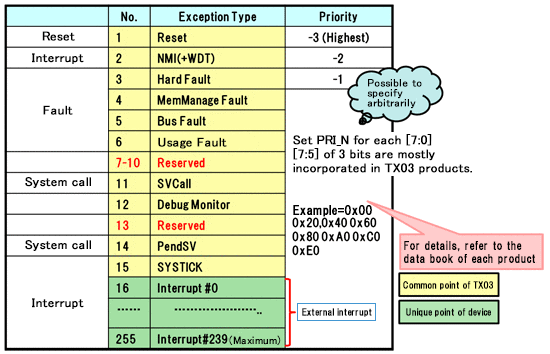

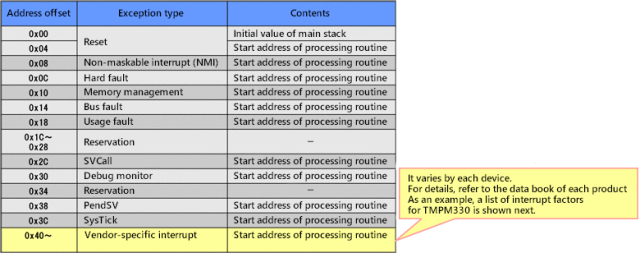

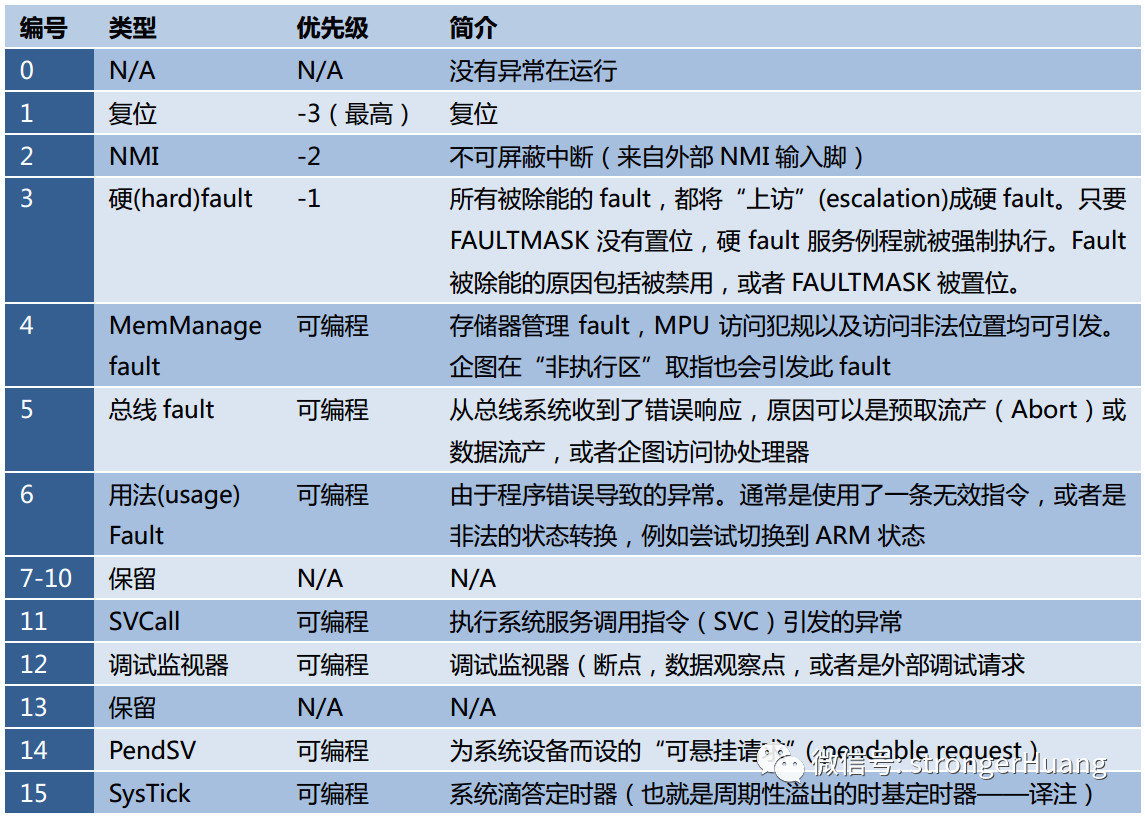

Arm Cortex-M3內(nèi)核的所有異常都在特權(quán)模式下運(yùn)行,且具有中斷特權(quán)并支持嵌套中斷,所有異常都集成在NVIC寄存器中。值得注意的是,因每個(gè)設(shè)備而異,部分設(shè)備中斷過(guò)程支持外部中斷。異常可通過(guò)復(fù)位、中斷、故障和系統(tǒng)調(diào)用執(zhí)行。異常類型和特權(quán)級(jí)別如圖2所示。

圖2 異常類型和特權(quán)級(jí)別

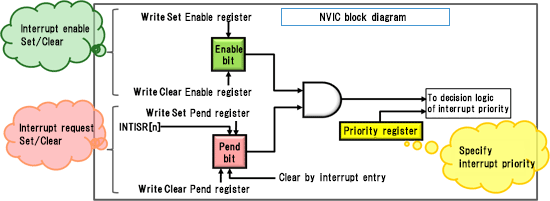

對(duì)于集成異常的NVIC控制寄存器,當(dāng)發(fā)生異常和中斷操作時(shí),它作為從主內(nèi)核到存儲(chǔ)器的設(shè)備被訪問(wèn),用于控制各中斷使能的設(shè)置與清除、控制各中斷請(qǐng)求的設(shè)置與清除(釋放保留)以及控制中斷的優(yōu)先級(jí)。

下面我們?cè)賻Т蠹伊私釴VIC塊的基本功能之一——外部中斷處理控制,將使能位和掛起位分配給每個(gè)外部中斷信號(hào),并配置控制寄存器。控制寄存器分為僅設(shè)置寄存器和僅清除寄存器。外部中斷的產(chǎn)生通過(guò)優(yōu)先級(jí)寄存器的信息來(lái)控制。該寄存器用于設(shè)置中斷優(yōu)先級(jí)以及使能位和掛起位的狀態(tài),如圖3。Arm Cortex-M3通過(guò)NVIC控制實(shí)現(xiàn)高速入棧/出棧處理,此外,如果中斷處理過(guò)程中同時(shí)發(fā)生中斷請(qǐng)求或發(fā)生高優(yōu)先級(jí)的中斷請(qǐng)求,則入棧/出棧處理的寄存器自動(dòng)保存將被忽略,從而改善處理時(shí)間。

圖3

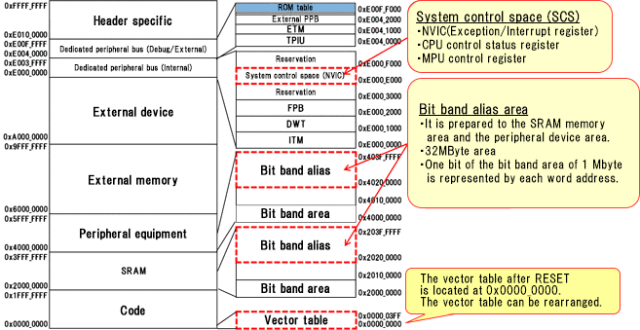

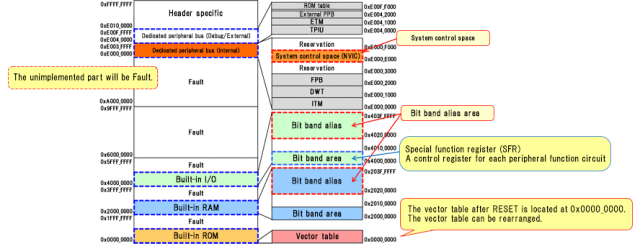

介紹完異常和中斷操作,我們?cè)賮?lái)看看Arm Cortex-M3規(guī)格的存儲(chǔ)器映射。圖4是Arm Cortex-M3規(guī)格的存儲(chǔ)器映射示意圖,可以清楚看到每個(gè)存儲(chǔ)器對(duì)應(yīng)的存儲(chǔ)功能。圖5則展示了這款MCU的存儲(chǔ)器映射細(xì)節(jié),從中可以看到相比于Arm Cortex-M3標(biāo)準(zhǔn)的規(guī)格,該芯片的部分存儲(chǔ)器映射進(jìn)行了深度優(yōu)化。

圖4

圖5

在CPU接收到外部中斷/異常時(shí),它會(huì)先查詢向量表,以查找到相應(yīng)的中斷服務(wù)程序地址。向量表是指中斷服務(wù)程序入口地址的偏移量與段基址,一個(gè)中斷向量占據(jù)4字節(jié)空間。各種異常的處理者(處理例程)的起始地址是分別設(shè)置的。當(dāng)異常或中斷事件發(fā)生時(shí),從地址開始獲取異常處理者。各種異常的向量表如圖6所示。

圖6

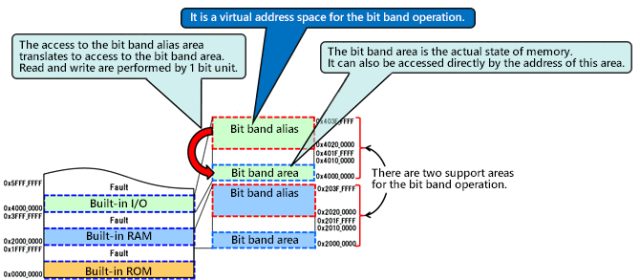

此外,關(guān)于位帶和位帶別名區(qū)的詳細(xì)信息如圖7所示。存儲(chǔ)器中的數(shù)據(jù)通過(guò)1位單元進(jìn)行有效運(yùn)算。1位單元通過(guò)將位帶區(qū)的數(shù)據(jù)加載或存儲(chǔ)到位帶別名區(qū)來(lái)訪問(wèn)這些數(shù)據(jù)。

那么位帶區(qū)數(shù)據(jù)和位帶別名區(qū)的地址如何分配?位帶別名區(qū)的地址以字為單位進(jìn)行分配(1個(gè)字=32位):位帶別名區(qū)的字地址bit0訪問(wèn)位帶區(qū)的每個(gè)位;位帶別名區(qū)的字地址的分配方式為,每個(gè)地址分配給位帶區(qū)的每個(gè)位。

圖7

今天的芝識(shí)課堂,我們深入探討了Arm Cortex-M3內(nèi)核的操作模式,并分析了存儲(chǔ)器映射的具體細(xì)節(jié)。接下來(lái)我們會(huì)一起進(jìn)入東芝MCU產(chǎn)品的外圍電路部分,學(xué)習(xí)如何針對(duì)不同應(yīng)用增加各種功能單元,從而助力低功耗高性能解決方案開發(fā)的,敬請(qǐng)期待!

審核編輯:劉清

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166422 -

Cortex-M3

+關(guān)注

關(guān)注

9文章

276瀏覽量

60119 -

NVIC

+關(guān)注

關(guān)注

0文章

36瀏覽量

11947 -

外部中斷

+關(guān)注

關(guān)注

1文章

133瀏覽量

16103 -

控制寄存器

+關(guān)注

關(guān)注

0文章

34瀏覽量

11617

原文標(biāo)題:芝識(shí)課堂——強(qiáng)大的Arm? Cortex?-M3內(nèi)核(下)

文章出處:【微信號(hào):toshiba_semicon,微信公眾號(hào):東芝半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Cortex‐M3內(nèi)核的知識(shí)點(diǎn)匯總,絕對(duì)實(shí)用

針對(duì)ARM Cortex M3平臺(tái)的代碼移植

特大好消息:ARM Cortex-M0/M3免收授權(quán)費(fèi)了

如何定制基于Cortex-M0/M3免費(fèi)內(nèi)核的自主SoC

如何定制基于Cortex-M0/M3免費(fèi)內(nèi)核的自主SoC | 直播報(bào)名(11.25)

ME32x系列是內(nèi)嵌ARM Cortex M0/M3核的32位微控制器

Cortex M3權(quán)威指南

使用FreeRTOS TM實(shí)時(shí)內(nèi)核ARM Cortex M3版

芝識(shí)課堂【TX03微控制器】—強(qiáng)大的Arm? Cortex?-M3內(nèi)核(上)

強(qiáng)大的Arm? Cortex?-M3內(nèi)核(下)

強(qiáng)大的Arm? Cortex?-M3內(nèi)核(下)

評(píng)論