noise shaping(NS) SAR ADC最近兩年的發(fā)展趨勢,對不同paper中的實現(xiàn)方式進行了分析并對其優(yōu)缺點進行概括。雖然noise shaping SAR ADC這一結構是在2012年才被提出來,但經歷這近十年的發(fā)展,其在論文中的實現(xiàn)方式也在不斷進步,受到了廣泛地研究,因此,下文著重介紹分析ISSCC 2020 和 ISSCC 2021發(fā)表的關于NS SAR ADC的paper。

首先,在具體談paper之前,先說說目前noise shaping SAR ADC的類型。按照NS的方式,即如何extract quantization noise和實現(xiàn)quantization noise的filtering,NS可分為CIFF(cascaded noise feedforward),EF(error feedback)以及兩者的hybrid。CIFF和EF的具體區(qū)別,這里就不做具體解釋了,有興趣的可以去看看'[1]J. Fredenburg and M. Flynn, “A 90MS/s 11MHz Bandwidth 62dB SNDR Noise-Shaping SAR ADC,” ISSCC, pp. 468–470, Feb. 2012.' 和 ‘[1]A S. Li, B. Qiao, M. Gandara, D.Z. Pan, N. Sun, A 13-ENOB second-order noise-shaping SAR ADC realizing optimized NTF zeros using the error-feedback structure. IEEE J. Solid-State Circuits 53(12), 3484–3496 (2018)’這兩篇paper,分別解釋了CIFF和EF的工作原理。而hybrid EF-CIFF的工作原理在我上一篇的日志里面也有分析。

現(xiàn)在開始說一說從NS SAR ADC被提出以來遇到的主要問題以及如何發(fā)展的。NS SAR的主要優(yōu)勢在于其能夠在傳統(tǒng)SAR ADC的結構內部實現(xiàn)Delta-sigma的操作,這無論從能量和面積上講都是非常高效的。在[1]提出NS SAR的理論基礎過后,其首先面對的問題有三點:1. 用于sample residue voltage的capacitor處引入額外的KT/C noise;2. 使用高功耗的static integrator,與低功耗的傳統(tǒng)SAR ADC的特點相矛盾。 3. 使用Multi-input-pair comparator,使得比較器的噪聲進一步增加。首先針對第一點,有些文章開始使用buffer來消除額外的KT/C noise限制,但引入buffer會帶來一定的限制,如果使用static buffer,那么靜態(tài)功耗則會增加;而如果使用dynamic buffer,則其會受到variation和low intrinsic gain的限制。針對第二點,為了避免引入功耗大的static integrator,有些文章開始采用fully passive noise shaping,即只使用switches和capacitors來實現(xiàn)filter,從而大大降低filter的功耗 ;這一方案同樣也有一定限制,具體體現(xiàn)為由于在charge sharing過程中的charge loss,導致無法實現(xiàn)agressive noise transfer function,大大減小了NS對ADC精度的提升;有文章利用comparator輸入尺寸的比例來實現(xiàn)對residue voltage的gain,但實際上更多comparator input-pair的引入導致了更為嚴重的comparator noise,有可能成為設計的瓶頸。 針對最后一點,這兩年的文章大多都采用了summation capacitor的來實現(xiàn)加法,這種方式允許只是用傳統(tǒng)的一對input pair的comparator。

目前有很多文章都采用了帶gain的buffer來補償filter的charge loss從而實現(xiàn)agressive noise transfer function,具體我會在后面論文分的分析里面提到。

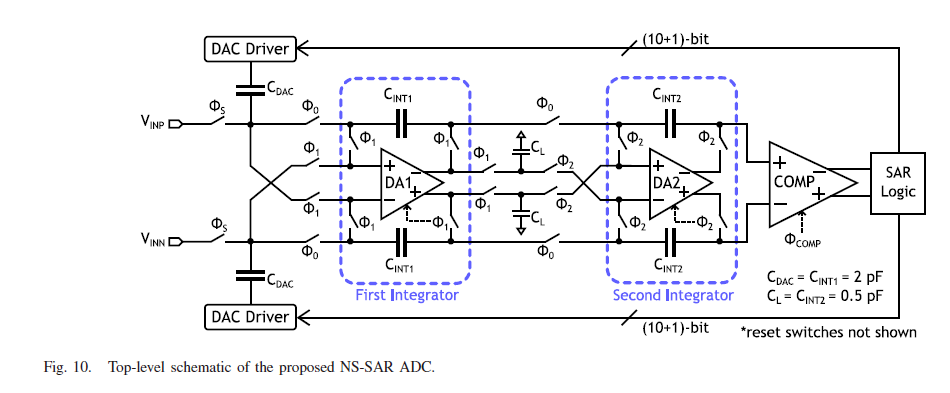

paper 1:'[3]X.Y. Tang, X.X. Yang, A 13.5-ENOB, 107-μW Noise-Shaping SAR ADC With PVT-Robust Closed-Loop Dynamic Amplifier, in IEEE Journal of Solid-State Circuits ( Volume: 55, Issue: 12, Dec. 2020), pp. 3248 - 3259'

這篇文章在我印象里是第一篇采用fully dynamic并且同時實現(xiàn)PVT robust aggressive NTF的。這篇文章的主要意圖是解決傳統(tǒng)的dynamic amplifier low gain以及無法保證PVT robustness的問題。因此,文章提出使用closed-loop floating inverter amplifier,其同樣作為dynamic amplifier,由于其current reuse以及較穩(wěn)定的輸出共模電平,使之具有high gain和PVT robust的特點。文章巧妙的使用CDAC和summation capacitor作為input capacitor和feedback capacitor,同時summation capacitor也作為integrator的輸出,這樣大大減少了area overhead。文章實現(xiàn)了PVT robust的2nd order CIFF NS,雖然階數(shù)并沒有太高,但仍達到了接近84dB的SNDR以及181.5dB的FoM。

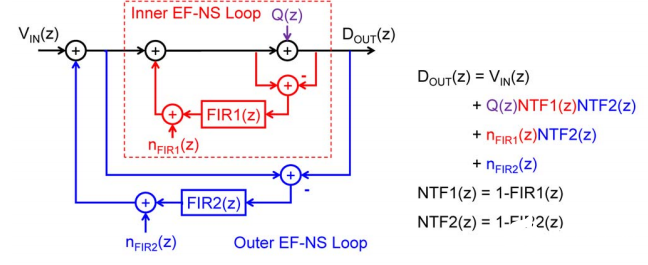

paper 2: '[4]J. Liu, B.Y. Zheng, A 4th-Order Cascaded-Noise-Shaping SAR ADC with 88dB SNDR Over 100kHz Bandwidth, in 2020 IEEE International Solid- State Circuits Conference - (ISSCC)'

這篇文章提出的cascaded NS方法非常巧妙。在這之前,如果要實現(xiàn)高階的NS,大多數(shù)采用switch和capacitor filter的文章都會面臨filter capacitor mismatch的問題,大大降低NS的有效性。這一篇文章提出了另一種方法,即cascade兩個二階的FIR filter,這樣實現(xiàn)的NTF成為了兩個二階high pass filter的乘積,有效減小了capacitor mismatch的影響。除此之外,這種方法也簡化了filter switch的control signal,更易于實現(xiàn)。從filter noise的角度來講,第一個FIR filter的noise會被第二個FIR filter shape,這使得第一個filter使用的capacitor的值可以減小同時不會引入過多的noise。但文章采用了open-loop static buffer,導致其性能在功耗上和PVT robustness方面并沒有達到最優(yōu)。

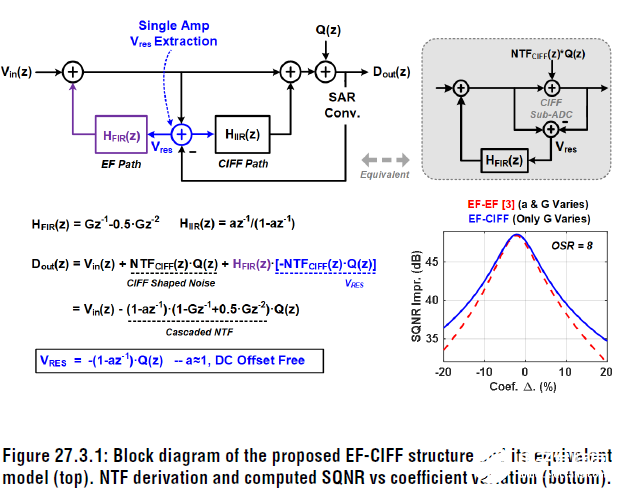

paper 3: ‘[5]TH. Wang, R. Wu, A 13.8-ENOB 0.4pF-CIN 3rd-Order Noise-Shaping SAR in a Single-Amplifier EF-CIFF Structure with Fully Dynamic Hardware-Reusing kT/C Noise Cancelation,in 2021 IEEE International Solid- State Circuits Conference - (ISSCC)’

這篇文章在NS工作原理部分就不展開了,可以參考上一篇日志。這篇文章提出的另一個比較重要的點在于其將sampling noise cancellation(SNC)使用到了NS SAR當中,大大降低了SAR ADC前級driver以及reference buffer的設計難度。關于sampling noise cancellation method,感興趣的話可以參考這篇文章引用到的文章,從實際應用角度是非常有意義的。

審核編輯:黃飛

-

SAR

+關注

關注

3文章

424瀏覽量

46639 -

adc

+關注

關注

99文章

6612瀏覽量

547800 -

比較器

+關注

關注

14文章

1805瀏覽量

108273

發(fā)布評論請先 登錄

相關推薦

SAR型ADC的結構及采樣過程

AD數(shù)據(jù)轉換-SAR ADC介紹

請教關于SAR ADC的噪聲譜計算

一種18位SAR ADC的設計實現(xiàn)

序列 SAR ADC 使您能夠在 PSoC 4 上配置和使用不同操作模式的 SAR ADC

SAR型ADC原理簡析

關于QTouch ADC的介紹與演示

SAR ADC的采樣過程和模擬輸入結構

關于NS SAR ADC的paper結構介紹

關于NS SAR ADC的paper結構介紹

評論