verilog中的task和function都是用于實(shí)現(xiàn)模塊中的可重復(fù)的功能,并且可以接收參數(shù)和返回結(jié)果。但是它們在編寫和使用上有一些區(qū)別。下面將詳細(xì)介紹task和function的區(qū)別。

- 語法結(jié)構(gòu):

- task的語法格式為:task [automatic|static] 數(shù)據(jù)類型 任務(wù)名稱 (輸入?yún)?shù)列表);

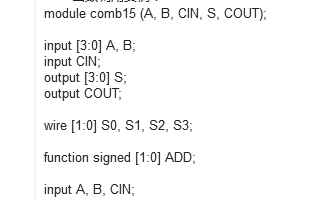

- function的語法格式為:函數(shù)數(shù)據(jù)類型 函數(shù)名稱 (輸入?yún)?shù)列表)

task和function都可以具有輸入?yún)?shù)列表,用于接收外部傳遞的參數(shù)。但是task可以沒有返回值,而function必須有返回值并且要明確指定返回的數(shù)據(jù)類型。

- 用途:

- task主要用于執(zhí)行一系列的操作或任務(wù),它可以包含多個(gè)語句,可以有輸入?yún)?shù),但是沒有返回值。task通常用于一組連續(xù)的語句塊,用于組織和封裝一系列的操作。例如,在時(shí)序邏輯中,可以使用task來實(shí)現(xiàn)狀態(tài)轉(zhuǎn)換。

- function主要用于執(zhí)行特定的計(jì)算或運(yùn)算,并返回一個(gè)結(jié)果。function可以包含多個(gè)語句,也可以有輸入?yún)?shù)。function通常用于將一組操作封裝成一個(gè)函數(shù),可以通過調(diào)用函數(shù)獲得運(yùn)算結(jié)果。例如,在組合邏輯中,可以使用function來實(shí)現(xiàn)一些計(jì)算和邏輯運(yùn)算。

- 調(diào)用方式:

- task通過調(diào)用task名稱來執(zhí)行,可以在任何地方使用task進(jìn)行調(diào)用,并可以在調(diào)用處返回一個(gè)任務(wù)。

- function通過調(diào)用function名稱來執(zhí)行,可以將函數(shù)的返回值賦值給一個(gè)變量,或者直接使用函數(shù)的返回值,用于其他計(jì)算和運(yùn)算。

- 變量聲明:

- task中聲明的變量作用域范圍為整個(gè)模塊,所有的任務(wù)都可以訪問這些變量。

- function中聲明的變量作用域范圍為函數(shù)體內(nèi),即只能在函數(shù)內(nèi)部訪問這些變量。

- 并發(fā)控制:

- task可以被多個(gè)模塊同時(shí)調(diào)用,可以并發(fā)執(zhí)行,但是task內(nèi)部的語句是按照順序執(zhí)行的。

- function只能在一個(gè)模塊內(nèi)被調(diào)用,并且在同一時(shí)間只能被一個(gè)模塊調(diào)用。

- 時(shí)間控制:

- task中可以使用

#和wait語句來實(shí)現(xiàn)時(shí)間控制和延遲。 - function中不允許使用

#和wait語句,因?yàn)閒unction本身的目的是進(jìn)行計(jì)算和運(yùn)算,而不是進(jìn)行延遲控制。

綜上所述,task和function在用途、語法結(jié)構(gòu)、調(diào)用方式、變量作用域、并發(fā)控制和時(shí)間控制方面都有一定的區(qū)別。根據(jù)實(shí)際需求選擇使用task或function,能更好地實(shí)現(xiàn)所需的功能。

-

模塊

+關(guān)注

關(guān)注

7文章

2785瀏覽量

50016 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

112054 -

參數(shù)

+關(guān)注

關(guān)注

11文章

1867瀏覽量

32956 -

Function

+關(guān)注

關(guān)注

0文章

14瀏覽量

10090 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4377瀏覽量

64546

發(fā)布評論請先 登錄

例說Verilog HDL和VHDL區(qū)別

轉(zhuǎn)載---verilog中task和function的區(qū)別

verilog HDL學(xué)習(xí)筆記

煉獄傳奇-task_function之戰(zhàn)

Verilog函數(shù)中function里的過程語句該怎么寫

Verilog的task和function說明語句

簡談FPGA verilog中的task用法

簡談FPGA verilog中的function用法與例子

verilog task和function區(qū)別

verilog task和function區(qū)別

評論