QFN封裝引腳間距較小問(wèn)題:產(chǎn)生原因與解決方案

QFN封裝引腳間距較小問(wèn)題是什么?

產(chǎn)生QFN封裝引腳間距較小問(wèn)題,為什么?

解決QFN封裝引腳間距較小問(wèn)題要怎么辦?

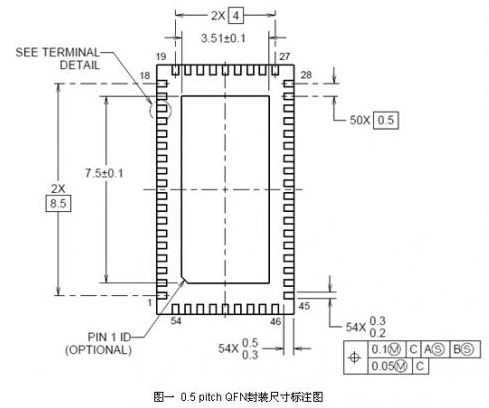

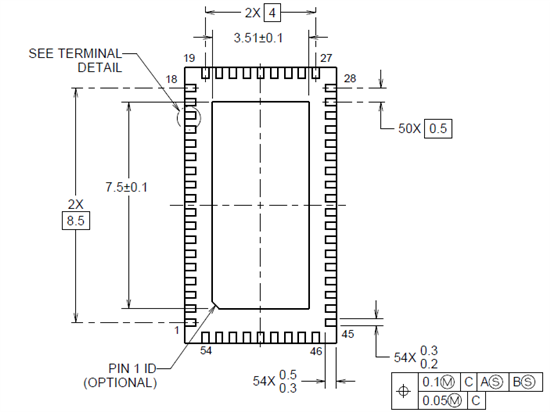

QFN封裝的引腳間距較小是指在該封裝中,相鄰引腳之間的距離相對(duì)較小。這種設(shè)計(jì)有助于減小整體封裝的尺寸,使芯片的集成更加緊湊,從而在有限的空間內(nèi)容納更多的引腳和電路。這也是QFN封裝被廣泛用于需要小型化和高集成度的應(yīng)用的原因之一。

小間距的引腳可以提供以下優(yōu)勢(shì):

緊湊性:

引腳間距較小允許在有限的空間內(nèi)容納更多的引腳,從而實(shí)現(xiàn)緊湊的封裝設(shè)計(jì)。

電氣性能:

小間距有助于減少引腳之間的電感和串?dāng)_,對(duì)于高頻應(yīng)用具有一定的優(yōu)勢(shì)。

熱性能:

小間距有助于提高散熱性能,因?yàn)樵谙嗤牡撞糠庋b面積上有更多的引腳可以用于散熱。

信號(hào)完整性:

較小的引腳間距可以降低信號(hào)傳輸?shù)膿p失,對(duì)于高速信號(hào)和高頻應(yīng)用更有利。

需要注意的是,雖然小間距可以提供上述優(yōu)勢(shì),但也增加了焊接和布局的復(fù)雜性,因此在設(shè)計(jì)和制造過(guò)程中需要特別注意。焊接過(guò)程需要更高的精度,而布局需要更謹(jǐn)慎地考慮信號(hào)完整性和熱管理。

"QFN封裝"是什么?

QFN是Quad Flat No-leads的縮寫(xiě),它是一種集成電路封裝的形式。QFN封裝通常是一種無(wú)引腳焊盤(pán)的封裝,也被稱(chēng)為“裸露焊盤(pán)”或“底部焊盤(pán)”封裝。與傳統(tǒng)的封裝相比,QFN封裝的特點(diǎn)是它沒(méi)有外露的引腳,而是將引腳隱藏在封裝的底部。

QFN封裝的主要特點(diǎn)包括:

無(wú)引腳外露:

QFN封裝沒(méi)有傳統(tǒng)封裝中突出的引腳,而是將引腳放置在封裝的底部,通過(guò)焊盤(pán)連接到電路板上。

緊湊設(shè)計(jì):

由于沒(méi)有引腳外露,QFN封裝可以設(shè)計(jì)得非常緊湊,從而占用更少的空間。

散熱性能好:

由于QFN封裝的底部通常是金屬的,因此它具有良好的散熱性能,有助于提高芯片的熱穩(wěn)定性。

適用于高頻應(yīng)用:

由于QFN封裝的設(shè)計(jì),它對(duì)高頻應(yīng)用有較好的適應(yīng)性,減少了因引腳長(zhǎng)度和電感等因素引起的信號(hào)失真。

QFN封裝在電子產(chǎn)品中廣泛應(yīng)用,特別是在需要小型化、高性能和散熱要求較高的應(yīng)用中,如移動(dòng)設(shè)備、通信設(shè)備和各種嵌入式系統(tǒng)。

QFN封裝引腳間距較小問(wèn)題會(huì)導(dǎo)致什么?

焊接困難:

引腳間距較小可能導(dǎo)致焊接過(guò)程的復(fù)雜性增加。在組裝過(guò)程中,對(duì)焊點(diǎn)的精確控制要求較高,需要更高的生產(chǎn)精度,否則可能導(dǎo)致焊接質(zhì)量不穩(wěn)定,例如焊接不良或短路。

布局設(shè)計(jì)挑戰(zhàn):

較小的引腳間距使得布局設(shè)計(jì)更為復(fù)雜。在電路板設(shè)計(jì)中,需要特別注意信號(hào)完整性、阻抗匹配和防止串?dāng)_,以確保電路性能穩(wěn)定。

維修困難:

由于引腳間距較小,對(duì)QFN封裝的芯片進(jìn)行維修變得更加困難。手工焊接和重新焊接可能需要更高的技術(shù)水平。

散熱挑戰(zhàn):

盡管較小的引腳間距有助于提高散熱性能,但也可能使散熱更為具有挑戰(zhàn)性。在高功率應(yīng)用中,需要特別注意散熱設(shè)計(jì),以確保芯片工作在安全的溫度范圍內(nèi)。

高頻應(yīng)用的損耗:

對(duì)于極高頻或高速數(shù)字應(yīng)用,小引腳間距可能導(dǎo)致信號(hào)傳輸損耗增加,需要更加精密的布局和設(shè)計(jì)。

總體而言,雖然QFN封裝引腳間距較小的設(shè)計(jì)提供了許多優(yōu)勢(shì),但在選擇和應(yīng)用時(shí),設(shè)計(jì)工程師需要在小型化、性能、制造工藝和可維護(hù)性之間進(jìn)行權(quán)衡,并確保在應(yīng)用中的合適性。

出現(xiàn)QFN封裝引腳間距較小問(wèn)題是為什么?

01小型化和高集成度:

QFN封裝的設(shè)計(jì)旨在實(shí)現(xiàn)小型化和高度集成的電子器件。通過(guò)減小引腳間距,芯片制造商可以在有限的空間內(nèi)容納更多的引腳,從而實(shí)現(xiàn)更緊湊的封裝。

02空間效率:

較小的引腳間距使得QFN封裝能夠更有效地利用底部封裝面積,因?yàn)橐_可以更緊密地排列。這對(duì)于現(xiàn)代電子設(shè)備中有限的空間非常重要,例如智能手機(jī)、平板電腦和其他便攜式設(shè)備。

03散熱性能:

QFN封裝通常具有金屬底部,可以提供較好的散熱性能。通過(guò)減小引腳間距,可以在有限的底部空間內(nèi)增加更多的焊盤(pán),提高了封裝的散熱效果,有助于維持芯片的溫度在可接受的范圍內(nèi)。

04高頻應(yīng)用:

小引腳間距有助于減小引腳之間的電感和串?dāng)_,這對(duì)于高頻應(yīng)用非常重要。在無(wú)線(xiàn)通信、射頻(RF)和其他高頻電路中,QFN封裝的設(shè)計(jì)可以提供更好的性能。

解決方案

精密制造工藝:

提高制造工藝的精度是確保引腳間距小的QFN封裝焊接質(zhì)量的關(guān)鍵。使用高精度的制造設(shè)備和工藝能夠減小焊接誤差,提高焊點(diǎn)的可靠性。

精確的布局設(shè)計(jì):

在電路板布局設(shè)計(jì)階段,工程師需要仔細(xì)考慮引腳的布局,確保信號(hào)完整性、阻抗匹配和防止串?dāng)_。使用先進(jìn)的設(shè)計(jì)工具可以幫助進(jìn)行精確的布局規(guī)劃。

高精度的焊接技術(shù):

采用高精度的焊接技術(shù),如回流焊或波峰焊,以確保引腳焊接的質(zhì)量。在生產(chǎn)過(guò)程中,控制溫度和焊接時(shí)間,以防止焊點(diǎn)過(guò)度或不足。

自動(dòng)化生產(chǎn):

自動(dòng)化生產(chǎn)線(xiàn)可以提高制造過(guò)程的一致性和精度。使用自動(dòng)化設(shè)備,如表面貼裝技術(shù)(SMT)設(shè)備和焊接爐,可以減小人為因素對(duì)生產(chǎn)過(guò)程的影響。

良好的散熱設(shè)計(jì):

對(duì)于QFN封裝,由于底部通常是金屬的,散熱性能較好。設(shè)計(jì)工程師應(yīng)該注重良好的散熱設(shè)計(jì),確保芯片在工作時(shí)能夠有效散熱,避免溫度升高。

封裝選擇:

在一些特殊情況下,可以考慮選擇具有稍大引腳間距的QFN封裝型號(hào),以降低設(shè)計(jì)和制造的難度,盡管可能會(huì)略微增加封裝的體積。

這些解決方法的選擇取決于具體的應(yīng)用和設(shè)計(jì)要求。在實(shí)際應(yīng)用中,工程師需要綜合考慮設(shè)計(jì)復(fù)雜性、生產(chǎn)成本、性能和可維護(hù)性等因素,以找到最合適的平衡點(diǎn)。

審核編輯:湯梓紅

-

集成電路

+關(guān)注

關(guān)注

5423文章

12033瀏覽量

368200 -

QFN封裝

+關(guān)注

關(guān)注

0文章

177瀏覽量

17169 -

引腳

+關(guān)注

關(guān)注

16文章

1700瀏覽量

52758

原文標(biāo)題:QFN封裝引腳間距較小問(wèn)題,怎么辦?

文章出處:【微信號(hào):CEIA電子智造,微信公眾號(hào):CEIA電子智造】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

什么是QFN封裝?手動(dòng)焊接QFN封裝方式

小間距QFN封裝PCB設(shè)計(jì)串?dāng)_抑制問(wèn)題分析與優(yōu)化

什么是小間距QFN封裝PCB設(shè)計(jì)串?dāng)_抑制?

怎么抑制PCB小間距QFN封裝引入的串?dāng)_

針對(duì)PCB設(shè)計(jì)中由小間距QFN封裝引入串?dāng)_的抑制方法

四側(cè)無(wú)引腳扁平封裝(QFN),四側(cè)無(wú)引腳扁平封裝(QFN)是

PCB設(shè)計(jì)中由小間距QFN封裝引入串?dāng)_的抑制方法分析

PCB小間距QFN封裝引入串?dāng)_的抑制方法資料下載

小間距QFN封裝PCB設(shè)計(jì)串?dāng)_抑制的分析

QFN封裝有哪些特點(diǎn)

SMT加工產(chǎn)生冷焊的原因以及解決方案

宇凡微QFN20封裝介紹,QFN20封裝尺寸圖

qfn封裝的優(yōu)缺點(diǎn)

羅徹斯特電子QFN解決方案

QFN封裝引腳間距較小問(wèn)題的產(chǎn)生原因與解決方案

QFN封裝引腳間距較小問(wèn)題的產(chǎn)生原因與解決方案

評(píng)論