Cadence 17.4后將ORCAD與ALLEGRO的聯(lián)系更加緊密,同時PCB仿真功能有明顯的提升,以前PCB的后仿真基本是在Cadence Sigrity中完成。而現(xiàn)在Cadence將Sigrity 的功能與Allegro 完美地結(jié)合,使用戶能在PCB界面中直接調(diào)用Sigrity Aurora分析工具,可以實現(xiàn)現(xiàn)場分析,現(xiàn)場修改。

在此之前先介紹下Sigrity Aurora

Sigrity Aurora是一款強(qiáng)大的電子系統(tǒng)仿真軟件,它支持多種類型的仿真分析,包括信號完整性(SI)分析、電源完整性(PI)分析以及3D電磁場仿真等。該軟件可以針對電子系統(tǒng)中的高速互連、電源分布和電磁干擾等問題進(jìn)行精確建模和仿真,幫助工程師在設(shè)計階段預(yù)測和優(yōu)化系統(tǒng)的性能。

在Sigrity Aurora中,用戶可以通過直觀的用戶界面創(chuàng)建和編輯仿真模型,包括電路原理圖、3D電磁場模型等。軟件內(nèi)置了豐富的元件庫和參數(shù)設(shè)置選項,可以滿足各種復(fù)雜的仿真需求。同時,Sigrity Aurora還支持與其他CAD軟件的集成,如Cadence Allegro等,可以實現(xiàn)無縫的數(shù)據(jù)交換和協(xié)同設(shè)計。

除了基本的仿真功能外,Sigrity Aurora還提供了一系列高級功能,如自動優(yōu)化算法、蒙特卡洛分析等,可以幫助用戶更加高效地進(jìn)行仿真分析和設(shè)計優(yōu)化。此外,軟件還提供了豐富的后處理功能,包括結(jié)果可視化、數(shù)據(jù)導(dǎo)出等,方便用戶進(jìn)行結(jié)果分析和報告制作。

了解了Sigrity Aurora之后,介紹在PCB完成后利用Sigrity Aurora對走線的阻抗分析

一,先用Allegro打開待分析的PCB文件

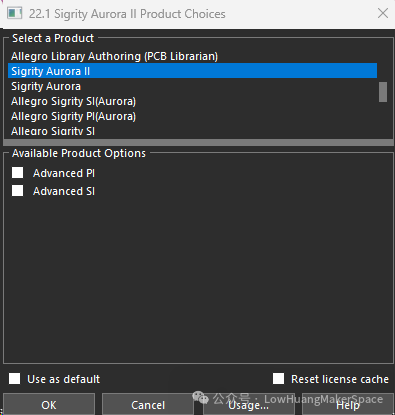

選擇File> ChangeEditor>選擇Sigrity Aurora II組件

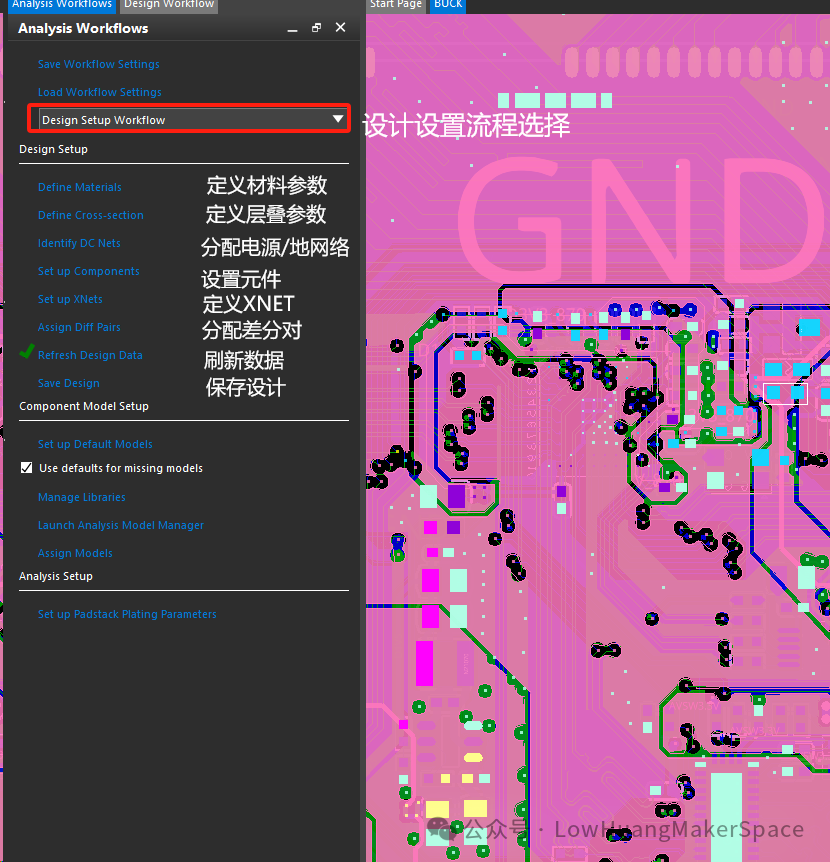

二、選擇分析工具:Analyze>workflows manager

三、參數(shù)設(shè)置

1,在分析阻抗前要對以下設(shè)計參數(shù)設(shè)置

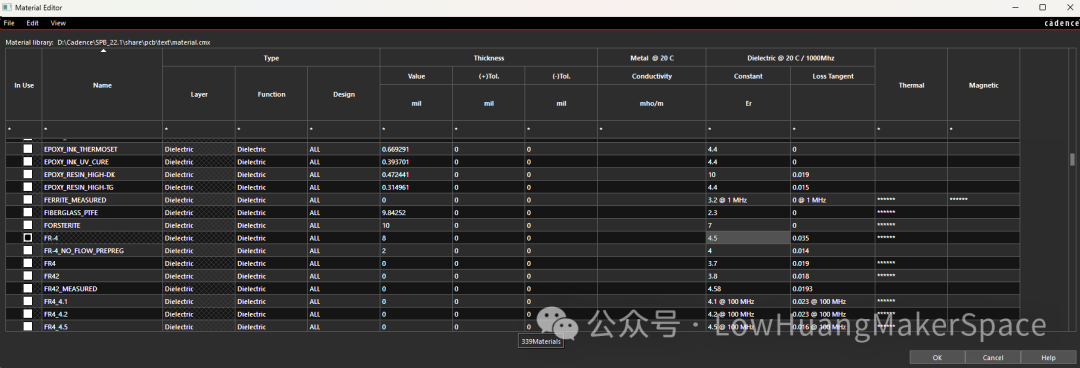

定義材料:對PCB的材料參數(shù),里面有常用339種材料,在設(shè)計中用到的有AIR、FR-4、COPPER、三種,根據(jù)PCB廠家給的參數(shù),支持修改。

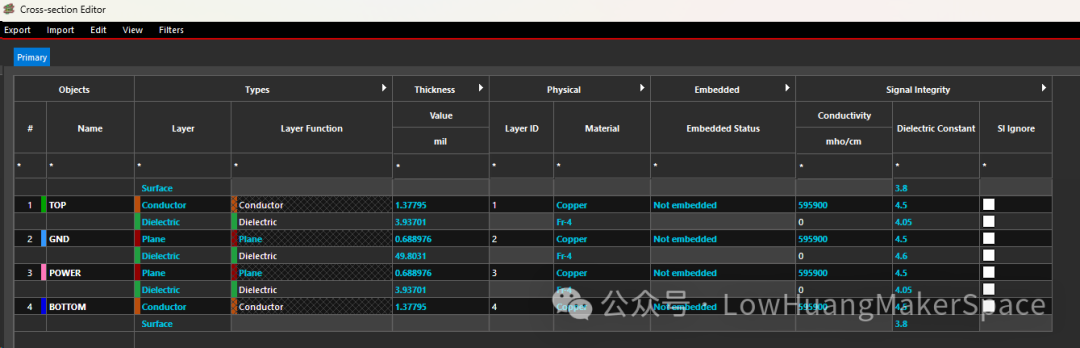

定義層疊結(jié)構(gòu):對于PCB的阻抗而言層疊參數(shù)是關(guān)鍵

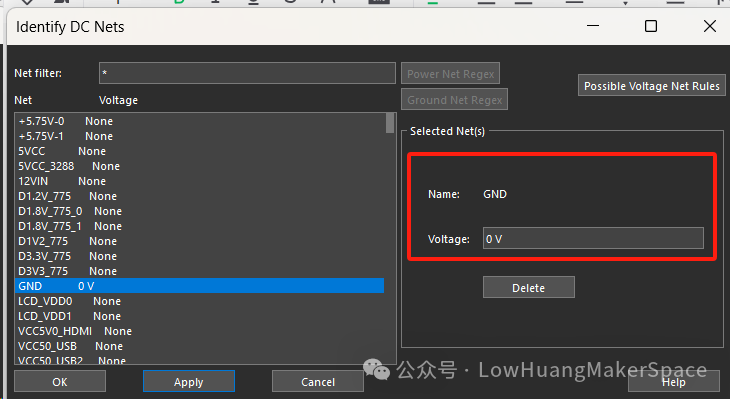

分配電源和地網(wǎng)絡(luò):這一步其實是設(shè)置參考平面的網(wǎng)絡(luò)及電氣參數(shù),對于用到的參考平面的網(wǎng)絡(luò)都需要定義。

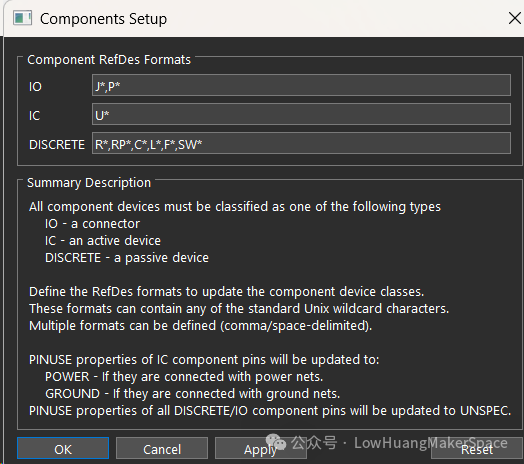

設(shè)置元件:這一步的目的是讓軟件根據(jù)位號前綴自動識別出元件類型

如:IC的前綴默認(rèn)是U,電阻是R,如有自定義的需要在這里告訴軟件

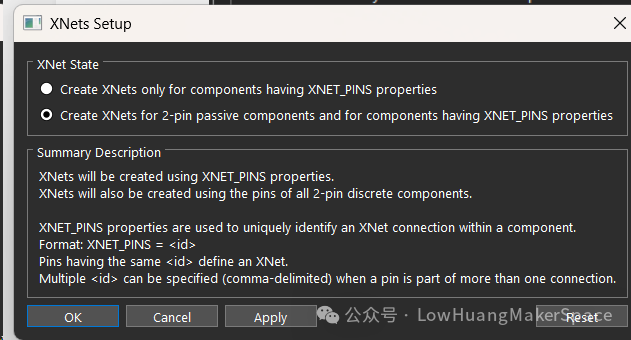

定義XNET網(wǎng)絡(luò):Xnet一般是在Allegro中已經(jīng)定義好了,因為做約束規(guī)則時要用,這里選默認(rèn)就好。

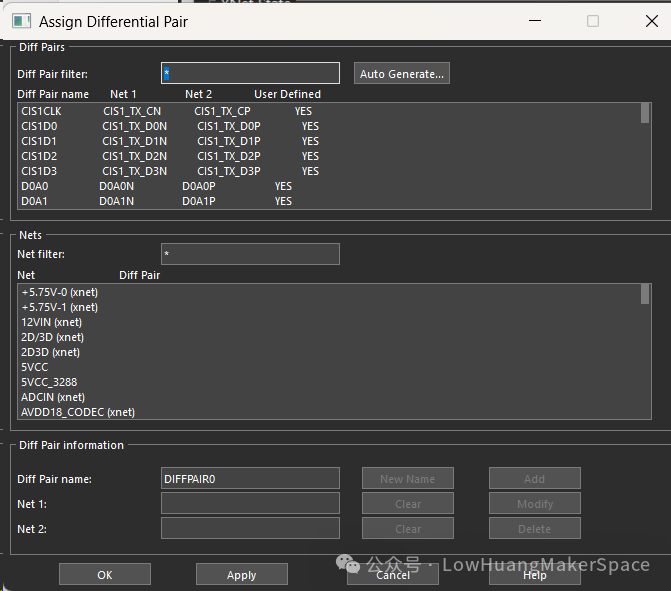

分配差分對:差分對同樣一般是在Allegro中已定經(jīng)定義好了,因為做約束規(guī)則時要用,如果前期沒有做,這里對你要分析的差分對進(jìn)行添加。

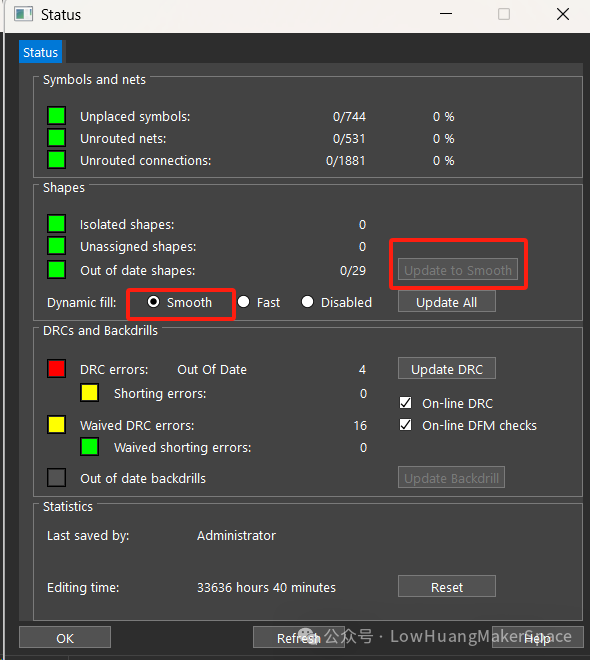

刷新數(shù)據(jù):因為PCB畫完后,有時對走線進(jìn)行調(diào)整后,一些動態(tài)銅皮可能會有一些變化,因此在分析前需要確認(rèn)。

選擇Display>Status 選對Smooth后Update to Smooth

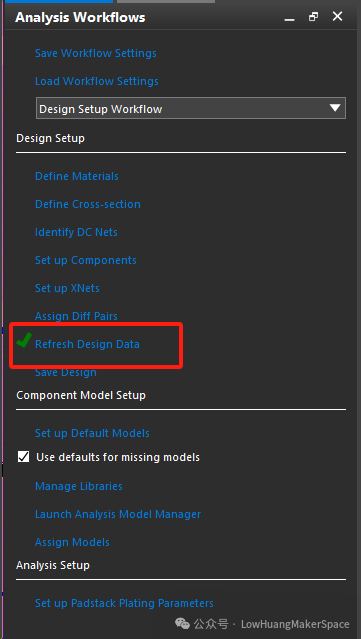

回到DesignSetup窗口點Refresh Design Data

保證設(shè)計:最后將設(shè)計保存

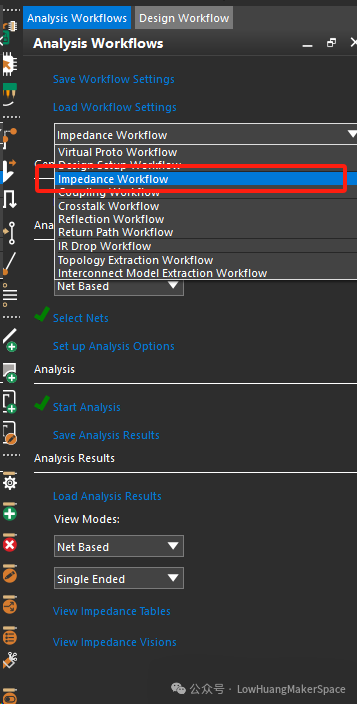

四、阻抗分析

1,進(jìn)入到阻抗分析流程

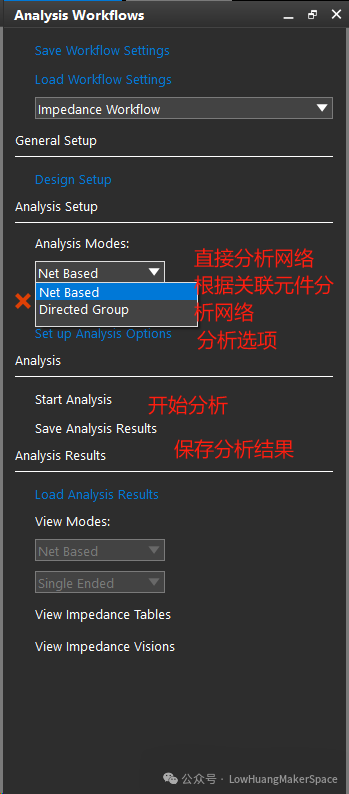

2,分析選項目設(shè)置

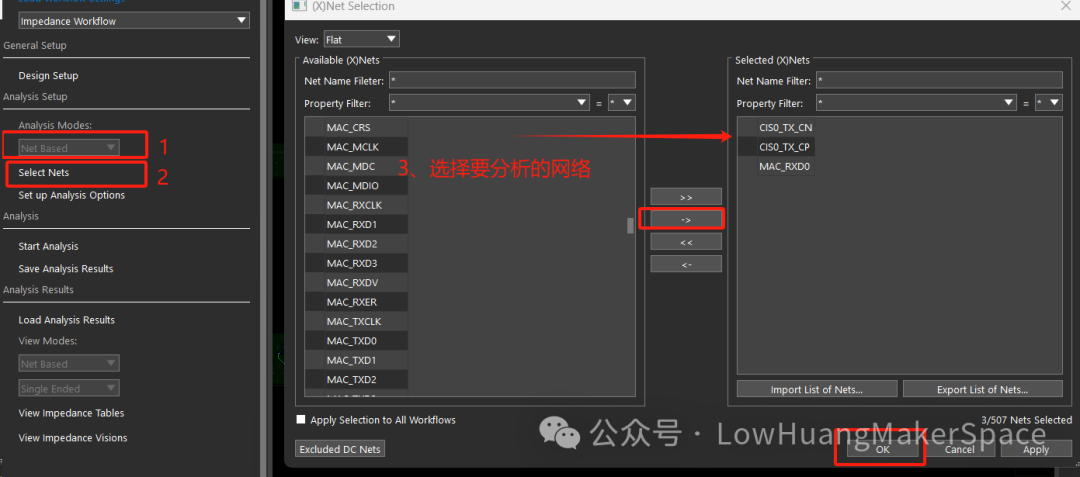

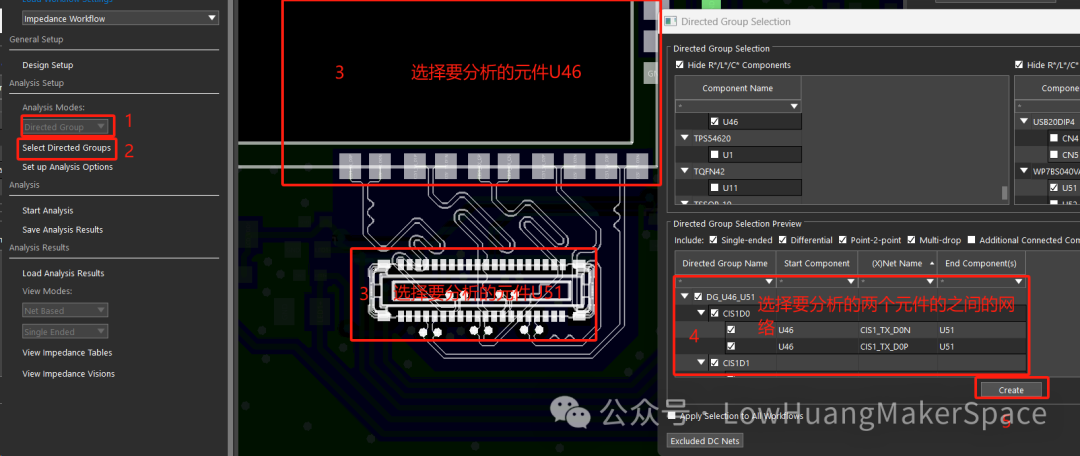

NetBased:用于選擇單一網(wǎng)絡(luò)進(jìn)行分析

Directed Group:用于選擇兩個元件之的網(wǎng)絡(luò)進(jìn)行分析

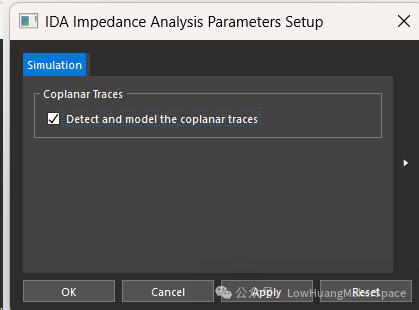

Set up Analysis Options:設(shè)置分析選項 可選可不選。

3、點選開始分析,等待分析完成。

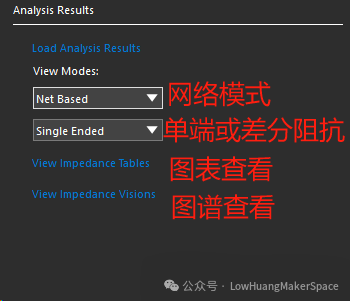

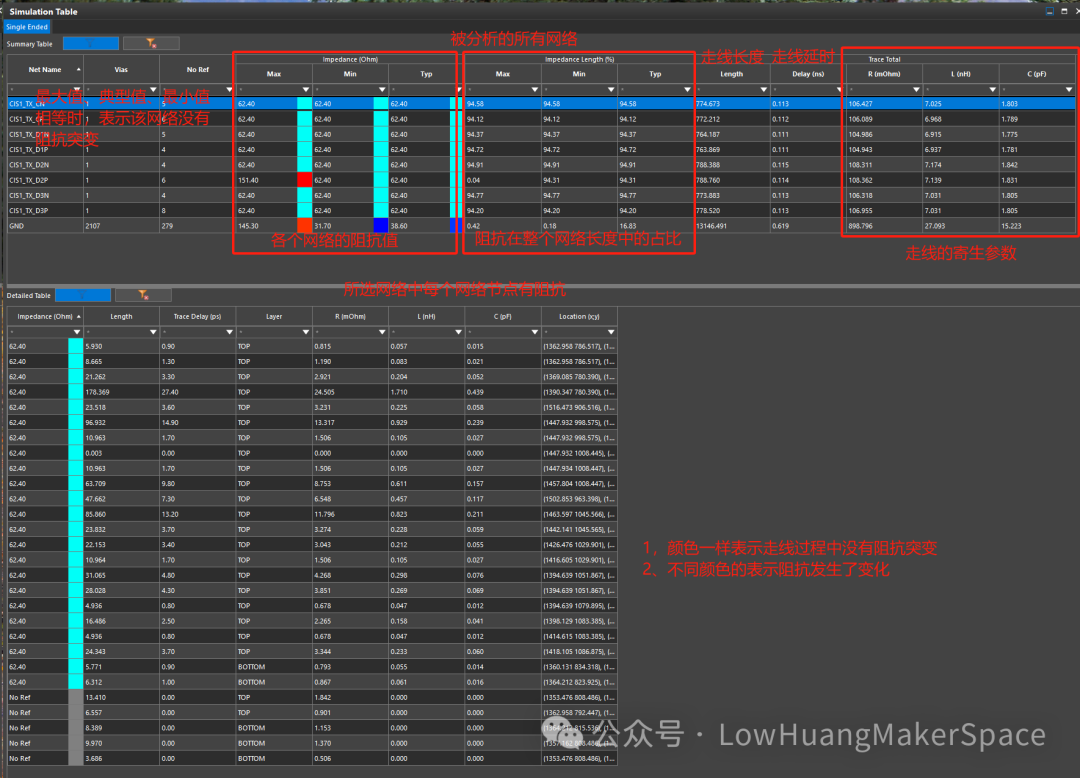

五、結(jié)果查看與解讀

如果分析的是單端網(wǎng)絡(luò),就選單端,否則就選差分;如果都有分兩次查看

1,圖表查看:選擇 View impedance table

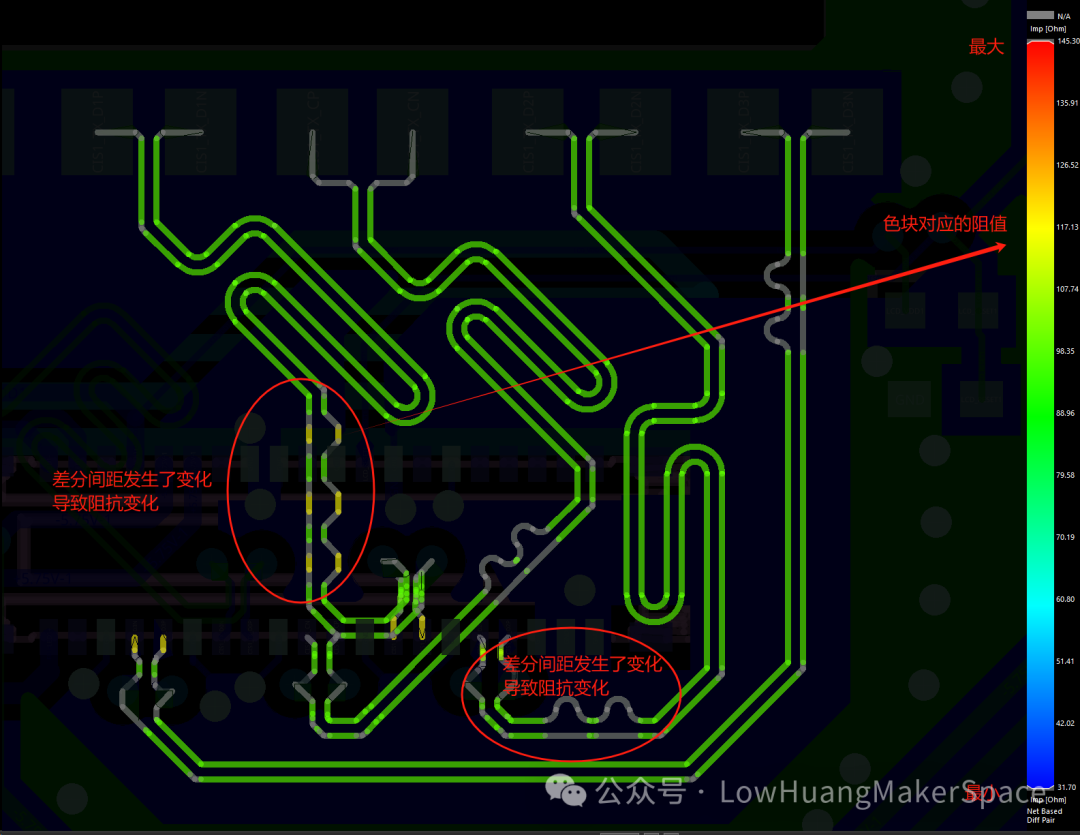

2、圖譜查看選擇 View impedancevisions

圖譜查看的方式更為直觀的查看到阻抗變化的位置

總結(jié):通過軟件工具我們可以很方便的檢測出阻抗的問題,同時可以現(xiàn)場調(diào)整后再進(jìn)行分析。在設(shè)計中差分阻抗發(fā)生變化,一般是由于繞線或拐角處,間距或線寬發(fā)生了變化導(dǎo)致;單端阻抗發(fā)生變化的原因一般是由于平面的分割造成,或者過孔換層處,沒有了參考層,再或者是BGA出線處線寬發(fā)生了變化導(dǎo)致。

審核編輯:劉清

-

Cadence

+關(guān)注

關(guān)注

67文章

966瀏覽量

143894 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2381瀏覽量

106325 -

PCB布線

+關(guān)注

關(guān)注

21文章

469瀏覽量

42534 -

allegro

+關(guān)注

關(guān)注

42文章

708瀏覽量

147034 -

電源完整性

+關(guān)注

關(guān)注

9文章

219瀏覽量

21142

原文標(biāo)題:Cadence Allegro 22.1 利用Sigrity Aurora 進(jìn)行PCB布線后的仿真分析--阻抗及寄生參數(shù)析

文章出處:【微信號:LowHuangMakerSpace,微信公眾號:LowHuangMakerSpace】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

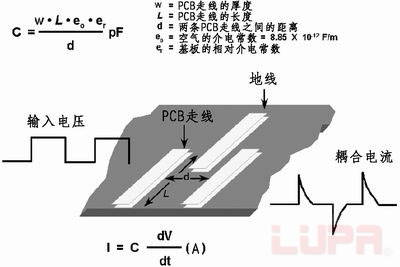

PCB布線設(shè)計時寄生電容的計算方法

埋容的PCB設(shè)計與PI仿真 三

【轉(zhuǎn)帖】PCB仿真分析解決方案

【下載】Cadence高速電路設(shè)計Allegro Sigrity SIPIEMI設(shè)計指南 [陳蘭兵] 電子書PDF+隨書光盤

【免費(fèi)直播】李增和大家一起學(xué)習(xí)S參數(shù)的相關(guān)知識及提取解讀分析優(yōu)化S參數(shù)的方法

使用Cadence Allegro 17.4軟件進(jìn)行布線阻抗分析的具體方法

PCB布線產(chǎn)生的寄生電感對DC-DC效率的影響

利用Sigrity Aurora進(jìn)行PCB布線后的仿真分析-阻抗及寄生參數(shù)析

利用Sigrity Aurora進(jìn)行PCB布線后的仿真分析-阻抗及寄生參數(shù)析

評論