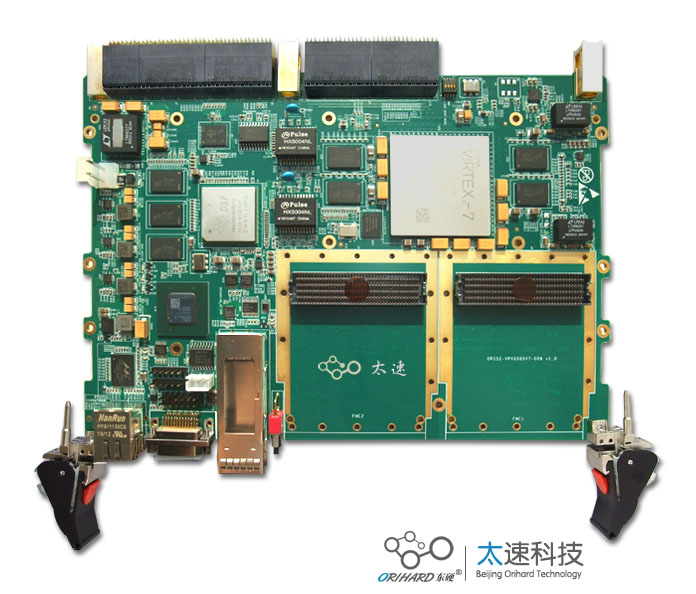

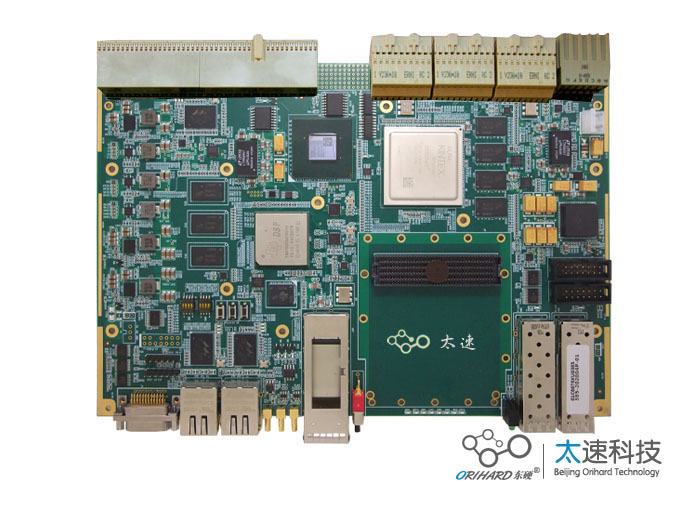

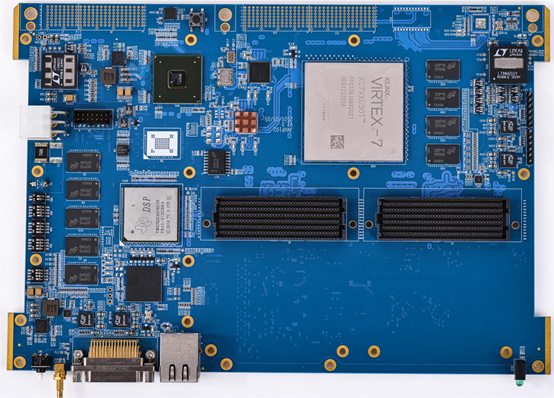

基于6U VPX的雙TMS320C6678+Xilinx FPGA K7 XC7K420T的圖像信號處理板

綜合圖像處理硬件平臺包括圖像信號處理板2塊,視頻處理板1塊,主控板1塊,電源板1塊,VPX背板1塊。

一、板卡概述

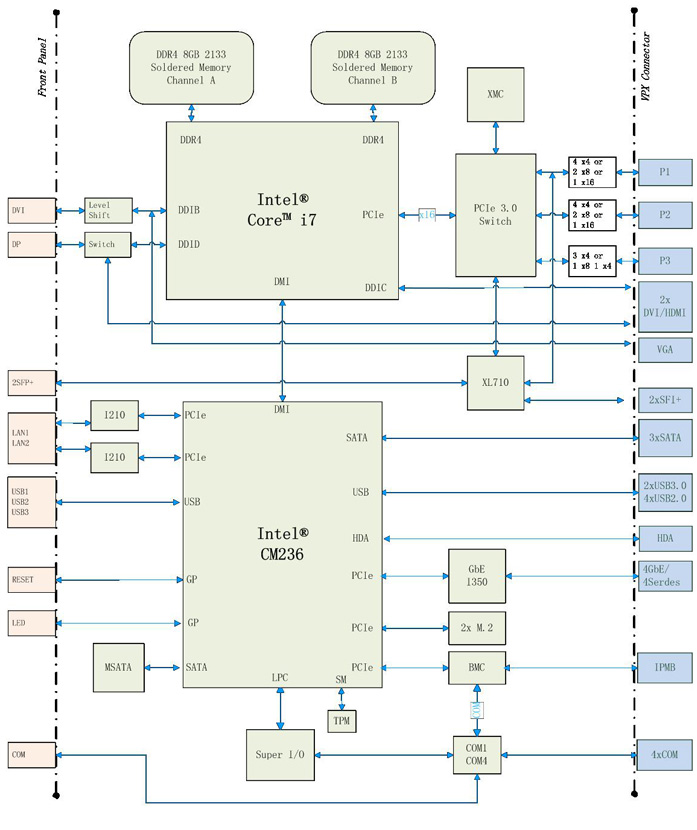

圖像信號處理板包括2片TI 多核DSP處理器-TMS320C6678,1片Xilinx FPGA XC7K420T-1FFG1156,1片Xilinx FPGA XC3S200AN。實現四路千兆以太網輸出,兩路422輸出。通過FPGA的GTX ,LVDS實現高速背板互聯。采用6u VPX架構。芯片滿足工業級要求,板卡滿足抗震要求。

視頻信號處理板卡負載對視頻信號進行處理,返回或輸出。板卡采用雙 TI 8核DSP處理器 TMSC6678,Xilinx的 K7-XC7K420T處理器 ,Xilinx 的Spartans XC3S200AN處理器,TI的MSP430處理器。其中CFPGA負責管理板卡的上電時序,時鐘配置,系統及模塊復位等,MCU負責檢測板卡的溫度、電源。

二、技術指標

支持2個TMS320C6678芯片,每片DSP外掛DDR3,256M x 64bit容量; Nor Flash 16M x16bit容量;4路以太網接口,DSP之間通過HyperLink x4 互聯,支持4 x 3.125Gbps帶寬。

DSP與K7直接通過RapidIO x4模式互聯,支持4 x 3.125 Gbp速度,

DSP 與K7 通過I2c,SPI,Uart,GPIO接口互聯。

DSP調試為普通JTAG口, FPGA-K7為BPI模式。

板卡要求工業級芯片。結構滿足抗震要求。

板卡采用雙電源供電,12v~6A,5v~1A。

三、接口互聯設計

兩片6678通過 Hyperlink x4 @3.125Gbps /per Lane 互聯。

每片6678的SGMII-0通過PHY芯片,連接至排針。

每片6678的SGMII-1通過PHY芯片,連接到VPX-P4。

每片6678的PCIe x2 連接至VPX-P3。

每片6678和K7通過 SRIO x4 @ 3.125G bps /per Lnae互聯。

每片6678和K7實現GPIO,SPI,I2C,UART互聯。

每片6678 和CFPGA 實現GPIO,SPI互聯。

K7和CFPGA實現GPIO互聯。

K7的 GTX x20 分別連接至 VPX的P1,P2,P3接口

K7的LVDS x10 連接至VPX-P5。

K7 輸出兩組422信號連接至VPX-P4。4

四、軟件代碼

DDR3讀寫測試測試

NorFlash軟件讀寫測試

NandFlash軟件讀寫測試

Eeprom讀寫測試

千兆以太網測試,支持UDP傳輸協議

HyperLink互聯測試

NorFlash 程序加載測試

K7 DDR3軟件讀寫測試

K7 BPI 程序加載測試

K7 SPI NorFlash 讀寫測試

DSPA/B和K7 I2C 互聯測試

DSPA/B和K7 SPI 互聯測試

DSPA/B和K7 GPIO 互聯測試

DSPA/B和K7 UART 互聯測試

DSPA/B和K7 SRIO 互聯測試

五、物理特性:

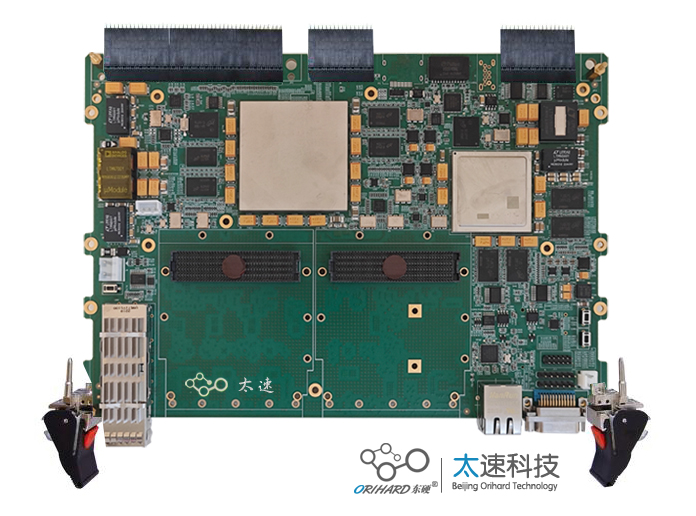

尺寸:6U VPX板卡,大小為160X233.35mm。

工作溫度:0℃~ +55℃ ,支持工業級 -40℃~ +85℃

工作濕度:10%~80%

六、系統搭建:

七、應用領域

軟件無線電系統,基帶信號處理,無線仿真平臺,高速圖像采集、處理等。

標簽: C6678板卡 , 高速圖像采集 , 基帶信號處理 , 軟件無線電系統 , 無線仿真平臺

審核編輯 黃宇

-

基帶信號

+關注

關注

0文章

32瀏覽量

11236 -

圖像信號

+關注

關注

0文章

27瀏覽量

14222

發布評論請先 登錄

相關推薦

高速圖像采集卡設計方案:204-基于Xilinx Virtex-6 XC6VLX240T 和TI DSP TMS320C6678的信號處理板

FMC子卡設計方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數據處理核心板

6U CPCI板卡設計方案:8-基于雙TMS320C6678 + XC7K420T的6U CPCI Express高速數據處理平臺

【米爾-Xilinx XC7A100T FPGA開發板試用】+01.開箱(zmj)

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡

XCVU9P 板卡設計原理圖:616-基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡 高性能數字計算卡

TMS320C6678多核固定和浮點數字信號處理器數據表

TMS320C6414T,TMS320C6415T,TMS320C6416T定點數字信號處理器數據表

基帶信號處理設計原理圖:基于6U VPX的雙TMS320C6678+Xilinx FPGA K7 XC7K420T的圖像信號處理板

基帶信號處理設計原理圖:基于6U VPX的雙TMS320C6678+Xilinx FPGA K7 XC7K420T的圖像信號處理板

評論