隨著電子技術(shù)的進(jìn)步.FPGA邏輯電路能完成的功能越來(lái)越多,同樣也帶來(lái)了一個(gè)很大的問(wèn)題,即邏輯電路的規(guī)模越來(lái)越大,這意味著RTL代碼到FPGA的映射、布局布線所花費(fèi)的時(shí)間也越來(lái)越長(zhǎng)。

如果代碼結(jié)構(gòu)不合理,編寫(xiě)隨意,沒(méi)有考慮到FPGA布局布線的可行性以及時(shí)序收斂的問(wèn)題,那么很可能使時(shí)序收斂非常困難,更壞的情況是布局布線失敗(即place and route fail)。這種情況在大規(guī)模的設(shè)計(jì)、大規(guī)模的FPGA上更為常見(jiàn),因此有必要專(zhuān)門(mén)有一個(gè)章來(lái)講RTL代碼的設(shè)計(jì)、電路結(jié)構(gòu)的設(shè)計(jì)、大規(guī)模邏輯電路的技巧以及如何解決此類(lèi)問(wèn)題。

布局布線失敗

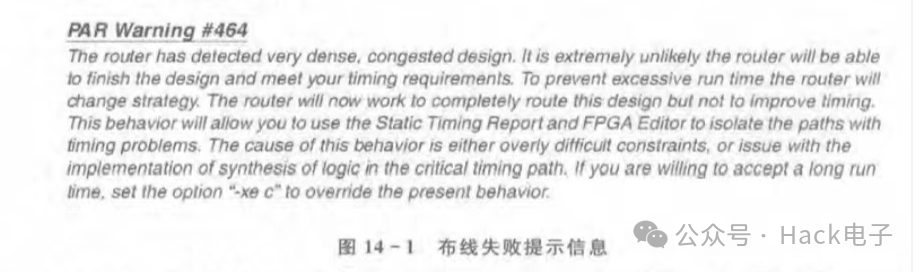

在某些FPGA中,特別是在大規(guī)模的FPGA(XilinxVirtex6以上,AlteraStratixIV以上)中實(shí)現(xiàn)大規(guī)模的設(shè)計(jì),如果前期沒(méi)有對(duì)設(shè)計(jì)的邏輯電路做好結(jié)構(gòu)優(yōu)化,同時(shí)不注意代碼風(fēng)格,那么很可能會(huì)帶來(lái)一個(gè)問(wèn)題:布局布線失敗。這種現(xiàn)象困擾著設(shè)計(jì)者因?yàn)橐粋€(gè)大型的設(shè)計(jì)從綜合到布局布線通常需要花費(fèi)十來(lái)個(gè)小時(shí),有些甚至是一兩天的時(shí)間,而這種結(jié)果意味著這些時(shí)間將被極大地浪費(fèi)。該現(xiàn)象一般在FPGA工具中會(huì)出現(xiàn)如圖14-1所示的信息。

圖14-1 布線失敗提示信息

圖14-1的大體意思是說(shuō)布線工具(router)檢測(cè)到當(dāng)前是一個(gè)非常密集(dense)擁塞(congested)的設(shè)計(jì),布線工具有可能沒(méi)有辦法實(shí)現(xiàn)布線。這里的密集和擁塞是指什么呢?從字面上意思理解就是FPGA布線工具在進(jìn)行布線的時(shí)候,發(fā)現(xiàn)設(shè)計(jì)的某些部分在布局后器件之間的分布過(guò)于密集,連線過(guò)于復(fù)雜,因此無(wú)法完成布線。

這跟PCB的設(shè)計(jì)有點(diǎn)類(lèi)似,當(dāng)PCB的布局不合理或者器件過(guò)多的時(shí)候,有可能在指定的面積下無(wú)法完成布線,只能通過(guò)增加PCB面積或者層數(shù)來(lái)完成。

那么對(duì)于FPGA來(lái)說(shuō)到了設(shè)計(jì)能夠布局布線階段,這已經(jīng)是一個(gè)中期的階段,此時(shí)要重新選型不現(xiàn)實(shí);另外如果FPGA本身已經(jīng)是最大規(guī)模,那么更換FPGA更是不可能。這種情況跟時(shí)序不收斂要惡劣得多。

因此,在這個(gè)時(shí)候,設(shè)計(jì)者通常面臨兩種選擇:

①刪除部分設(shè)計(jì)需求,除低設(shè)計(jì)占用的FPGA資源;

②優(yōu)化邏輯電路的實(shí)現(xiàn)架構(gòu)、代碼。

對(duì)于第一種選擇,設(shè)計(jì)變更太大,造成的影響太多,而且降低FPGA資源利用率后也不能保證能夠布線成功第二種選擇是一個(gè)比較艱難的選擇,這意味著很可能要對(duì)前期已經(jīng)仿真驗(yàn)證好的代碼進(jìn)行大量修改和優(yōu)化,在進(jìn)行布局布線測(cè)試的過(guò)程中又重新仿真驗(yàn)證。

這是一個(gè)比較麻煩的過(guò)程,但是,這也印證了前期設(shè)計(jì)規(guī)劃的重要性,即要求設(shè)計(jì)者在前期就能夠預(yù)見(jiàn)到該設(shè)計(jì)可能遇到的問(wèn)題,在做邏輯電路架構(gòu)和編碼的時(shí)候注意到這種潛在的危險(xiǎn),爭(zhēng)取在概要設(shè)計(jì)和詳細(xì)設(shè)計(jì)階段就把該類(lèi)風(fēng)險(xiǎn)考慮進(jìn)去,編碼的時(shí)候養(yǎng)成良好的編碼風(fēng)格和習(xí)慣,最大程度地減少該類(lèi)事情的出現(xiàn)。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

618025 -

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43320 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4800瀏覽量

90292

原文標(biāo)題:FPGA布局布線失敗怎么辦(一)

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一招搞定PCB布局布線的可制造性設(shè)計(jì)問(wèn)題

FPGA去耦電容如何布局布線

PCB布局布線技術(shù)的發(fā)展

布局布線技術(shù)的發(fā)展

FPGA設(shè)計(jì)的塑封式布局和布線介紹

FPGA的布局布線

MCM布局布線的軟件實(shí)現(xiàn)

華秋干貨鋪 | PCB布局布線的可制造性設(shè)計(jì)

【干貨分享】PCB布局布線的可制造性設(shè)計(jì)

PCB布局布線的可制造性設(shè)計(jì)

【PCB設(shè)計(jì)】一招搞定PCB布局布線的可制造性設(shè)計(jì)問(wèn)題

PCB布局布線技巧104問(wèn)

DCDC電源的布局布線設(shè)計(jì)

FPGA布局布線的可行性 FPGA布局布線失敗怎么辦

FPGA布局布線的可行性 FPGA布局布線失敗怎么辦

評(píng)論