遲滯比較器(Hysteresis Comparator)是一種具有滯后特性的比較器,廣泛應用于模擬電路和數字電路中。它能夠消除輸入信號的噪聲,提高系統的穩定性和可靠性。

一、遲滯比較器的工作原理

- 遲滯比較器的基本概念

遲滯比較器是一種具有滯后特性的比較器,其輸出在輸入信號變化時不會立即跟隨輸入信號的變化,而是在輸入信號達到一定的閾值后才發生變化。這種滯后特性使得遲滯比較器能夠消除輸入信號的噪聲,提高系統的穩定性和可靠性。

- 遲滯比較器的工作原理

遲滯比較器的工作原理可以分為以下幾個步驟:

(1)輸入信號的獲取:遲滯比較器的輸入信號可以是模擬信號或數字信號。模擬信號需要經過模數轉換器(ADC)轉換為數字信號,數字信號可以直接輸入到比較器中。

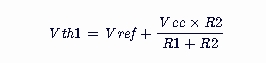

(2)閾值的設置:遲滯比較器需要設置兩個閾值,即上升閾值和下降閾值。上升閾值是輸入信號達到該值時,比較器輸出從低電平跳變到高電平;下降閾值是輸入信號低于該值時,比較器輸出從高電平跳變到低電平。這兩個閾值之間存在一定的滯后,即遲滯。

(3)輸入信號與閾值的比較:將輸入信號與上升閾值和下降閾值進行比較。當輸入信號大于上升閾值時,比較器輸出高電平;當輸入信號小于下降閾值時,比較器輸出低電平。

(4)滯后特性的實現:由于上升閾值和下降閾值之間存在一定的滯后,當輸入信號在這兩個閾值之間變化時,比較器的輸出不會立即跟隨輸入信號的變化,而是保持當前狀態,直到輸入信號達到另一個閾值。

二、遲滯比較器的設計方法

- 基本遲滯比較器的設計

基本遲滯比較器的設計主要包括以下幾個步驟:

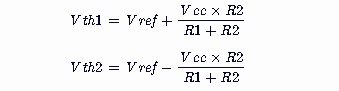

(1)選擇合適的比較器電路:根據實際應用需求,選擇合適的比較器電路,如運放比較器、差分放大器比較器等。

(2)設置閾值:根據實際應用需求,設置合適的上升閾值和下降閾值。這兩個閾值可以通過電阻分壓器、電壓參考源等方式實現。

(3)設計滯后特性:通過調整上升閾值和下降閾值之間的差值,實現所需的滯后特性。滯后差值越大,滯后特性越明顯。

(4)仿真和調試:使用電路仿真軟件對設計好的遲滯比較器進行仿真,檢查其性能是否滿足要求。根據仿真結果進行調試,直至滿足設計要求。

- 改進型遲滯比較器的設計

為了提高遲滯比較器的性能,可以采用一些改進型設計方法,如:

(1)使用差分放大器:差分放大器可以提高比較器的抗干擾能力,減小噪聲對輸出的影響。

(2)引入反饋控制:通過引入反饋控制,可以提高比較器的穩定性和可靠性。

(3)采用數字控制:將閾值和滯后差值設置為可編程參數,通過數字控制實現,方便調整和優化。

三、遲滯比較器的應用領域

遲滯比較器廣泛應用于各種電子系統中,如:

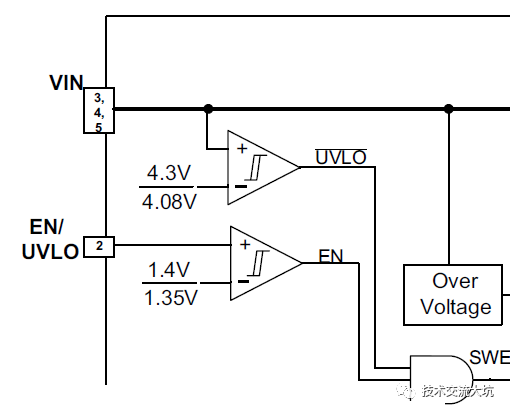

- 電源管理:在電源管理電路中,遲滯比較器可以用于過壓保護、欠壓保護等,提高電源系統的穩定性和可靠性。

- 信號處理:在信號處理電路中,遲滯比較器可以用于消除信號噪聲,提高信號的準確性和可靠性。

- 傳感器信號調理:在傳感器信號調理電路中,遲滯比較器可以用于消除傳感器信號的噪聲,提高信號的穩定性和可靠性。

- 數字邏輯電路:在數字邏輯電路中,遲滯比較器可以用于消除邏輯噪聲,提高電路的抗干擾能力。

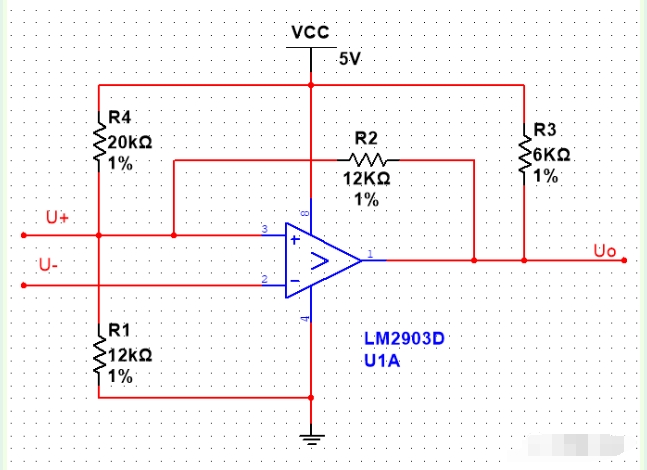

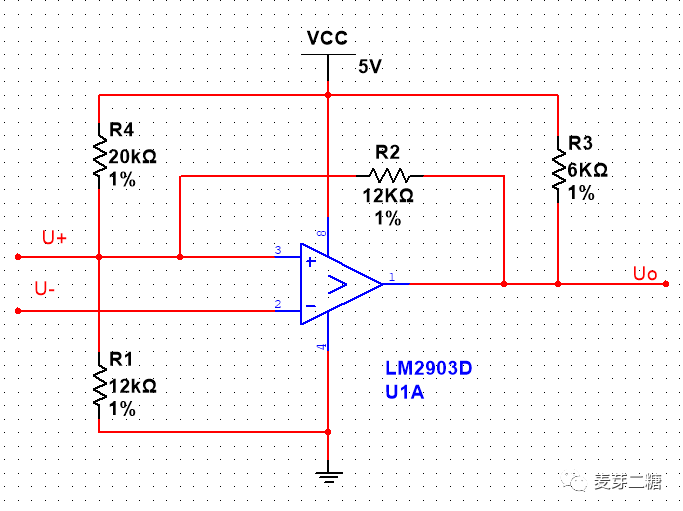

滯回比較器高低閾值計算

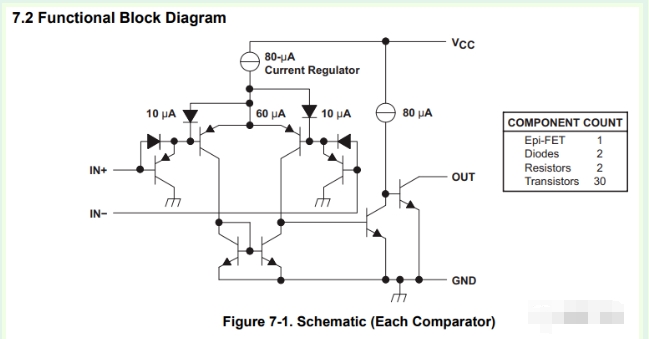

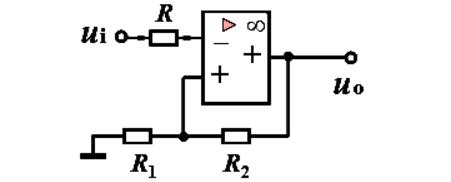

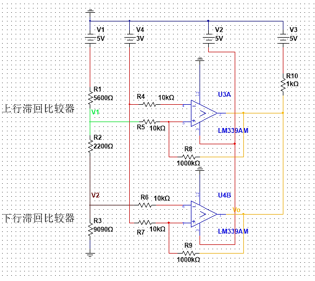

圖1是典型的滯回比較電路,也是之前項目電路中的一部分。U+端相當于一個基準電壓,但是有兩個閾值,這兩個閾值的計算我們后邊說,U-端就是我們自己輸入的信號,與普通比較器一樣,當反相輸入端U-大于正相輸入U+時,輸出端Uo輸出低電平,當反相輸入端U-小于正相輸入U+時,輸出端Uo輸出高電平,這里需要注意的一點是,LM2903是開漏輸出(如圖2所示),輸出高電平是需要外部上拉的,這對理解后邊的閾值計算有幫助。

圖1、滯回電路

圖2、LM2903功能框圖

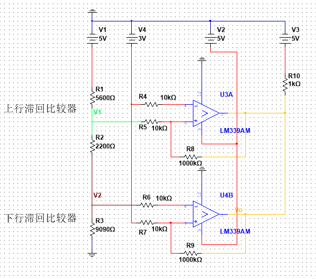

1、高閾值計算

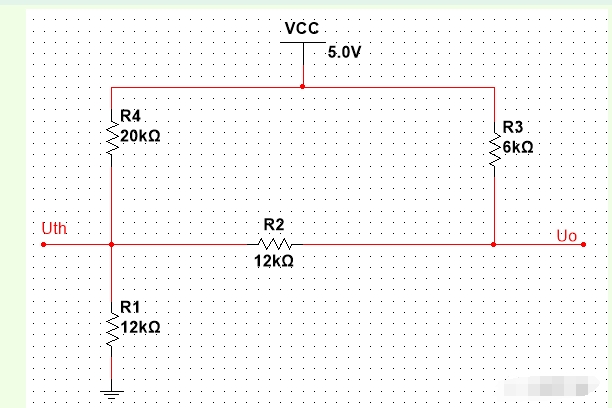

由圖1可以看出,U+的電壓與輸出端Uo的電平有關系,我們先分析高閾值情況,即假設目前Uo輸出高電平,也就是Uo端通過R3上拉到5V。注意重點來了,電路等效電阻計算,R2與R3串聯后與R4并聯,然后再與R1串聯。等效電路如下:

圖3、Uth等效電阻示意圖

R = ((R2+R3)//R4)+R1 = ((12K+6K)//20K)+12K ≈ 21.5K

Uth = 5V/R * R1 = 5V/21.5K * 12K ≈ 2.79V

也就是說當反相輸入端的電壓大于2.79V,輸出端發生電平轉換,由高電平轉換為低電平。

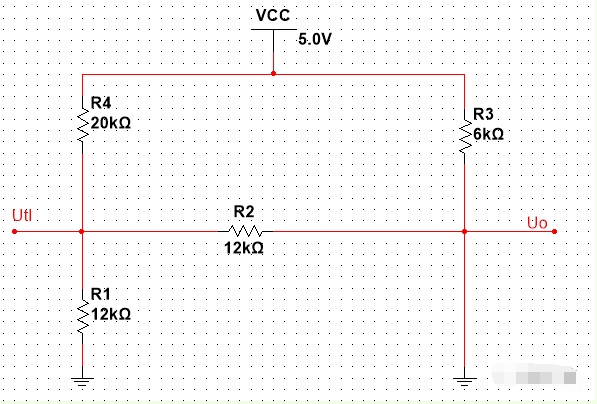

2、低閾值計算

當輸出端為低電平時,計算Utl時的電路等效電阻,R1與R2并聯,再與R4串聯。

圖4、Utl等效電阻示意圖

R = (R1//R2) + R4 = (12K//12K) + 20K = 26K

Utl = 5V/R * (R1//R2) = 5V/26K * 6K ≈ 1.15V

同樣,當反相輸入端的電壓小于1.15V時,輸出端再一次發生電平轉換,由低電平轉換為高電平。

四、優點與應用

遲滯比較器具有以下優點:

- 抗干擾能力強 :由于遲滯現象的存在,遲滯比較器能夠有效地抑制由于噪聲或信號波動引起的誤觸發。

- 穩定性好 :正反饋機制使得輸出狀態在輸入信號穿越閾值點后能夠保持穩定一段時間。

- 可調節性強 :通過調整正反饋網絡的參數(如電阻、電容等),可以改變遲滯寬度和門限電壓,從而滿足不同應用場景的需求。

遲滯比較器廣泛應用于信號處理、波形整形、噪聲抑制等領域。例如,在數字電路中,遲滯比較器常用于將模擬信號轉換為數字信號;在電源管理電路中,遲滯比較器可用于實現過壓保護和欠壓保護等功能。

-

模擬電路

+關注

關注

125文章

1591瀏覽量

103746 -

數字電路

+關注

關注

193文章

1638瀏覽量

81665 -

閾值

+關注

關注

0文章

123瀏覽量

18727 -

遲滯比較器

+關注

關注

1文章

34瀏覽量

18701 -

輸入信號

+關注

關注

0文章

472瀏覽量

12859

發布評論請先 登錄

遲滯比較器電路工作原理 滯回比較器高低閾值計算

遲滯比較器電路工作原理 滯回比較器高低閾值計算

評論