以下文章來源于Arm精選 ,作者baron

1、51單片機的中斷響應模型

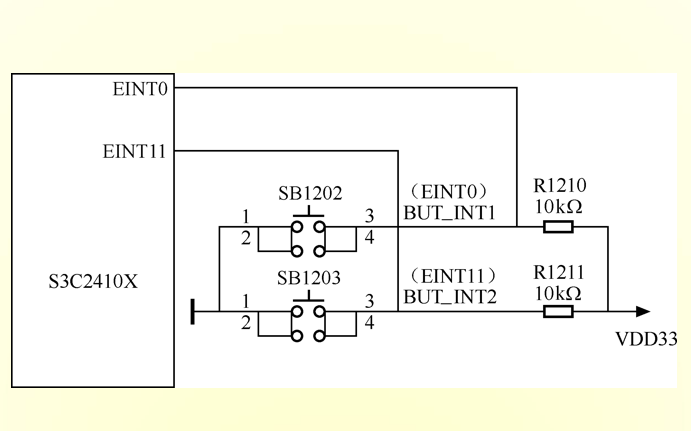

我們先回憶一下在單片機上的中斷的使用。

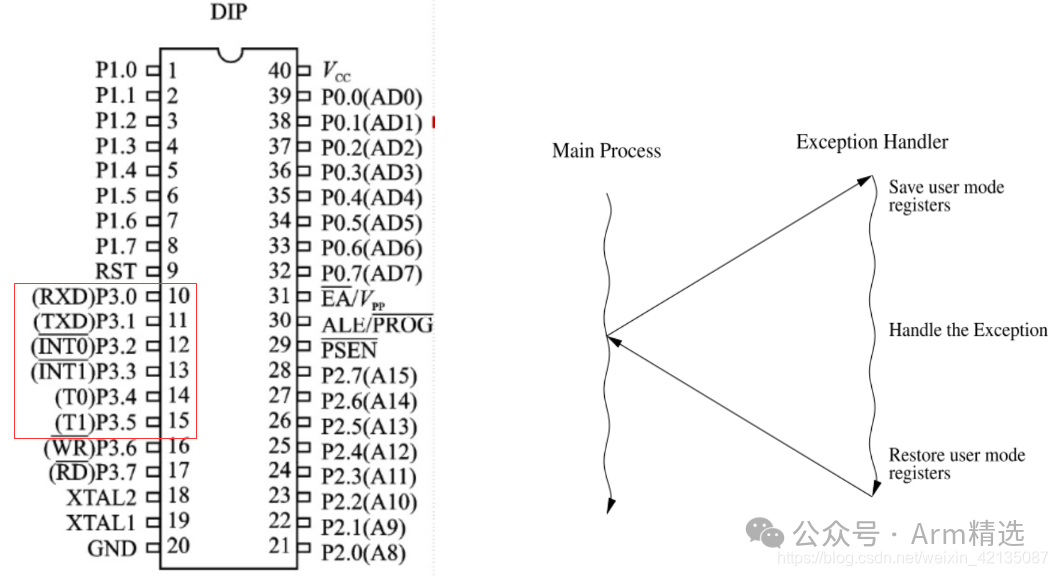

如下圖所示,左邊是51單片機的管腳圖,P3.0-P3.5是單片機對應的中斷管教,當該管教電平發生變化時,觸發cpu異常。

當cpu來了一個異常時(中斷),cpu跳轉到異常向量地址處,執行handler函數,執行完畢后再回來

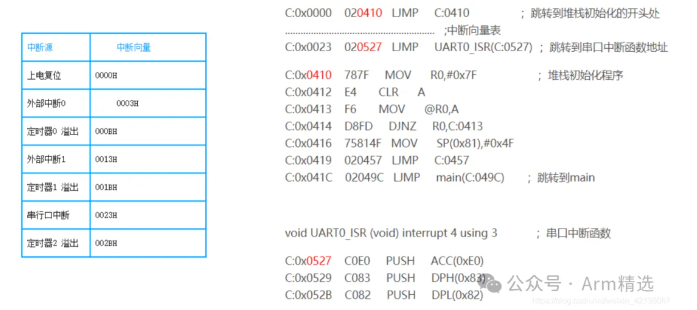

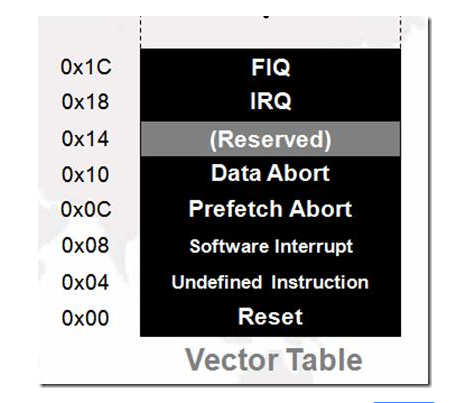

那么cpu異常時,跳轉的是哪個地址呢,其實這都是cpu出廠時設計好的。如下圖所示,左邊是cpu設計好的異常向量表基地址。右邊是軟件對異常的處理。

當來了一個uart中斷時,cpu觸發異常跳轉到0023地址處,而該地址處執行LJMP UART0_ISR指令,跳轉UART0_IAR函數去處理中斷…

2、ARM的異常有哪?

在ARMV7上,ARM異常有:RESET、swi、undef、prefetch、data abort、irq、fiq

其中RESET、swi是同步異常,其余是異步異常

在ARMV8上,ARM異常有serror、irq、fiq、Synchronous

其中Synchronous是同步異常,serror、irq、fiq是異步異常

解釋一下什么是同步異常什么是異步異常?

同步異常:軟件觸發行為、知道什么時候發生 例如:svc、smc、hyc指令觸發的都是同步異常

異步異常:軟硬件行為,不知道什么時候發生,發生時間是隨機的 例如:irq中斷觸發irq異常、fiq中斷觸發fiq異常…

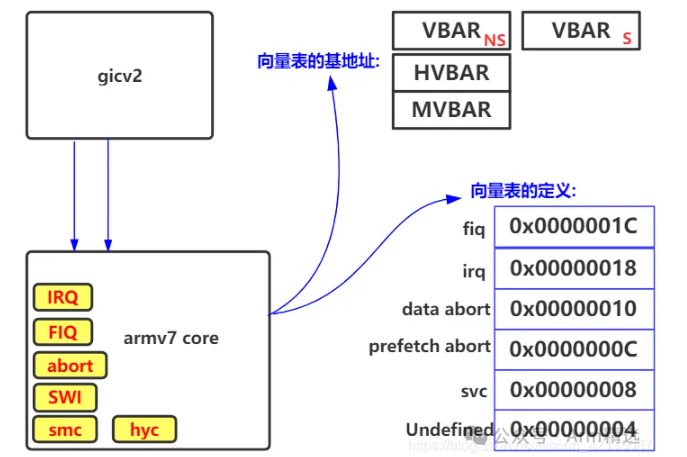

當異常發生了,ARM CORE就要跳轉到異常向量表地址處了。其實是跳轉到:異常基地址 + 異常向量表偏移處

3、ARM的異常向量表基地址

(1)、ARMV7的異常向量表基地址

主要為VBAR、HVBAR、MVBAR三個寄存器,其中VBAR是banked.

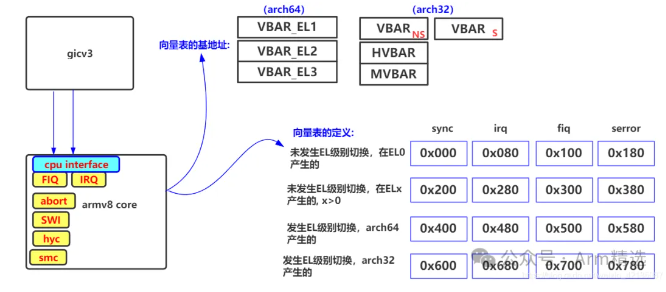

(2)、ARMV8的異常向量表基地址

主要為VBAR_EL1、VBAR_EL2、VBAR_EL3三個寄存器

4、ARM的向量表offset

(1)、armv7的異常向量表的定義

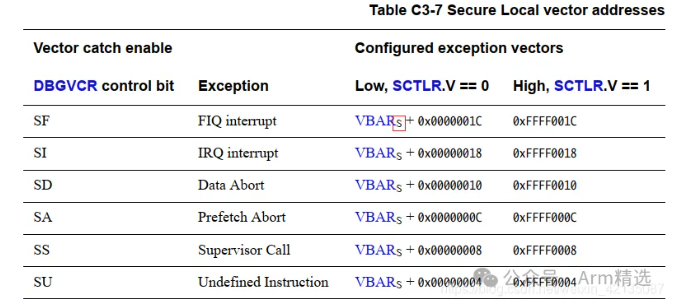

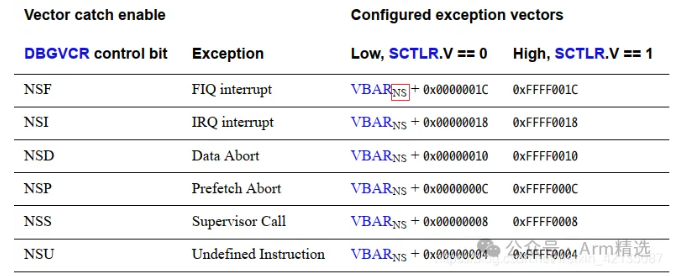

其實在armv7上有多張異常向量表,下圖分別列舉出在secure、non-secure側的兩張異常向量表

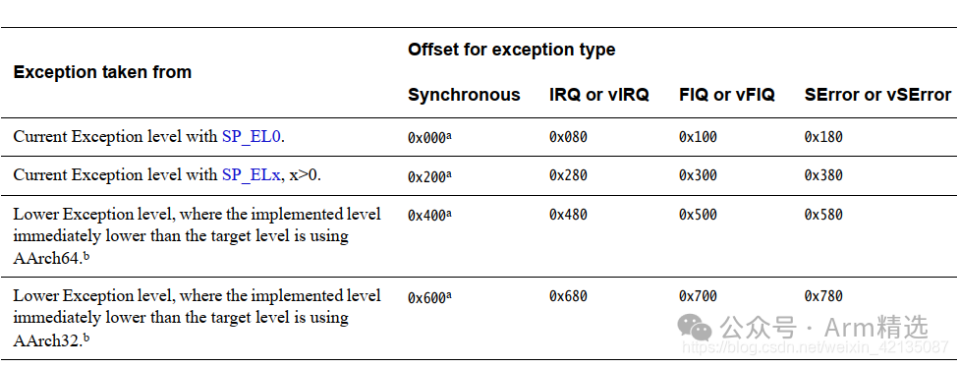

(2)、在armv8上異常向量表

實際上有四組表,每組表有四個異常入口,分別對應同步異常,IRQ,FIQ和出錯異常。

如果發生異常并不會導致exception level切換,并且使用的棧指針是SP_EL0,那么使用第一組異常向量表。

如果發生異常并不會導致exception level切換,并且使用的棧指針是SP_EL1/2/3,那么使用第二組異常向量表。

如果發生異常會導致exception level切換,并且比目的exception level低一級的exception

level運行在AARCH64模式,那么使用第三組異常向量表。

如果發生異常會導致exception level切換,并且比目的exception level低一級的exception

level運行在AARCH32模式,那么使用第四組異常向量表。

另外我們還可以看到的一點是,每一個異常入口不再僅僅占用4bytes的空間,而是占用0x80 bytes空間,也就是說,每一個異常入口可以放置多條指令,而不僅僅是一條跳轉指令

-

單片機

+關注

關注

6065文章

44946瀏覽量

648014 -

ARM

+關注

關注

134文章

9325瀏覽量

375628 -

cpu

+關注

關注

68文章

11053瀏覽量

216254 -

中斷

+關注

關注

5文章

904瀏覽量

42571

原文標題:ARM Core如何響應中斷的

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ARM9的高端異常向量基址硬件如何配置?

ARM寄存器分析以及異常處理方法

arm異常的處理方法

淺析ARM的異常分類與異常處理

ARM中斷向量表異常處理過程解析

一文弄懂ARM芯片的地址重映射

ARM未定義指令異常和SVC異常是什么意思

如何理解ARM異常、中斷和向量表

ARM體系結構所支持的異常有哪些含義和所支持的異常類型概述

嵌入式系統原理及應用教程之ARM異常中斷處理及編程的資料說明

ARM體系結構所支持的異常和具體含義

ARM interrupt-4

ARM的異常有哪些?ARM的異常向量表基地址

ARM的異常有哪些?ARM的異常向量表基地址

評論