微處理器作為計算機系統的核心部件,其內部結構復雜而精密,集成了眾多關鍵組件以實現高效的數據處理和控制功能。

一、微處理器的基本組成

微處理器的基本組成通常包括運算器、控制器、寄存器組以及內部總線等關鍵部分。這些部分相互協作,共同完成指令的執行和數據的處理。

1. 運算器

運算器是微處理器的核心部分,負責執行各種算術運算和邏輯運算。它主要由算術邏輯單元(ALU)和寄存器組成。

- 算術邏輯單元(ALU) :ALU是微處理器的計算中心,能夠執行加、減、乘、除等基本算術運算,以及與、或、非、異或等邏輯運算。ALU的設計直接影響微處理器的計算能力和效率。

- 寄存器 :寄存器用于臨時存儲ALU的計算結果和其他運算數據。這些寄存器包括累加器、狀態寄存器、程序計數器等,它們在運算過程中起著至關重要的作用。

2. 控制器

控制器是微處理器的指揮中心,負責指令的取指、譯碼和執行。它主要由指令寄存器、指令譯碼器和控制邏輯組成。

- 指令寄存器 :用于存儲從內存中讀取的指令,以便后續進行譯碼和執行。

- 指令譯碼器 :將指令寄存器中的指令譯碼為微處理器可以執行的命令,即控制信號。

- 控制邏輯 :根據譯碼結果產生一系列的控制信號,用于控制運算器、寄存器組以及其他部件的工作。

3. 寄存器組

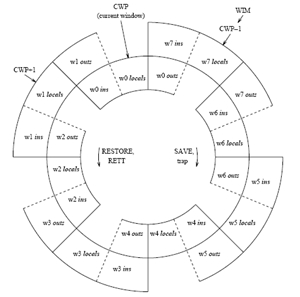

寄存器組是微處理器中用于存儲數據的重要部分,它由多個寄存器組成,包括通用寄存器和專用寄存器。

- 通用寄存器 :如累加器、變址寄存器等,用于存儲運算過程中需要頻繁訪問的數據。

- 專用寄存器 :如程序計數器(PC)、狀態寄存器等,具有特定的用途和功能。程序計數器用于指示下一條要執行的指令的地址;狀態寄存器用于記錄微處理器的運行狀態和條件碼等信息。

4. 內部總線

內部總線是微處理器內部各部分之間的數據傳輸通道,包括數據總線、地址總線和控制總線。它們共同構成了微處理器的內部通信網絡。

- 數據總線 :用于傳輸數據信號,其寬度決定了微處理器內部數據傳輸的位數。

- 地址總線 :用于傳輸地址信號,指定數據存儲或訪問的位置。

- 控制總線 :用于傳輸控制信號,如讀寫信號、中斷信號等,用于協調微處理器內部各部件的工作。

二、微處理器的內部結構設計

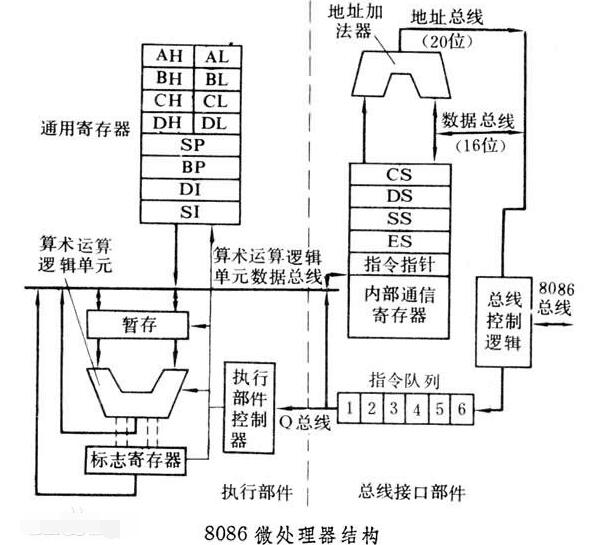

微處理器的內部結構設計通常根據其具體架構和用途而有所不同。以經典的x86架構為例,其內部結構設計可以分為執行部件(EU)和總線接口部件(BIU)兩大部分。

1. 執行部件(EU)

執行部件是微處理器中負責執行指令的核心部分,它主要由運算器、寄存器組和部分控制邏輯組成。

- 運算器 :如前所述,負責執行各種算術運算和邏輯運算。

- 寄存器組 :包括通用寄存器和專用寄存器,用于存儲數據和指令執行過程中的中間結果。

- 控制邏輯 :與控制器中的控制邏輯相似,但更側重于執行部件內部的控制和協調。

2. 總線接口部件(BIU)

總線接口部件是微處理器與外部存儲器、I/O接口等部件進行通信的橋梁,它主要負責指令的取指和數據的傳輸。

- 指令隊列 :用于暫存從內存中取出的指令流,以便后續執行。

- 地址寄存器 :用于寄存CPU要向外部發出的地址信息。

- 數據緩沖器 :起到CPU內、外傳輸數據的緩沖作用,確保數據傳輸的穩定性和可靠性。

- 總線控制邏輯 :負責控制數據總線、地址總線和控制總線的操作,實現CPU與外部部件之間的通信。

三、微處理器的運行機制

微處理器的運行機制主要包括取指、譯碼、執行和回寫四個階段。

- 取指階段 :CPU通過地址總線向內存發出地址信號,通過控制總線發出讀指令信號,從內存中取出一條指令并存儲到指令寄存器中。

- 譯碼階段 :指令譯碼器對指令寄存器中的指令進行譯碼,產生相應的控制信號。

- 執行階段 :控制邏輯根據譯碼結果控制運算器執行相應的運算或操作,同時寄存器組參與運算過程中的數據存儲和傳輸。

- 回寫階段 :將運算結果或中間結果存儲回寄存器組或內存中,為下一條指令的執行做準備。

四、微處理器的性能優化

微處理器的性能優化是半導體技術和計算機科學領域持續關注的熱點。隨著應用需求的不斷增長,對處理器性能的要求也越來越高。以下將從幾個方面繼續探討微處理器性能優化的技術和方法。

1. 指令集優化

指令集是微處理器執行操作的基礎,優化指令集可以顯著提升處理器的性能。現代微處理器通常采用復雜指令集(CISC)或精簡指令集(RISC)架構,并通過增加新的指令、改進現有指令的執行效率等方式來優化指令集。

- CISC與RISC的融合 :現代處理器往往融合了CISC和RISC的特點,采用CISC的外部指令集和RISC的內部執行方式,以提高指令的執行效率和靈活性。

- SIMD(單指令多數據)指令 :通過一條指令同時處理多個數據,可以顯著提高多媒體和圖形處理等領域的性能。

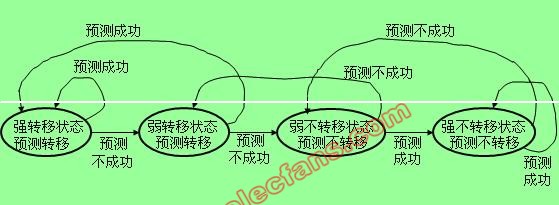

- 分支預測 :為了減少分支指令帶來的執行延遲,現代處理器采用了分支預測技術,提前預測分支的走向并預取相關指令,以提高執行效率。

2. 緩存技術

緩存是微處理器中用于存儲臨時數據的關鍵部件,它能夠顯著減少處理器對內存的訪問次數,提高數據訪問速度。緩存技術的優化主要包括以下幾個方面:

- 多級緩存 :現代處理器通常采用多級緩存結構(如L1、L2、L3緩存),以提高緩存命中率和降低訪問延遲。

- 智能緩存策略 :如LRU(最近最少使用)替換算法、偽LRU算法等,用于管理緩存中的數據,確保常用數據能夠被快速訪問。

- 預取技術 :通過分析程序的行為和訪問模式,預測未來可能需要的數據,并提前將其從內存中加載到緩存中,以減少緩存未命中的次數。

3. 并行處理技術

隨著多核處理器的普及,并行處理技術成為提高處理器性能的重要手段。并行處理技術主要包括以下幾種形式:

- 多線程 :通過在同一處理器上同時運行多個線程,實現任務級別的并行處理。現代操作系統和編程語言提供了豐富的線程管理工具和庫,使得多線程編程變得更加容易。

- 多核處理器 :每個核心都可以獨立執行指令和數據處理任務,從而實現指令級別的并行處理。多核處理器通過共享緩存和內部總線等資源,實現了高效的數據共享和通信。

- 向量處理 :通過SIMD指令集,實現單條指令對多個數據元素的并行處理,特別適用于多媒體、科學計算等領域。

4. 動態電壓與頻率調整(DVFS)

動態電壓與頻率調整技術是一種根據處理器負載情況動態調整其工作電壓和頻率的方法。在處理器負載較低時,降低其工作電壓和頻率可以顯著降低功耗和發熱量;在處理器負載較高時,提高其工作電壓和頻率可以確保足夠的處理性能。DVFS技術通過平衡功耗和性能之間的關系,實現了能耗的優化。

5. 制造工藝與封裝技術

制造工藝和封裝技術的改進也是提高微處理器性能的重要手段。隨著半導體制造工藝的不斷進步,處理器的晶體管密度不斷提高,功耗和發熱量逐漸降低,同時性能也得到提升。封裝技術的改進則使得處理器能夠更好地與其他部件集成和通信,提高了系統的整體性能和可靠性。

五、未來展望

隨著人工智能、物聯網等新興技術的快速發展,對微處理器性能的要求將越來越高。未來微處理器的發展將更加注重以下幾個方面:

- 能效比提升 :在保持高性能的同時,進一步降低功耗和發熱量,提高能效比。

- 異構計算 :結合CPU、GPU、FPGA等多種計算單元的優勢,實現更加靈活和高效的計算模式。

- 安全性增強 :加強處理器的安全防護能力,防止惡意攻擊和數據泄露。

- 定制化設計 :根據特定應用場景的需求進行定制化設計,提高處理器的針對性和性能表現。

總之,微處理器的內部結構復雜而精密,其性能優化涉及多個方面和層次。通過不斷的技術創新和改進,微處理器將繼續在各個領域發揮重要作用,推動科技進步和社會發展。

-

寄存器

+關注

關注

31文章

5427瀏覽量

123714 -

微處理器

+關注

關注

11文章

2373瀏覽量

83938 -

計算機系統

+關注

關注

0文章

290瀏覽量

24552

發布評論請先 登錄

80X86微處理器

奔騰(Pentium)微處理器介紹

SPARC微處理器綜合介紹

基于FPGA實現VLIW微處理器

PS501的內部結構圖

處理器系列之X86微處理器體系結構

微處理器內部結構介紹

微處理器內部結構介紹

評論