SR鎖存器是一種常見的數字邏輯電路,它具有保持信號狀態的功能。在設計和分析SR鎖存器時,我們需要了解其約束條件。

一、引言

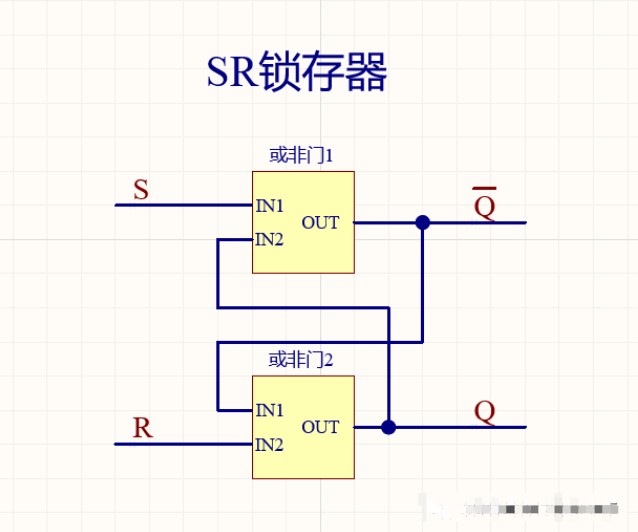

在數字邏輯電路設計中,鎖存器是一種非常重要的組件。它能夠存儲一位二進制信息,并且能夠在輸入信號發生變化時保持其輸出狀態。SR鎖存器(Set-Reset Latch)是一種基本的鎖存器類型,它由兩個交叉耦合的反相器和一個S(Set)輸入和一個R(Reset)輸入組成。本文將詳細介紹SR鎖存器的約束條件,以及如何根據這些條件進行設計和分析。

二、SR鎖存器的基本結構

- 反相器

反相器是一種基本的數字邏輯門,它的作用是將輸入信號取反。反相器的邏輯表達式為:

Q = NOT(D)

其中,Q是輸出,D是輸入。

- 交叉耦合

在SR鎖存器中,兩個反相器的輸出分別連接到另一個反相器的輸入,形成交叉耦合。這種結構使得SR鎖存器具有存儲一位二進制信息的能力。

- S輸入和R輸入

S輸入和R輸入是SR鎖存器的兩個控制輸入。當S輸入為高電平時,鎖存器的輸出Q被設置為高電平;當R輸入為高電平時,鎖存器的輸出Q被重置為低電平。

三、SR鎖存器的約束條件

- 競爭條件

競爭條件是SR鎖存器設計中需要特別注意的問題。當S輸入和R輸入同時為高電平時,鎖存器的輸出Q將處于不確定狀態。這是因為兩個反相器的輸出相互影響,導致它們無法穩定在一個確定的狀態。為了避免競爭條件,我們需要確保S輸入和R輸入不會同時為高電平。

- 建立時間和保持時間

建立時間和保持時間是鎖存器設計中的重要參數。建立時間是指在時鐘信號的上升沿之前,輸入信號需要保持穩定的最小時間。保持時間是指在時鐘信號的上升沿之后,輸入信號需要保持穩定的最小時間。為了保證鎖存器的正常工作,我們需要確保輸入信號滿足建立時間和保持時間的要求。

閾值電壓是SR鎖存器中的一個重要參數,它決定了鎖存器在不同輸入條件下的輸出狀態。當S輸入或R輸入的電平高于閾值電壓時,鎖存器的輸出Q將被設置或重置。為了保證鎖存器的穩定工作,我們需要選擇合適的閾值電壓。

- 噪聲容限

噪聲容限是衡量鎖存器對噪聲干擾的抵抗能力的一個重要參數。在實際應用中,輸入信號可能會受到噪聲干擾,導致鎖存器的輸出Q出現錯誤。為了提高鎖存器的可靠性,我們需要設計具有較高噪聲容限的鎖存器。

- 功耗

功耗是鎖存器設計中需要考慮的另一個重要因素。在現代電子系統中,功耗是一個關鍵的指標,因為它直接影響到系統的能效和壽命。為了降低功耗,我們可以采用低功耗設計技術,如使用CMOS工藝、優化電路結構等。

四、SR鎖存器的設計方法

- 選擇合適的工藝

選擇合適的工藝是設計SR鎖存器的第一步。不同的工藝具有不同的特性,如閾值電壓、噪聲容限等。我們需要根據實際應用需求,選擇最適合的工藝。

- 設計電路結構

在設計SR鎖存器的電路結構時,我們需要考慮競爭條件、建立時間和保持時間等因素。通過合理布局和優化電路結構,我們可以提高鎖存器的性能和可靠性。

- 仿真和驗證

在設計過程中,仿真和驗證是非常重要的環節。通過仿真,我們可以預測鎖存器在不同條件下的性能,如功耗、噪聲容限等。驗證則是確保鎖存器滿足設計要求的關鍵步驟。

- 優化設計

根據仿真和驗證的結果,我們可以對設計進行優化。優化的目標是提高鎖存器的性能,降低功耗,提高可靠性等。

五、SR鎖存器的應用

SR鎖存器在數字邏輯電路設計中有廣泛的應用,如存儲器、寄存器、計數器等。通過合理設計和優化,SR鎖存器可以滿足不同應用場景的需求。

-

反相器

+關注

關注

6文章

316瀏覽量

44109 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

16058 -

輸入信號

+關注

關注

0文章

472瀏覽量

12861

發布評論請先 登錄

基本rs觸發器的約束條件

sr鎖存器約束條件怎樣得出的

sr鎖存器約束條件怎樣得出的

評論