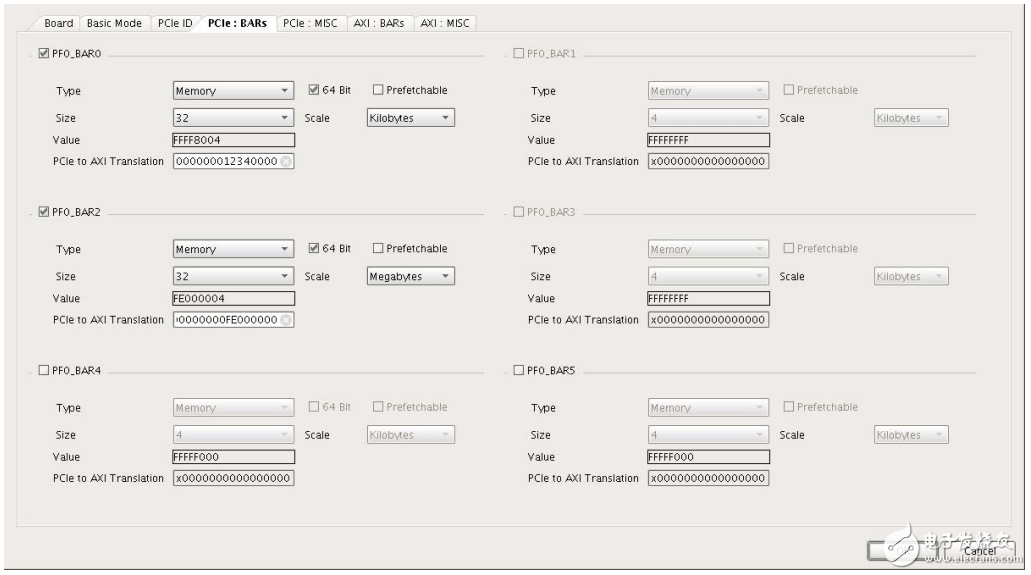

UltraScale系列芯片包含PCIe的Gen3 Integrated Block IP核在內(nèi)的多種不同功能的IP核都會(huì)有一頁設(shè)置為PCIe:BARs,設(shè)置IP核的Base address register 的相關(guān)參數(shù),如圖1所示:

圖1 PCIe:BARs 配置圖

一般來說在FPGA中使用PCIe核都是Endpoint mode,我們的PC主機(jī)端是Rootpoint mode,一般會(huì)有一個(gè)Root Complex的混合管理器,來管理接入PCIe總線的端點(diǎn)設(shè)備。對(duì)于PC機(jī)來說,當(dāng)PC機(jī)識(shí)別該P(yáng)CIe設(shè)備后便會(huì)識(shí)別到BAR n相對(duì)應(yīng)的基地址和地址空間(不過該基地址是PC機(jī)的Root Complex主動(dòng)分配的,還是PCIe設(shè)備內(nèi)部固定的還有疑問)。設(shè)別基本配置信息后,PC機(jī)便可以對(duì)PCIe的內(nèi)存空間進(jìn)行讀寫操作了。

而PCIe IP核本身能夠引出AXI總線接口,該AXI接口是memory map 型的,所以就肯定存在自己的地址空間,本文所提的PCIe to AXI Translation便是PCIe的地址空間到AXI的地址空間的轉(zhuǎn)換。

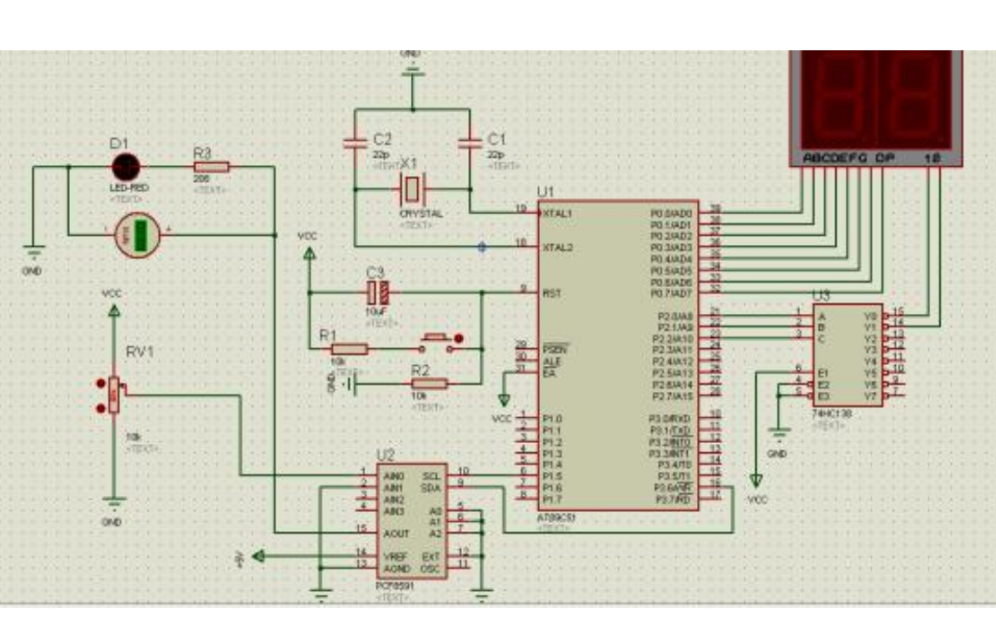

這里就圖1中的BAR0來說明下PCIe to AXI Translation的轉(zhuǎn)換過程。BAR0的配置為:64bit數(shù)據(jù)位寬、32kilobytes地址范圍、PCIe to AXI Translation為0x0000000012340000。此時(shí)的PCIe IP核的BAR0是拓展連接到外部的AXI總線的,該總線連接到另外一個(gè)DDR4 MIG IP核,如圖2所示。圖中重點(diǎn)標(biāo)注的AXI總線便是PCIe核引出的AXI總線。

圖2 PCIe核拓展AXI接口

假設(shè)PC機(jī)設(shè)別到的PCIe BAR0的基地址為0x0000000000000000,在FPGA內(nèi)部DDR4的AXI基地址為0x0000000012340000。現(xiàn)在PC機(jī)想要往FPGA內(nèi)部的DDR4地址空間的0x000000001234000F地址寫入數(shù)據(jù),那么PC機(jī)應(yīng)該對(duì)PICe內(nèi)存空間的0x000000000000000F寫入數(shù)據(jù),然后由PCIe to AXI Translation的關(guān)系,便會(huì)把0x000000000000000F轉(zhuǎn)換到0x000000001234000F上實(shí)現(xiàn)對(duì)AXI總線的操作,進(jìn)而實(shí)現(xiàn)對(duì)DDR4的寫入操作。圖3可以看出具體的轉(zhuǎn)換操作。

圖3 PCIe to AXI Translation 轉(zhuǎn)換圖

既然有PCIe to AXI Translation,那相應(yīng)的也有AXI to PCIe Translation了,圖4是AXI to PCIe Translation的轉(zhuǎn)換圖,不過這種操作應(yīng)用不多,原理也跟PCIe to AXI Translation差不多,這就不再贅述了。

圖4 AXI to PCIe Translation 轉(zhuǎn)換圖

-

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83191 -

AXI

+關(guān)注

關(guān)注

1文章

128瀏覽量

16711

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用rt_malloc申請(qǐng)內(nèi)存空間失敗,顯示沒有內(nèi)存怎么解決?

請(qǐng)教高手,安卓智能手機(jī)的內(nèi)存空間不夠問題

Linux內(nèi)存點(diǎn)滴 用戶進(jìn)程內(nèi)存空間

請(qǐng)問66ak2h內(nèi)存空間申請(qǐng)如何實(shí)現(xiàn)

在MPFS2文件之前預(yù)留內(nèi)存空間的最佳方法是什么?

DM8127使用SWOSD_TI_alloc()分配內(nèi)存空間怎么加大?

如何與ctypes庫(kù)創(chuàng)建的數(shù)組共享內(nèi)存空間?

stm32 使用u*** host庫(kù)占用內(nèi)存空間很大!!!

RTThread的動(dòng)態(tài)內(nèi)存空間該如何去分配呢

在stm32f429上的輕量級(jí)算法運(yùn)行時(shí)所用的內(nèi)存空間要怎么得到呢?

C51程序中兩種對(duì)內(nèi)存空間地址寫數(shù)據(jù)的方法說明

一文詳解PCIe內(nèi)存空間到AXI內(nèi)存空間的轉(zhuǎn)換

一文詳解PCIe內(nèi)存空間到AXI內(nèi)存空間的轉(zhuǎn)換

評(píng)論