ARM處理器的寄存器組織是其核心架構(gòu)的重要組成部分,對(duì)于理解ARM處理器的運(yùn)行機(jī)制和性能特點(diǎn)具有重要意義。以下是對(duì)ARM處理器寄存器組織及功能的詳細(xì)闡述。

一、ARM處理器的寄存器概述

ARM處理器通常包含多個(gè)寄存器,這些寄存器用于存儲(chǔ)數(shù)據(jù)、地址和處理器狀態(tài)等信息。根據(jù)功能和用途的不同,ARM處理器的寄存器可以分為通用寄存器和狀態(tài)寄存器兩大類。通用寄存器用于保存數(shù)據(jù)和地址,而狀態(tài)寄存器則用于標(biāo)識(shí)或設(shè)置處理器的工作模式或工作狀態(tài)等功能。

二、通用寄存器

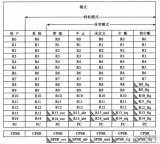

ARM處理器中的通用寄存器數(shù)量較多,通常為31個(gè)(R0-R30),這些寄存器都是32位的,用于存儲(chǔ)數(shù)據(jù)和地址。通用寄存器可以根據(jù)其分組與否和使用目的進(jìn)一步細(xì)分為未分組寄存器、分組寄存器和程序計(jì)數(shù)器(PC)三類。

1. 未分組寄存器(R0-R7)

未分組寄存器包括R0-R7,這些寄存器在所有處理器模式下都指向同一個(gè)物理寄存器。它們沒(méi)有被系統(tǒng)用作特殊用途,因此在任何可采用通用寄存器的應(yīng)用場(chǎng)合都可以使用。然而,在中斷和異常處理進(jìn)行工作模式轉(zhuǎn)換時(shí),由于不同的處理器工作模式均使用相同的物理寄存器,可能會(huì)造成寄存器中數(shù)據(jù)的破壞。因此,在程序設(shè)計(jì)時(shí)需要注意這一點(diǎn)。

2. 分組寄存器(R8-R14)

分組寄存器包括R8-R14,這些寄存器每一次所訪問(wèn)的物理寄存器與處理器當(dāng)前的工作模式有關(guān)。具體來(lái)說(shuō):

- 對(duì)于R8-R12來(lái)說(shuō),每個(gè)寄存器對(duì)應(yīng)兩個(gè)不同的物理寄存器。一組用于除FIQ(快速中斷)模式外的所有處理器模式(通常稱為用戶模式或系統(tǒng)模式),而另一組則專門用于FIQ模式。這樣的結(jié)構(gòu)設(shè)計(jì)有利于加快FIQ的處理速度,因?yàn)镕IQ模式常被用來(lái)處理一些時(shí)間緊急的任務(wù),如DMA處理。

- 對(duì)于R13和R14來(lái)說(shuō),每個(gè)寄存器對(duì)應(yīng)6個(gè)不同的物理寄存器。其中的一個(gè)是用戶模式和系統(tǒng)模式共用的;而另外5個(gè)分別用于5種異常模式(管理模式、數(shù)據(jù)訪問(wèn)中止模式、未定義指令中止模式、普通中斷模式和快速中斷模式)。這種設(shè)計(jì)使得每種異常模式都有自己獨(dú)立的物理寄存器來(lái)保存堆棧指針(R13)和返回地址(R14),從而保證了異常處理時(shí)的數(shù)據(jù)完整性和程序的可恢復(fù)性。

3. 程序計(jì)數(shù)器(PC,R15)

程序計(jì)數(shù)器(PC)是ARM處理器中的一個(gè)特殊寄存器,用于控制程序中指令的執(zhí)行順序。正常運(yùn)行時(shí),PC指向CPU運(yùn)行的下一條指令。每次取指后PC的值會(huì)自動(dòng)修改指向下一條指令,從而保證了指令按照一定的順序執(zhí)行。此外,PC還可以被用作通用寄存器來(lái)存儲(chǔ)數(shù)據(jù)和地址,但需要注意其使用限制和可能產(chǎn)生的不可預(yù)知結(jié)果。

三、狀態(tài)寄存器

狀態(tài)寄存器用于標(biāo)識(shí)或設(shè)置處理器的工作模式或工作狀態(tài)等功能。ARM處理器中通常包含多個(gè)狀態(tài)寄存器,其中最重要的是當(dāng)前程序狀態(tài)寄存器(CPSR)和備份程序狀態(tài)寄存器(SPSRs)。

1. 當(dāng)前程序狀態(tài)寄存器(CPSR)

CPSR是一個(gè)32位的寄存器,可以在任何處理器模式下被訪問(wèn)。它包含了ALU(算術(shù)邏輯單元)狀態(tài)標(biāo)志的備份、中斷禁止位、當(dāng)前處理器模式以及其他狀態(tài)和控制信息。CPSR中的條件碼標(biāo)志(N、Z、C、V)用于指示算術(shù)運(yùn)算的結(jié)果狀態(tài)(如負(fù)數(shù)、零、進(jìn)位、溢出等),這些標(biāo)志可以被用來(lái)控制程序的流程。此外,CPSR中的中斷禁止位用于控制中斷的響應(yīng)和屏蔽。

2. 備份程序狀態(tài)寄存器(SPSRs)

SPSRs是一組用于異常處理的備份程序狀態(tài)寄存器。在ARM處理器中,通常有5個(gè)SPSRs(SPSR_svc、SPSR_abt、SPSR_und、SPSR_irq、SPSR_fiq),分別對(duì)應(yīng)于5種異常模式。當(dāng)異常發(fā)生時(shí),CPSR的當(dāng)前狀態(tài)會(huì)被保存到相應(yīng)的SPSR中,以便在異常處理完成后恢復(fù)處理器的狀態(tài)。這種設(shè)計(jì)保證了異常處理時(shí)的數(shù)據(jù)完整性和程序的可恢復(fù)性。

四、寄存器組織的功能與優(yōu)勢(shì)

ARM處理器的寄存器組織具有以下功能和優(yōu)勢(shì):

- 提高執(zhí)行效率 :通過(guò)多級(jí)流水線和高效的指令執(zhí)行機(jī)制,ARM處理器能夠充分利用寄存器資源來(lái)加速指令的執(zhí)行。

- 降低功耗 :精簡(jiǎn)的指令集和高效的執(zhí)行效率使得ARM處理器在保持高性能的同時(shí)能夠降低功耗。

- 增強(qiáng)靈活性 :未分組寄存器和分組寄存器的設(shè)計(jì)使得ARM處理器能夠適應(yīng)不同的應(yīng)用場(chǎng)景和工作模式需求。

- 提高數(shù)據(jù)安全性 :通過(guò)備份程序狀態(tài)寄存器和異常處理機(jī)制,ARM處理器能夠在異常發(fā)生時(shí)保護(hù)數(shù)據(jù)完整性和程序的可恢復(fù)性。

- 支持多任務(wù)處理 :通過(guò)切換不同的處理器模式和寄存器組,ARM處理器能夠支持多任務(wù)處理和并發(fā)執(zhí)行。

綜上所述,ARM處理器的寄存器組織是其核心架構(gòu)的重要組成部分,對(duì)于提高執(zhí)行效率、降低功耗、增強(qiáng)靈活性、提高數(shù)據(jù)安全性以及支持多任務(wù)處理等方面都具有重要作用。

-

寄存器

+關(guān)注

關(guān)注

31文章

5401瀏覽量

122768 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2283瀏覽量

95820 -

ARM處理器

+關(guān)注

關(guān)注

6文章

361瀏覽量

42348

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ARM處理器及ARM處理器工作模式

ARM處理器及ARM處理器工作模式

詳解ARM處理器寄存器與運(yùn)行模式

ARM處理器的寄存器一共包括哪些呢

ARM微處理器的編程模型

ARM寄存器詳解

多寄存器組網(wǎng)絡(luò)處理器上的寄存器分配技術(shù)

ARM處理器的寄存器組織及功能

ARM處理器的寄存器組織及功能

評(píng)論