前端總線(Front Side Bus,FSB)是計算機中處理器與內存、北橋芯片之間數據傳輸的通道。在計算機系統中,前端總線頻率是衡量數據傳輸速率的一個重要指標。內存則是計算機的主要存儲部件,用于臨時存儲CPU需要處理的數據和指令。

1. 前端總線頻率的定義

前端總線頻率是指處理器與主板上其他組件(如內存、北橋芯片)之間數據傳輸的速率,通常以MHz(兆赫茲)為單位。前端總線頻率越高,數據傳輸速度越快,處理器與內存之間的通信效率也就越高。

2. 內存的定義

內存,也稱為隨機存取存儲器(Random Access Memory,RAM),是計算機的主要存儲部件之一。它用于臨時存儲CPU需要處理的數據和指令。內存的容量、速度和類型都會影響計算機的性能。

3. 前端總線頻率與內存的關系

3.1 數據傳輸速率

前端總線頻率和內存的頻率決定了數據在處理器和內存之間的傳輸速率。如果前端總線頻率較低,即使內存的速度很快,數據傳輸速率也會受到限制。

3.2 同步與異步

在早期的計算機系統中,內存的頻率通常與前端總線頻率相同,這種設計被稱為同步前端總線(Synchronous FSB)。隨著技術的發展,內存的頻率可以高于或低于前端總線頻率,這種設計被稱為異步前端總線(Asynchronous FSB)。

3.3 內存帶寬

內存帶寬是指內存在單位時間內能夠處理的數據量。內存帶寬的計算公式為:帶寬 = 內存頻率 × 總線寬度 × 數據位數。前端總線頻率的提高可以增加內存帶寬,從而提高數據傳輸速率。

3.4 延遲

內存的延遲是指從處理器發出讀取或寫入請求到內存響應的時間。前端總線頻率的提高可以降低內存的延遲,從而提高計算機的響應速度。

4. 前端總線頻率與內存的匹配

為了充分發揮計算機的性能,前端總線頻率和內存頻率需要匹配。如果內存頻率低于前端總線頻率,會導致數據傳輸瓶頸,影響計算機的性能。反之,如果內存頻率過高,可能會導致系統不穩定。

5. 前端總線頻率的發展趨勢

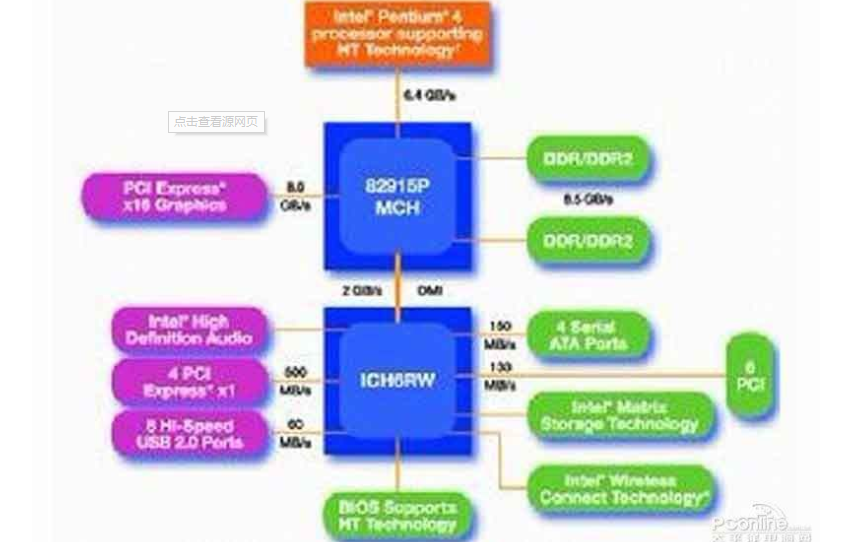

隨著計算機技術的發展,前端總線的概念逐漸被其他技術所取代,如HyperTransport、PCI Express等。這些技術提供了更高的數據傳輸速率和更低的延遲,從而提高了計算機的性能。

6. 內存的發展趨勢

內存技術也在不斷發展,如DDR、DDR2、DDR3、DDR4等。新一代的內存技術具有更高的頻率、更大的容量和更低的功耗,從而提高了計算機的性能。

7. 結論

前端總線頻率和內存之間的關系對于計算機性能有著直接的影響。為了充分發揮計算機的性能,需要合理匹配前端總線頻率和內存頻率。隨著技術的發展,前端總線和內存技術都在不斷進步,為計算機性能的提升提供了可能。

-

計算機

+關注

關注

19文章

7638瀏覽量

90373 -

內存

+關注

關注

8文章

3115瀏覽量

75070 -

頻率

+關注

關注

4文章

1559瀏覽量

60141 -

前端總線

+關注

關注

0文章

11瀏覽量

6952

發布評論請先 登錄

前端總線頻率,Front Side Bus(FSB)

什么是CPU的緩存/前端總線(FSB)頻率

前端總線頻率的詳細資料說明

前端總線頻率和內存的關系

前端總線頻率和內存的關系

評論