1 引言

運算放大器作為模擬系統(tǒng)和混合信號系統(tǒng)中的一個重要電路單元,廣泛應(yīng)用于數(shù)/模與模/ 數(shù)轉(zhuǎn)換器、有源濾波器、波形發(fā)生器和視頻放大器等各種電路中。伴隨著每一代CMOS 工藝 的發(fā)展,電源電壓和晶體管溝道長度的持續(xù)減小,不斷為運算放大器的設(shè)計提出了復(fù)雜的課 題。在A/D 轉(zhuǎn)換器中,運算放大器是最關(guān)鍵的部件。比如,有限增益、帶寬和有限壓擺率 等運算放大器的非理想特性都會造成積分器中的電荷轉(zhuǎn)移不完全,從而引起A/D轉(zhuǎn)換器的非線性。與單端輸出的運算放大器相比,全差分運算放大器能提供更大的輸出電壓擺幅,并具 有不易受共模噪聲影響、更高的線性度、減少偶次諧波干擾以及偏置電路更簡單等優(yōu)點。

本文從分析和優(yōu)化運算放大器的參數(shù)出發(fā),實現(xiàn)了一款高性能CMOS 全差分運算放大器 的設(shè)計,其主要性能指標要求為:開環(huán)增益大于70dB,單位增益帶寬大于80 MHz,轉(zhuǎn)換速 率大于160 V/μs。

2 高增益CMOS 全差分運算放大器設(shè)計

2.1 結(jié)構(gòu)選擇與分析

常見的全差分運算放大器的結(jié)構(gòu)有套筒式共源共柵、折疊式共源共柵和兩級運放等。在 兩級運放結(jié)構(gòu)中,次極點頻率由負載電容CL 決定,使速度受到限制,帶寬較小,且功耗較 大,電源抑制比和共模抑制比也較差。與套筒式結(jié)構(gòu)相比,折疊式共源共柵運放的輸出電壓 擺幅要大一些,但這是以較大的功耗和噪聲、較低的電壓增益和極點頻率為代價得到的[2]。套 筒式共源共柵是各種不同運放結(jié)構(gòu)*耗最低的一種,其增益也較高,可和普通的兩級運放 相比。從本設(shè)計的應(yīng)用出發(fā),決定采用套筒式共源共柵結(jié)構(gòu)來設(shè)計全差分運算放大器。

2.2 套筒式共源共柵運算放大器

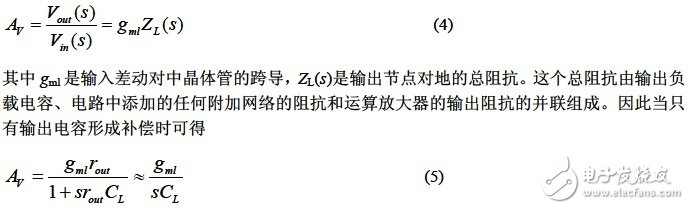

采用的套筒式共源共柵運算放大器主體結(jié)構(gòu)如圖1 所示。其中,M1、M2、M3 和M4 組成有源負載,其阻值很大,可提高運算放大器的增益。M7 和M8 是NMOS 差分輸入對,用 于把輸入電壓變?yōu)?a href="http://m.xsypw.cn/tags/電流/" target="_blank">電流;M7、M8 和M5、M6 一起組成差分式共源共柵結(jié)構(gòu)。M9 用來產(chǎn)生 尾電流以抑制輸入共模電平的變化對M7 和M8 的工作及輸出電平的影響。Vb1、Vb2 和Vb3 為 三個偏置電壓,VCMFB 為共模反饋電路產(chǎn)生的控制電壓。

2.3 共模反饋電路

全差分運算放大器中通常需要一個共模反饋電路(CMFB),使受控的共模輸出電壓值接近 于某個特定值(通常約為電源電壓的一半)[4]。CMFB 分連續(xù)時間和開關(guān)電容兩種。由于本文設(shè) 計的運放用在全差分開關(guān)電容電路中,加之連續(xù)時間CMFB 具有限制差模輸出信號幅度、增 加差模負載和增加靜態(tài)功耗等缺點[5-6],因此采用開關(guān)電容CMFB,其實際結(jié)構(gòu)如圖2 所示。

圖2 中的C1=C2,C3=C4,clk1 和clk2 為兩相不交疊時鐘信號,Vo-和Vo+接運放輸出電 壓,VCMFB 為該CMFB 產(chǎn)生的調(diào)節(jié)電壓,Vcmref 代表期望的輸出共模電壓,Vbias 是使運放輸出 共模電壓剛好等于期望值時的電流源柵極偏壓。當clk2 為高電平時,C3 和C4 預(yù)充電到 Vcmref-Vbias。當clk1 為高電平時,C1 和C3 并聯(lián),C2 和C4 并聯(lián),存儲在C3 和C4 上的電荷 將發(fā)生轉(zhuǎn)移,最終在C1 與C2 之間產(chǎn)生一個DC 補償電壓,疊加到運放的輸出共模電壓上, 從而保證運算放大器實際輸出共模電壓保持在預(yù)期值附近。

3 電路參數(shù)分析

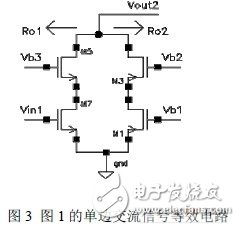

在圖 1 所示的電路中,由于兩條支路對稱,所以當輸入差模交流信號時,M9 的漏極電位 保持恒定,于是可認為M9 的漏極交流接地,由此得到圖1 的單邊交流信號等效電路,如圖3 所示。

3.1 開環(huán)直流增益

如圖3 所示,單邊增益等于輸入管的跨導(dǎo)乘以輸出電阻。輸出電阻等于從輸出節(jié)點看進去的兩個共源共柵結(jié)構(gòu)輸出電阻的并聯(lián),因此有

上式指出了具體某個晶體管對電路直流增益的貢獻,因此是晶體管參數(shù)調(diào)整的總體指導(dǎo) 依據(jù)。此外,從圖1 可以看到,M5、M6、M7 和M8 處在信號通路上,故要保證其電容值最 小,因此在改變參數(shù)以增大直流增益的過程中,盡量保持最小尺寸不變而進行寬長比的整體 變化。而PMOS 管M1、M2、M3 和M4 對信號的影響小得多,增大其尺寸可非常有效地改變 直流增益。

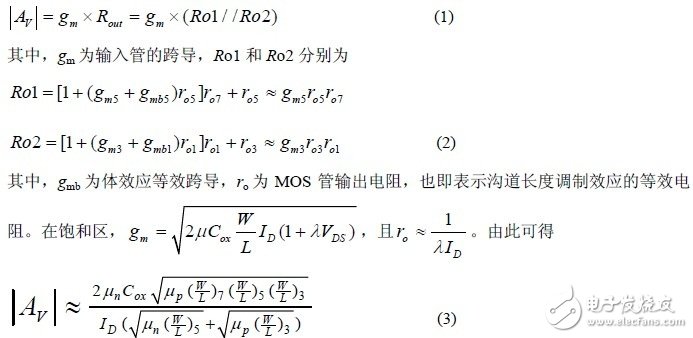

3.2 單位增益帶寬

套筒式共源共柵運算放大器的小信號傳遞函數(shù)可寫為

由(3)式和(10)式可知,增加輸入差分管的W/L、減小負載電容是提高單位增益帶寬的有效方法。

3.3 轉(zhuǎn)換速率和建立時間

運算放大器在額定負載及輸入階躍大信號時,輸出電壓上升段(或下降段)線性部分的斜率 稱為轉(zhuǎn)換速率,也叫壓擺率。圖1 所示運放Vout1-Vout2 的壓擺率SR=ID9/CL。本設(shè)計中負載電 容CL 為2.6 pF,轉(zhuǎn)換速率要求大于160 V/μs,因此ID9 至少為0.42 mA。

建立時間指當運算放大器構(gòu)成閉環(huán)負反饋時,在限定輸出負載并輸入階躍信號的條件下, 輸出電壓從階躍信號輸入時起至輸出電壓上升到穩(wěn)定值的誤差容限內(nèi)所需的時間。它分為線 性建立和非線性建立兩個不同的階段。線性建立階段指輸入差分小信號時,運算放大器的輸 出由閉環(huán)作用控制的階段。單位增益帶寬越大,線性建立時間越短。非線性建立階段是指當 輸入差分大信號時,運算放大器的輸出波形由轉(zhuǎn)換速率決定的階段,因此可通過適當增加尾 電流來縮短這段時間。

3.4 共模輸入范圍

輸入共模電壓范圍定義為當差動信號為零時,能維持電路工作在飽和區(qū)的共模電平范圍。 對于理想差分運算放大器,輸入共模電壓時輸出應(yīng)為零。而實際的差分運算放大器,電路既 不可能完全對稱,尾電流源的輸出阻抗也不可能為無窮大。因而,當輸入共模電壓時輸出不 為零;甚至當輸入共模電壓超出某一范圍時,運算放大器就不能再對差模信號進行正常放大。 從圖1 可以看到,輸入共模電壓VIC 有:

4 仿真結(jié)果

基于 SMIC 0.35 μm CMOS 工藝,在Cadence Spectre 模擬器上對該CMOS 運算放大器進 行仿真。結(jié)果如表1 所示。圖4 給出了運算放大器的頻率響應(yīng)特性曲線。

5 結(jié)論

采用簡單的套筒式共源共柵結(jié)構(gòu),通過分析決定開環(huán)直流增益、單位增益帶寬、轉(zhuǎn)換速 率和建立時間等主要性能參數(shù)的各種因素,實現(xiàn)了一款性能優(yōu)良的全差分運算放大器。Spectre 仿真表明,運算放大器的各項性能指標均達到設(shè)計要求,可應(yīng)用于高精度音頻Σ-Δ A/D 轉(zhuǎn)換 器中。

-

CMOS

+關(guān)注

關(guān)注

58文章

6001瀏覽量

238317 -

運算放大器

+關(guān)注

關(guān)注

216文章

5683瀏覽量

176094 -

共源共柵

+關(guān)注

關(guān)注

0文章

25瀏覽量

10505

發(fā)布評論請先 登錄

一種低壓低功耗CMOS折疊-共源共柵運算放大器的設(shè)計

一種高增益CMOS全差分運算放大器的設(shè)計

增益增強共源共柵放大器的設(shè)計

基于增益提高技術(shù)的高速CMOS運算放大器的設(shè)計與實現(xiàn)

用結(jié)構(gòu)簡單的套筒式共源共柵運算放大器實現(xiàn)高增益、高單位增益帶寬和低功耗的設(shè)計

用結(jié)構(gòu)簡單的套筒式共源共柵運算放大器實現(xiàn)高增益、高單位增益帶寬和低功耗的設(shè)計

評論