RS觸發器(Reset-Set觸發器)是一種基本的數字邏輯電路,用于存儲一位二進制信息。它由兩個輸入端(R和S)和一個輸出端(Q)組成,其中R代表復位(Reset),S代表置位(Set)。RS觸發器的邏輯功能和觸發方式如下:

邏輯功能

RS觸發器的邏輯功能可以通過真值表來描述。真值表如下:

| R | S | Q(t) | Q(t+1) |

|---|---|---|---|

| 0 | 0 | X | Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | X | 0 |

- Q(t) 表示當前狀態,Q(t+1) 表示下一個狀態。

- X 表示不穩定狀態,即觸發器在這種輸入下不能保持穩定。

從真值表可以看出:

- 當R=0且S=0時,觸發器保持當前狀態(Q)不變。

- 當R=0且S=1時,觸發器置位,即Q變為1。

- 當R=1且S=0時,觸發器復位,即Q變為0。

- 當R=1且S=1時,觸發器處于不穩定狀態,輸出Q將被強制為0。

觸發方式

RS觸發器的觸發方式主要有兩種:同步觸發和異步觸發。

1. 同步觸發(Synchronous Triggering)

在同步觸發方式下,觸發器的輸出狀態變化僅在時鐘信號(CLK)的上升沿或下降沿發生。這種觸發方式可以減少由于輸入信號的毛刺或噪聲引起的誤觸發。

同步RS觸發器的邏輯電路通常包括一個時鐘輸入端,以及一些額外的邏輯門來確保只有在時鐘信號的邊沿時才更新輸出狀態。同步觸發器的真值表如下:

| R | S | CLK | Q(t) | Q(t+1) |

|---|---|---|---|---|

| 0 | 0 | X | X | Q |

| 0 | 1 | X | 0 | 1 |

| 1 | 0 | X | 1 | 0 |

| 1 | 1 | X | X | 0 |

2. 異步觸發(Asynchronous Triggering)

在異步觸發方式下,觸發器的輸出狀態可以在任何時候由輸入信號R和S的變化來改變,而不需要等待時鐘信號。這種觸發方式可能會導致由于輸入信號的毛刺或噪聲引起的誤觸發。

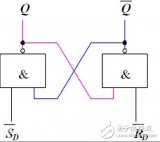

異步RS觸發器的邏輯電路比較簡單,通常只包括基本的與非門或或非門來實現邏輯功能。異步觸發器的真值表與上述邏輯功能相同。

應用

RS觸發器在數字電路中有廣泛的應用,包括但不限于:

- 存儲單元:在寄存器和內存中存儲數據。

- 計數器:在計數器電路中作為基本單元。

- 序列檢測:在序列檢測電路中識別特定的輸入序列。

- 同步化:在多時鐘域的系統中同步信號。

設計考慮

在設計RS觸發器時,需要考慮以下因素:

- 穩定性 :確保觸發器在所有輸入條件下都能穩定工作。

- 抗干擾能力 :設計時鐘信號和輸入信號的去毛刺電路,以減少誤觸發。

- 功耗 :在低功耗設計中,需要考慮觸發器的功耗。

- 速度 :在高速電路中,需要考慮觸發器的響應時間。

-

二進制

+關注

關注

2文章

805瀏覽量

42243 -

RS觸發器

+關注

關注

3文章

101瀏覽量

18367 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

16077 -

邏輯功能

+關注

關注

0文章

14瀏覽量

3207

發布評論請先 登錄

RS觸發器工作原理_RS觸發器邏輯功能_RS觸發器和SR觸發器的區別

rs觸發器的邏輯功能和觸發方式

rs觸發器的邏輯功能和觸發方式

評論