一、概述

芯片壓降的管理是確保集成電路(IC)穩(wěn)定運行的關鍵,涉及單板(PCB)、封裝、芯片內(nèi)部等多個層面。具體的推薦指標數(shù)據(jù)因應用領域、工藝節(jié)點、芯片類型等不同而有所差異,但以下是一些通用的指導原則和參考指標:

1.單板(PCB)層面

?電源層和地層的電阻: 目標通常是小于1mΩ/square(平方英寸),具體數(shù)值根據(jù)電流密度和應用要求而定。

?去耦電容布置: 通常推薦每1平方英寸的邏輯區(qū)域至少配置10uF的去耦電容,高頻應用中還需增加陶瓷電容(如0.1uF或1nF)來處理高頻瞬態(tài)電流。

?電壓波動: 動態(tài)電壓波動(ΔV)目標應小于電源電壓的5%,例如在3.3V電源下,ΔV應小于0.165V。

2.封裝(Package)層面

?封裝引腳電阻: 封裝引腳的電阻(或封裝阻抗)應控制在幾毫歐姆(mΩ)范圍內(nèi),具體數(shù)值依據(jù)封裝類型和設計要求。

?封裝電感: 封裝內(nèi)和封裝到PCB的電感應盡量低,理想情況下封裝內(nèi)電感小于1nH,以減少高頻時的電壓尖峰。

?熱阻: 封裝的熱阻(θjc)影響芯片的散熱,對于高性能應用,熱阻應低于10°C/W。

3.芯片內(nèi)部

?電源網(wǎng)格電阻: 芯片內(nèi)部電源網(wǎng)格的電阻應保持在納歐姆級別(nΩ),以確保在整個芯片上電壓降保持在最低。

?最大允許壓降: 一般認為芯片內(nèi)部的最大允許壓降不應超過電源電壓的5%,一般 建議控制再3%以內(nèi),確保邏輯門的閾值電壓不會受到影響,維持電路的穩(wěn)定工作。

?電遷移限制: 為了防止電遷移現(xiàn)象,局部電流密度通常不應超過幾百萬安培/平方厘米(A/cm2),具體數(shù)值根據(jù)工藝節(jié)點和材料屬性而定。

綜合策略

?仿真驗證: 在設計過程中,使用如Sigrity、Ansys等仿真軟件對全鏈路進行IR Drop仿真,確保在最壞情況下也能滿足上述指標。

?動態(tài)測試: 實際產(chǎn)品在完成設計后,進行動態(tài)測試,驗證在各種工作條件下的電壓穩(wěn)定性,確保設計符合預期。

請注意,這些數(shù)據(jù)是基于一般性建議,具體項目應依據(jù)實際設計需求、工藝能力、以及性能目標進行詳細評估和調(diào)整。

二、die內(nèi)IR drop分析

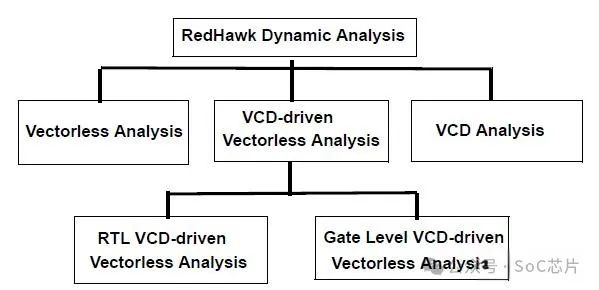

芯片die內(nèi)IR drop(電壓降)分析是半導體設計中的一個重要環(huán)節(jié),它直接關系到芯片的性能和可靠性。在集成電路(IC)內(nèi)部,電流通過電源網(wǎng)絡(power grid)時,由于網(wǎng)絡的電阻(R)和電流(I)的乘積效應,會導致電壓下降。以下是對芯片die內(nèi)IR drop分析的幾個關鍵步驟和考慮因素:

1.模型建立

?物理模型構建:首先,需要建立芯片die的物理模型,包括電源線、地線、晶體管、電容等元素的布局和尺寸,以及它們之間的電氣連接關系。

?電阻網(wǎng)絡模型:將電源網(wǎng)絡簡化為一個電阻網(wǎng)絡模型,通過計算不同金屬層、通孔和連線的電阻值來評估整個網(wǎng)絡的電阻分布。

2.電流分布分析

?靜態(tài)電流分析:計算芯片在無活動時的靜態(tài)電流分布,這通常基于設計的靜態(tài)功耗。

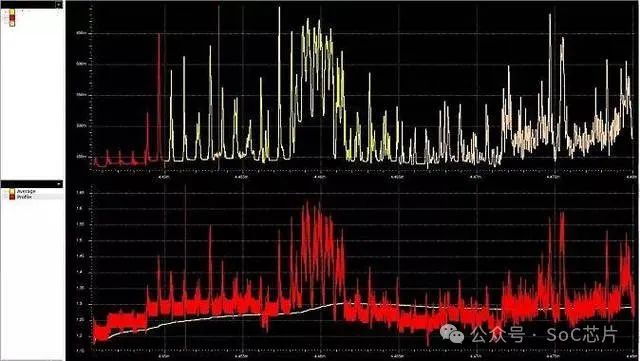

?動態(tài)電流分析:采用仿真工具(如SPICE)模擬芯片在不同操作狀態(tài)下的動態(tài)電流行為,考慮信號翻轉(zhuǎn)、時鐘活動等因素對電流分布的影響。

3.電壓降仿真

?靜態(tài)IR drop仿真:基于靜態(tài)電流分布計算電源網(wǎng)絡的電壓降,評估在無時序約束下的電壓穩(wěn)定性。

?動態(tài)IR drop仿真:考慮瞬時電流變化對電壓的影響,仿真在各種工作模式下,特別是高負載時的電壓波動情況。

4.關鍵區(qū)域識別

?熱點分析:通過仿真結果識別電壓降最大的區(qū)域,這些通常是電流密度高或電源網(wǎng)絡電阻較大的地方。

?時序分析:評估電壓降對電路時序路徑的影響,包括setup和hold時間,確保時序收斂。

5.優(yōu)化策略

?電源網(wǎng)格改進:優(yōu)化電源和地網(wǎng)的布局,增加金屬層,使用更大截面的金屬線以降低電阻。

?去耦電容優(yōu)化:在關鍵區(qū)域布局去耦電容,吸收瞬間電流尖峰,減少電壓波動。

?電流均衡:調(diào)整電路設計,盡可能平衡電流分布,避免局部過熱和電壓突降。

6.驗證與簽核

?IR drop簽核:確保在所有預期工作條件下,電壓降滿足設計規(guī)范,不會導致電路功能錯誤。

?EMC/熱分析:同時考慮電磁兼容性和熱管理,確保芯片在高功率操作下的穩(wěn)定性和可靠性。

7.迭代優(yōu)化

?設計迭代:基于仿真和分析結果,對設計進行調(diào)整,再次進行仿真驗證,直至所有指標滿足要求。

總之,芯片die內(nèi)IR drop分析是一個迭代、復雜的過程,需要綜合考慮設計、仿真、優(yōu)化和驗證的各個方面,以確保芯片在實際應用中能夠穩(wěn)定、高效地工作。隨著半導體工藝的進步和設計復雜性的增加,這一過程變得越來越重要,同時也是提升芯片性能和降低功耗的關鍵步驟。

三、封裝IR drop分析

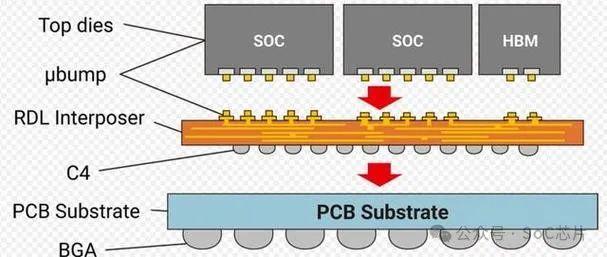

芯片封裝中的IR drop(電壓降)分析是一個復雜而重要的過程,它涉及評估封裝內(nèi)部的電壓損耗,確保芯片在封裝后能夠正常工作,不受電源波動的影響。封裝級的IR drop分析主要關注于從外部電源到芯片內(nèi)部的電源傳輸路徑中的電壓損耗。以下是進行封裝IR drop分析的關鍵步驟和考慮因素:

1.封裝模型構建

?物理模型:首先,需要構建一個精確的封裝模型,包括封裝材料(如基板、引線框架)、封裝內(nèi)電源線和地線、焊點(如Flip Chip下的凸點或Wire Bond的線)的電阻值和電感值。

?電氣模型:使用三維電磁場仿真軟件(如ANSYS HFSS,Cadence Sigrity等)建立封裝的電氣模型,模擬不同頻率下的電流流動和電場分布。

2.電流分布分析

?提取電流波形:根據(jù)芯片的功耗分布和工作模式,提取不同工況下的電流波形,包括峰值電流、平均電流和瞬態(tài)電流變化。

?封裝內(nèi)電流路徑:分析電流如何通過封裝的各個部分,包括引腳、襯底、封裝內(nèi)互連等,以識別潛在的高電阻或高電感區(qū)域。

3.IR drop仿真

?靜態(tài)分析:進行靜態(tài)IR drop仿真,評估在固定電流條件下的電壓降,確保在整個封裝上電壓分布均勻。

?動態(tài)分析:執(zhí)行動態(tài)仿真,考慮瞬態(tài)電流效應,評估在開關操作和高負載狀態(tài)下電壓波動的程度,這對于高速信號和敏感電路尤為重要。

4.熱效應考慮

?熱分析:封裝的溫度上升會導致電阻增加,進而影響IR drop。因此,進行熱分析,將溫度影響納入IR drop仿真,確保分析結果的準確性。

5.優(yōu)化與改進

?設計優(yōu)化:基于仿真結果,優(yōu)化封裝設計,如增加或優(yōu)化去耦電容布局、改善電源線和地線結構、選用低電阻材料等,以減少IR drop。

?電源分配策略:考慮使用多電源引腳、優(yōu)化電源分配網(wǎng)絡(PDN)設計,確保電源穩(wěn)定供給。

6.驗證與簽核

?簽核標準:根據(jù)行業(yè)標準和具體應用要求,設定IR drop的允許范圍,確保芯片在封裝后的性能和可靠性。

?后封裝測試:在實際封裝樣品上進行測試,驗證仿真結果,必要時進行調(diào)整。

7.系統(tǒng)級考慮

?與PCB協(xié)同優(yōu)化:封裝的IR drop分析不能孤立進行,需要與PCB的電源分配網(wǎng)絡設計協(xié)同考慮,確保整個系統(tǒng)層面的電源完整性。

通過上述步驟,可以有效地分析和管理芯片封裝中的IR drop,保證芯片在封裝后的性能表現(xiàn),減少因電源波動導致的功能故障和可靠性問題。

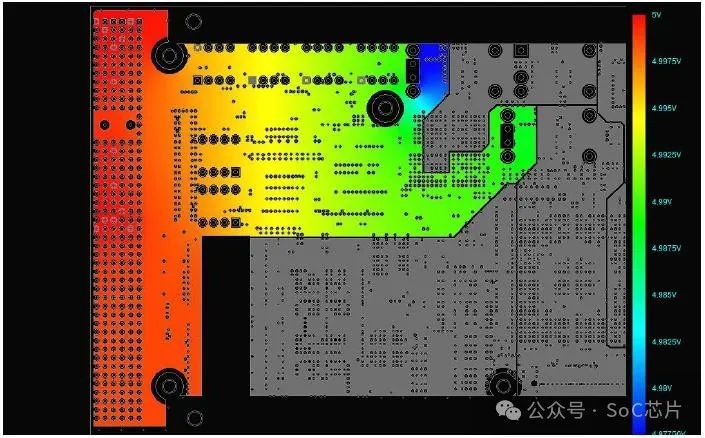

四、PCB單板IR drop分析

PCB(Printed CircuitBoard,印刷電路板)單板上的IR drop(電壓降)分析是確保電子設備穩(wěn)定運行的關鍵環(huán)節(jié),它評估了電流通過PCB電源網(wǎng)絡時因電阻效應引起的電壓損失。以下是進行PCB單板IR drop分析的主要步驟和考慮因素:

1.建模與準備

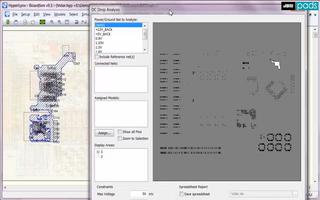

?電源網(wǎng)絡建模:使用EDA(Electronic Design Automation)工具如CadenceAllegro、Mentor Graphics HyperLynx或Altium Designer等,建立PCB的電源網(wǎng)絡模型。這包括電源平面、地平面、電源軌、去耦電容和連接這些部件的走線。

?電流需求分析:根據(jù)電路設計,估算不同工作模式下各個部分的電流消耗。這可能涉及靜態(tài)電流分析(DC)和動態(tài)電流分析(AC),考慮時鐘速度、信號翻轉(zhuǎn)率等因素。

2.仿真設置

?設置仿真參數(shù):在仿真軟件中輸入電源電壓、電流波形、環(huán)境溫度等參數(shù),確保仿真條件貼近實際工作環(huán)境。

?確定仿真范圍:選擇仿真時間窗口和感興趣的頻率范圍,以捕捉瞬態(tài)和穩(wěn)態(tài)行為。

3.IR drop仿真

?靜態(tài)IR drop分析:在無信號變化的情況下,計算電源網(wǎng)絡的電壓降,確保在靜態(tài)條件下的電壓穩(wěn)定。

?動態(tài)IR drop分析:模擬電路在不同操作模式下的瞬態(tài)電流變化,評估電壓波動,特別是對于高速信號和高功耗元件。

4.結果分析

?熱點識別:分析仿真結果,識別電壓降最大的區(qū)域,這些通常是電流密度高或電阻較大的區(qū)域。

?時序分析:評估電壓降對信號完整性的影響,包括是否導致時序違例(如setup和hold時間)。

5.優(yōu)化與調(diào)整

?電源平面優(yōu)化:通過增加電源平面的銅厚度、優(yōu)化平面布局、減少分割,降低電源網(wǎng)絡的總電阻。

?去耦電容優(yōu)化:合理布局去耦電容,特別是靠近高功耗元件,以快速響應瞬態(tài)電流需求,減少電壓波動。

?走線和過孔優(yōu)化:優(yōu)化電源和信號走線的寬度、長度,減少過孔數(shù)量,以降低電阻和感抗。

6.驗證與迭代

?設計迭代:根據(jù)仿真和分析結果,對PCB設計進行必要的修改,然后重復仿真和分析過程,直到所有關鍵區(qū)域的IR drop滿足設計規(guī)范。

?物理測試:在最終設計階段,可能還需要進行實際的測試驗證,確保仿真結果與實際情況相符。

通過上述步驟,可以有效管理和降低PCB單板上的IR drop,提高電子產(chǎn)品的穩(wěn)定性和可靠性,確保其在各種工作條件下的性能表現(xiàn)。

-

芯片

+關注

關注

459文章

52350瀏覽量

438648 -

集成電路

+關注

關注

5420文章

12012瀏覽量

367796 -

封裝

+關注

關注

128文章

8618瀏覽量

145124 -

去耦電容

+關注

關注

11文章

319瀏覽量

22882

原文標題:SoC芯片設計系列---芯片工作全鏈路壓降分析

文章出處:【微信號:gh_9d9a609c9302,微信公眾號:SoC芯片】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

芯片工作全鏈路壓降分析

芯片工作全鏈路壓降分析

評論