以下文章來源于慧智微電子,作者小慧

01

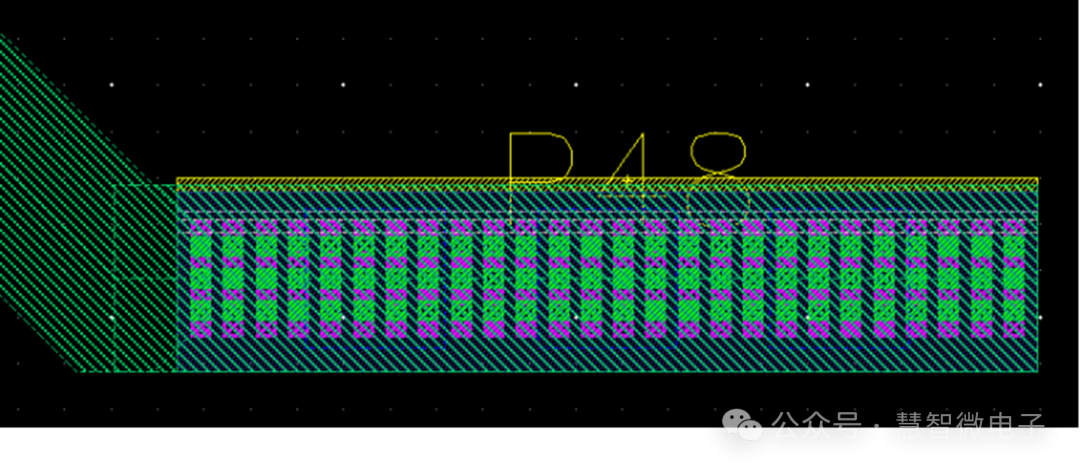

如何在Cadence的EMX仿真中精準設(shè)置長邊PORT?

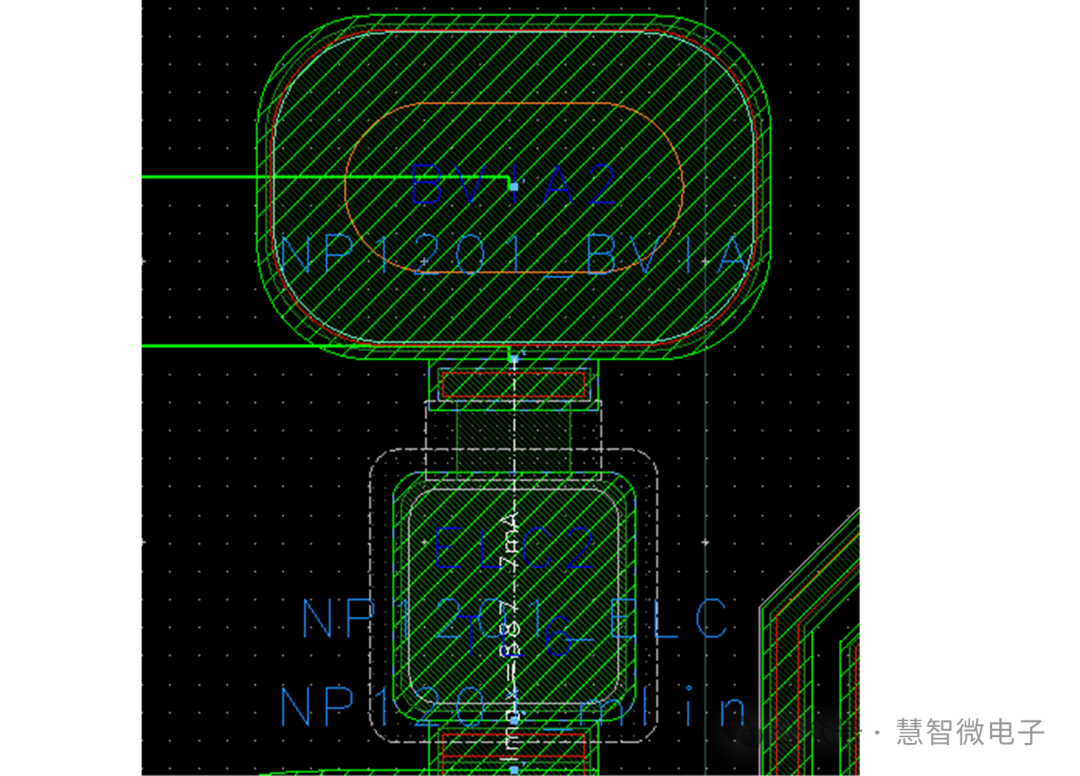

Q:請問在Cadence的EMX仿真里,如果需要在一個較長的邊打PORT,需要怎么設(shè)置會仿真比較精準?像這樣子直接吸附一個上去可以嗎?

A:你這不是label嗎?

Q:對,就是打label然后跑EMX。

A:是不是搞個傳輸線跑一下看看行不行就知道了。

A:可以,最好打到邊沿,沒達到邊沿會自動選個最近的邊沿。

Q:好的,謝謝大佬。

A:不過你可以估一下這個邊沿的長度和波長的關(guān)系。

Q:好的(????????)??????,不過這個頻率下對應(yīng)波長有5mm,應(yīng)該不太會影響。

A:嗯嗯,這種2.5D的電磁好像要注意一下如果有長邊注入信號可能會不準,和算法的一些假設(shè)近似有關(guān)。

02

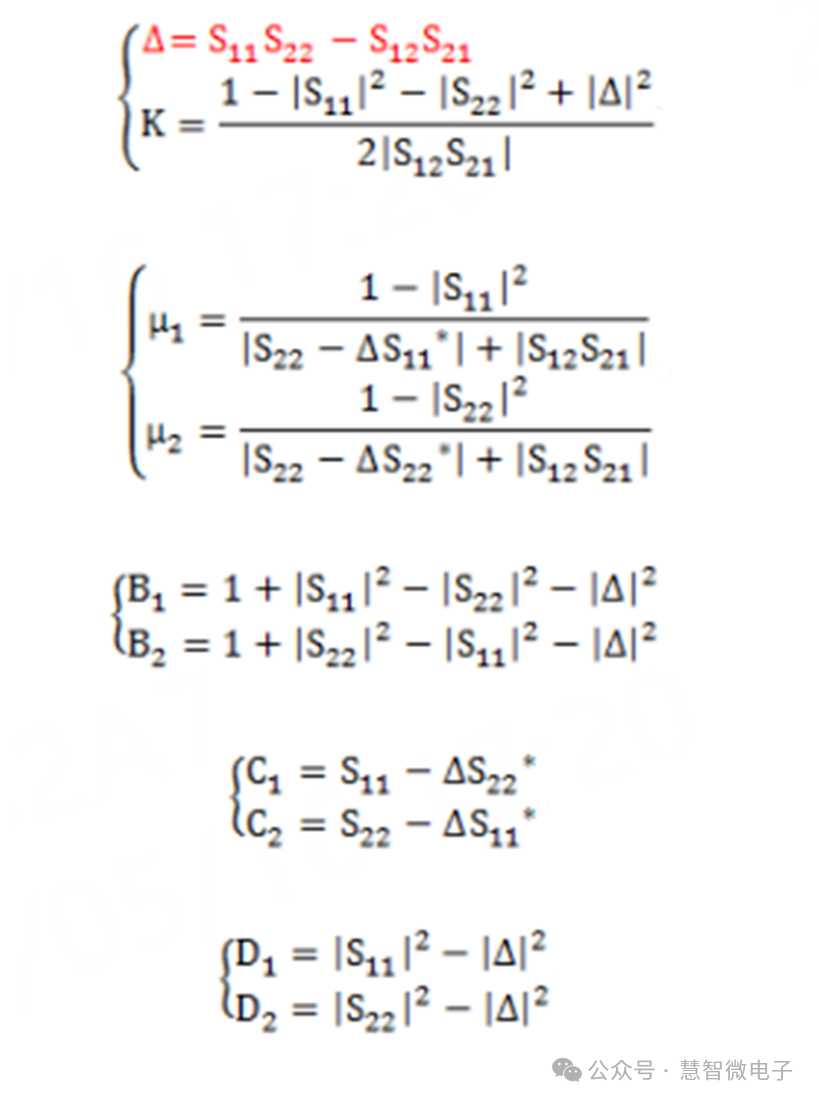

請問s參數(shù)可以計算穩(wěn)定性μ嗎?

Q:請問s參數(shù)可以計算穩(wěn)定性μ嗎?我測試得到S參數(shù)dB值。

A:可以,測試時導出為復數(shù)形式,然后放入maltab里面用矩陣計算。

就按照這個計算就可以。

Q:我測試數(shù)據(jù)只有dB,是不是就沒用了。

A:你看下保存數(shù)據(jù)格式,是不是有幅度與相位,有的話應(yīng)該可以,都是從網(wǎng)分導出數(shù)據(jù),大不了再導出一次。

Q:好的,多謝大俠。

03

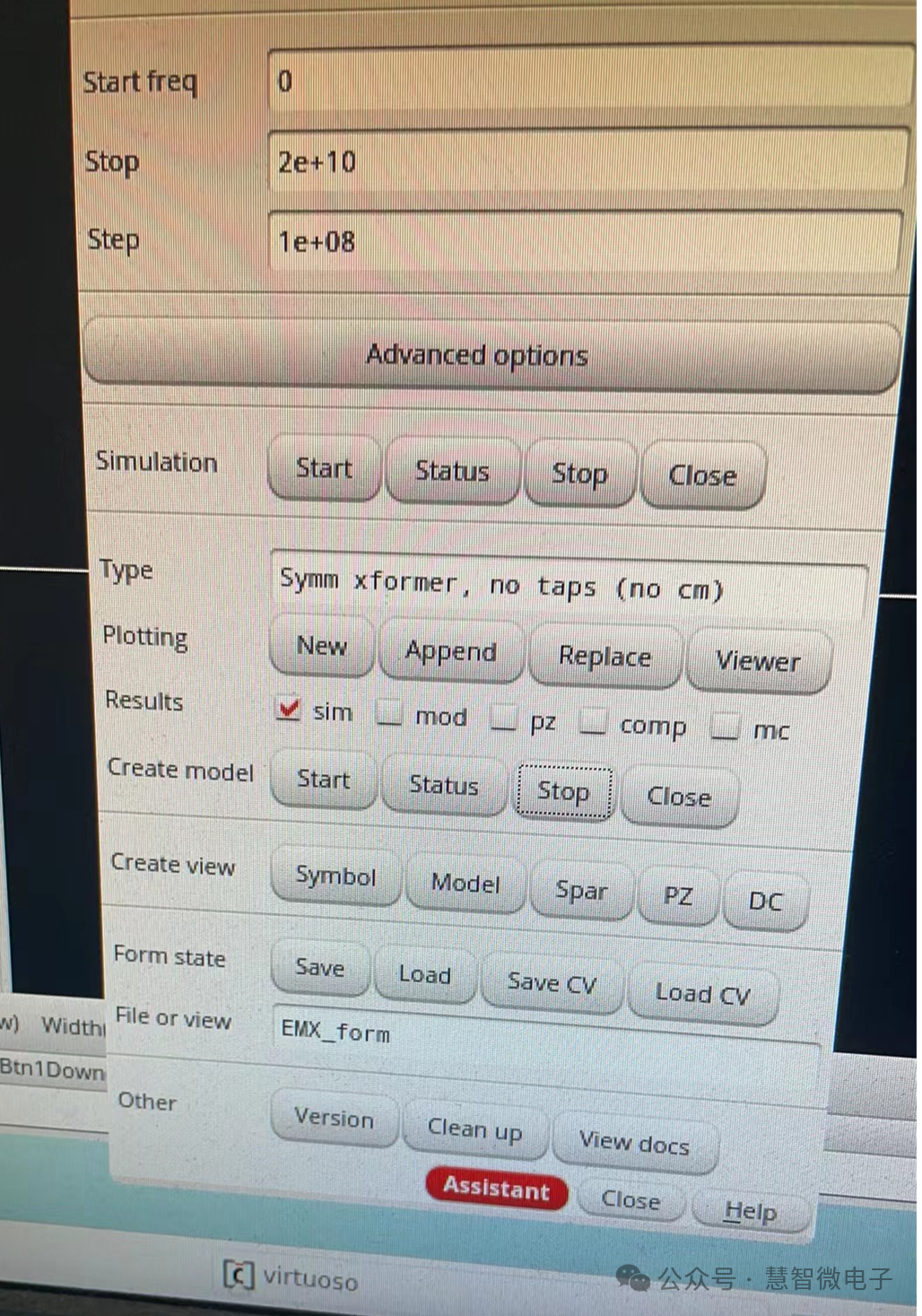

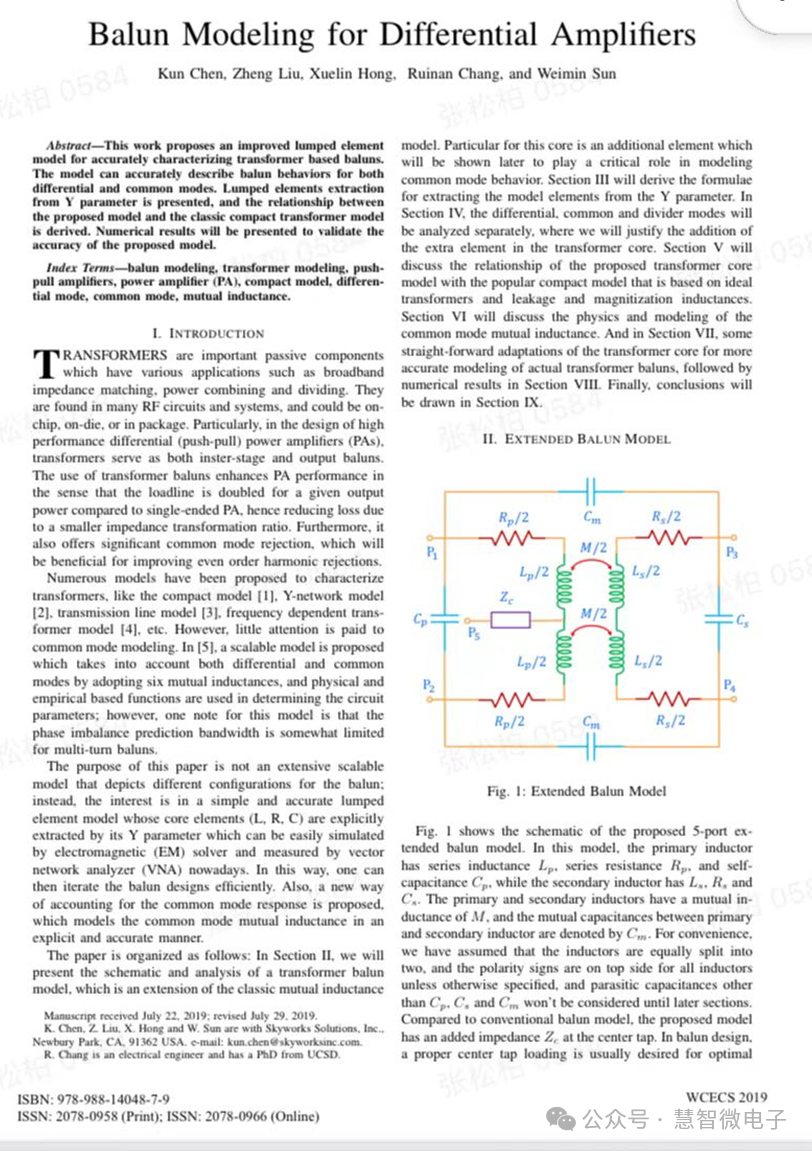

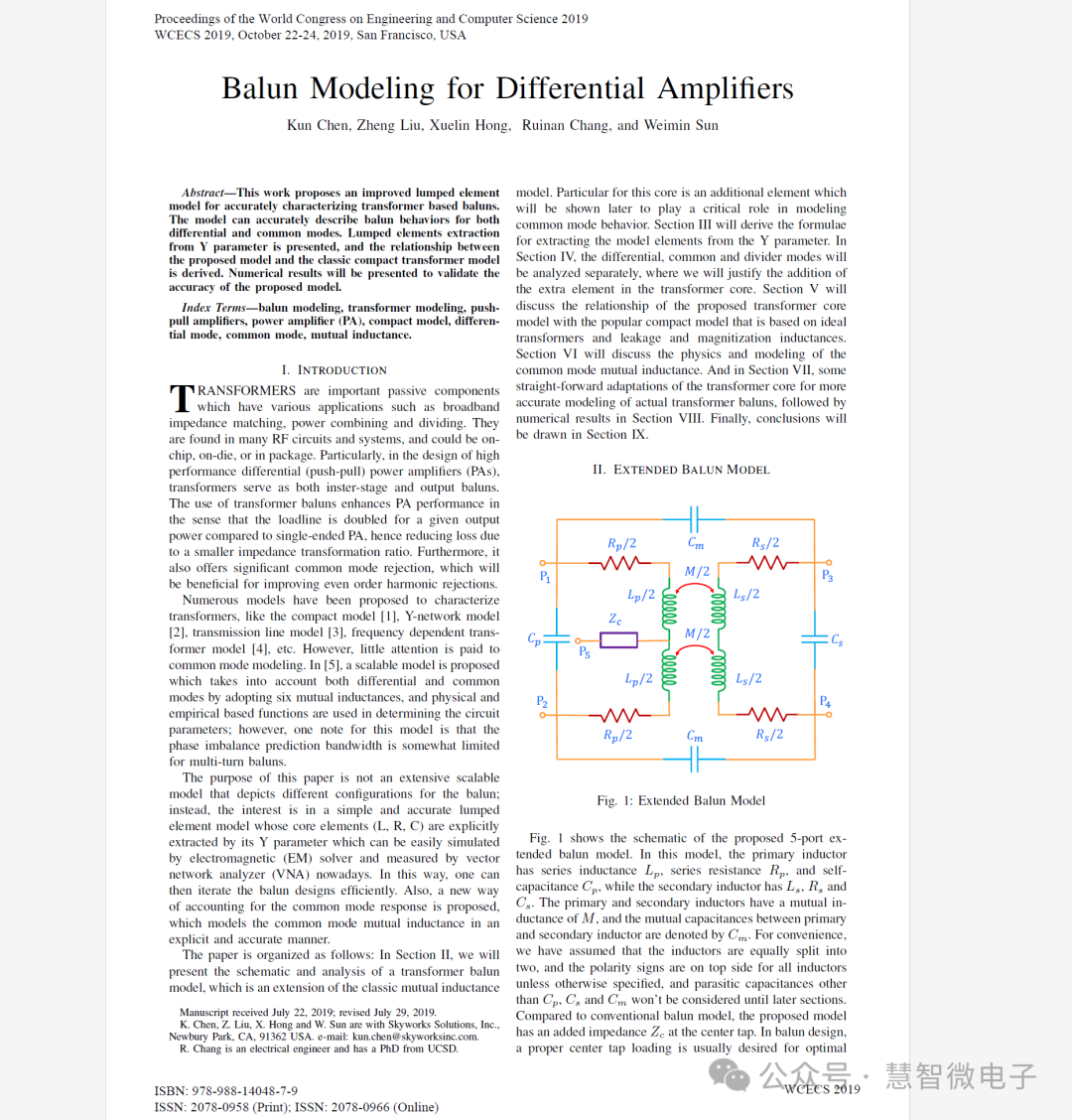

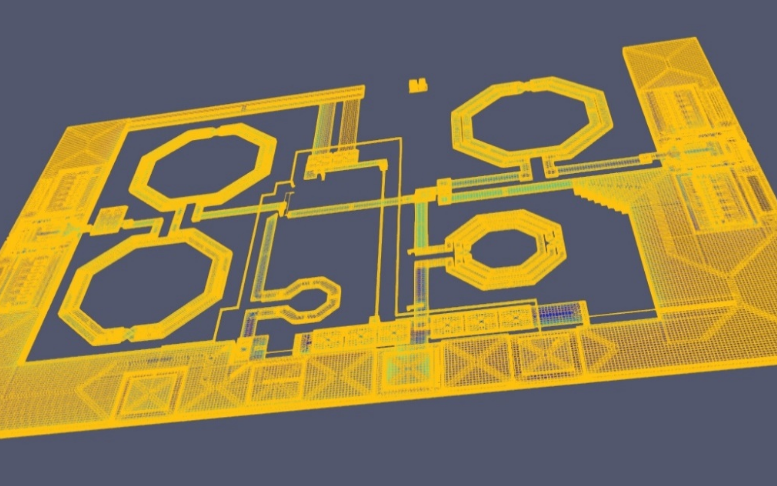

有關(guān)Virtuoso中變壓器EMX仿真snp文件導出與多圈仿真問題的討論

Q:請問在layout中畫好了變壓器,經(jīng)過了emx仿真,怎么導出snp文件,重新放進原理圖仿真呢?在virtuoso里面。

A:下面不是有CREATE嗎,下面create點Spar生成s參數(shù)的nport,再打包成symbol就好。

Q:謝謝,再請教一下,如果變壓器是兩個主圈和一個次圈繞在一起的,但是emx每次只能仿真其中一個主圈和次圈的耦合結(jié)果,不能同時看兩個主圈和一個次圈的結(jié)果。這樣生成的snp文件應(yīng)該是不準確的吧?忽略了另一個主圈。

A:可以參考這篇論文。

Q:好像不一樣,我這個是兩個主圈耦合到同一個次圈上。

A:還有參考是Gang Liu 的博士畢業(yè)論文。該是常見的參考。

Q:多謝您!!!

04

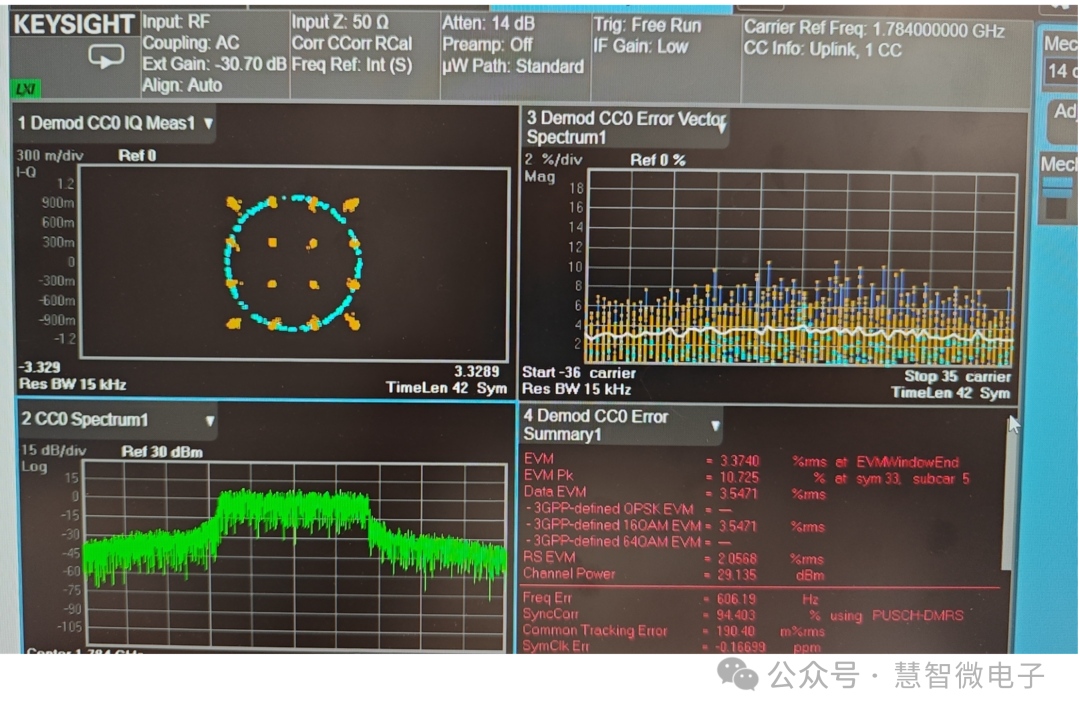

PA輸入信號EVM和ACLR良好,但EVM為何惡化?

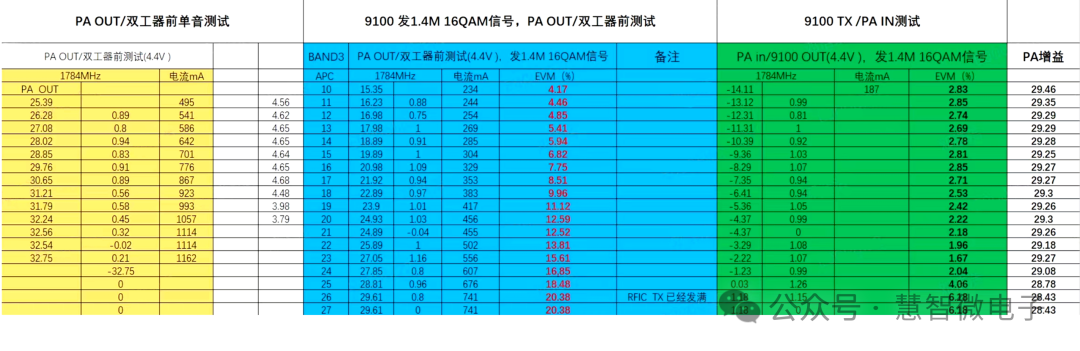

Q:請教個問題:PA輸入信號EVM和ACLR都挺好,PA的增益和線性功率也很大,但是就是EVM惡化非常大,是啥原因呢?

A:線性功率很大,有數(shù)據(jù)嗎?輸入輸出,PA的線性,都沒數(shù)據(jù),怎么分析呢?

A:輸出的ACLR怎樣?器件里面只有PA嗎?有沒有集成開關(guān)之類的?

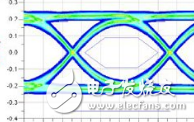

Q:左面黃色是單音測的,不知道輸入。左面是PA 輸入,中間是PA 輸出信號。只有PA,集成的PA,內(nèi)部有一個SP3T開關(guān),把PA輸出引到三個不同PAD。?EVM和ACLR全部惡化很多。

A:線性度的數(shù)據(jù)除了P1dB還要OIP3呢?

Q:OIP3沒測,別的廠家的PA,其他低頻段900M左右,EVM幾乎沒有惡化。

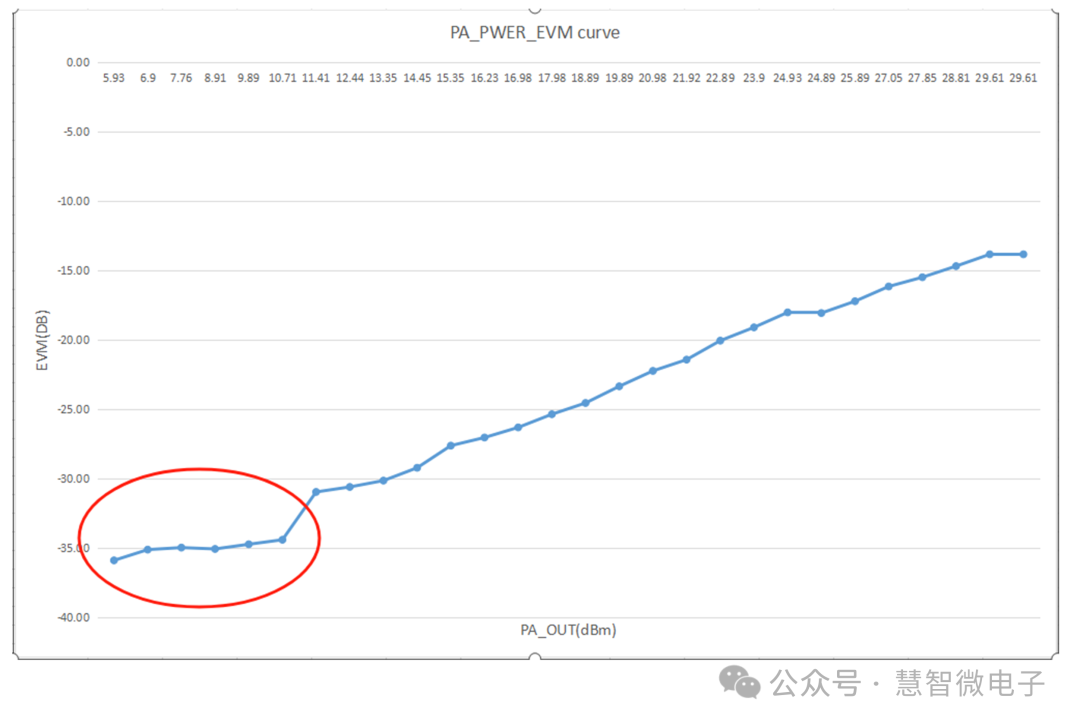

A:輸入evm是-30dB,輸出最開始是-27dB,感覺已經(jīng)有非線性出來了。可以先講輸入信號調(diào)低,從PA輸入從小到大,將PA的浴盆曲線掃描出來才能夠判斷了。

Q:找到最好的EVM?

A:一下懟非線性區(qū)不好辦。

A:1是不是輸入太大了?可以將輸入打小點嗎?

Q:輸入可以打小,-14dBm,其實很小了。可以繼續(xù)發(fā)更小功率,EVM可以和輸入差不多。

浴盆曲線后,是要干什么?

A:最好evm才-30dB?

粗略判斷鏈路的線性區(qū)間。

Q:我們的RFIC最好也就1%這樣。

A:輸入匹配是一樣的嗎?

Q:稍有不同,方便焊接調(diào)制信號把PA的匹配去掉了,直接接到頻譜儀,原來有幾個匹配,PA.輸出匹配不是50歐姆。

?

A:不是應(yīng)該拿信號源先測試外部PA么?直接上鏈路了?

Q:明天準備,信號源單獨灌PA信號,因為之前除了1.4M帶寬EVM ACLR也能達標,就沒太關(guān)注。測了1.4M的16QAM信號,EVM超標了,把問題爆扣出來了。

A:工作時就TX不切對吧?“ 集成的PA,內(nèi)部有一個SP3T開關(guān),把PA輸出引到三個不同PAD”

Q:工作時是固定的,不切換。

A:這個1.4m是容易出問題。

Q:猜測1.4M窄帶OIP3異常。這個現(xiàn)象單獨測試PA不一定有問題,畢竟PA的供應(yīng)商肯定內(nèi)部有測試過。

A:除了1.4M帶寬信號,其他的帶寬信號是多少的?

Q:3M/5M/10M/15M/20M帶寬。

A:猜測1.4M窄帶OIP3異常。這個現(xiàn)象單獨測試PA不一定有問題,畢竟PA的供應(yīng)商肯定內(nèi)部有測試過。

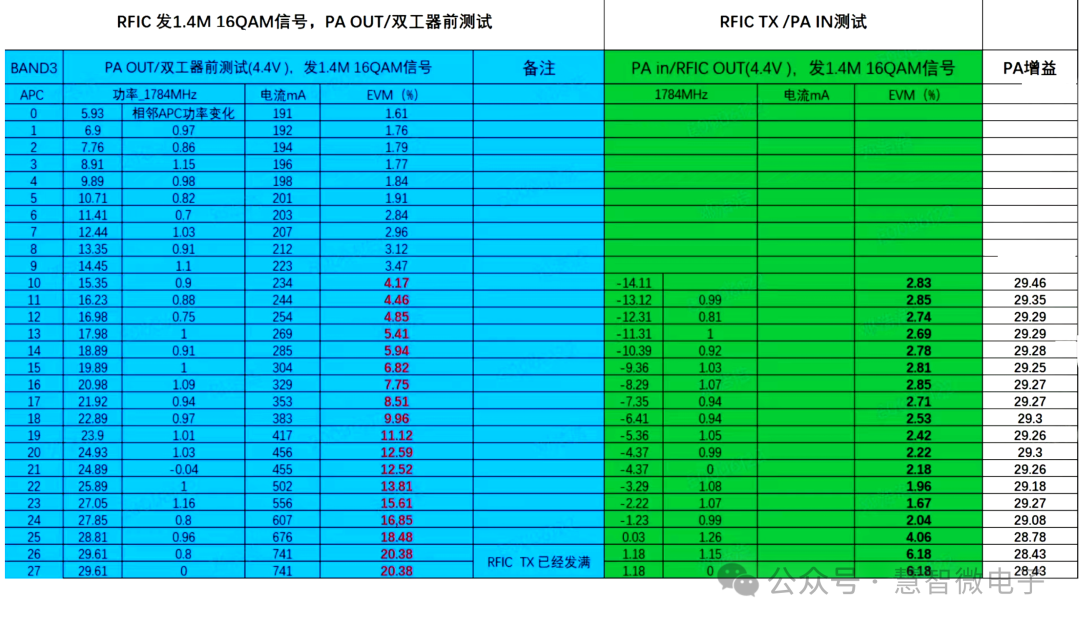

Q:補充了下小功率的EVM。

A:需要跟你用信號源輸入信號,測量PA的輸出進行對比;16QAM信號的峰均比是多少的?我忘記了;可以用頻譜儀測量信號源輸出16QAM信號時,峰值功率和平均功率的比值,那個就是峰均比了;不習慣用百分比來表示EVM,習慣用dB,線性區(qū)間只有這么點?

Q:單獨PA輸入,測試PA輸出,EVM達到28dbm,EVM只從輸入0.4惡化到2.2。PA輸出29dbm,EVM也只到3.37。

A:那說明PA自身沒問題,還是需要回到鏈路上面查問題了。需要排除1.4M窄帶下OIP3。和排除PA對芯片輸出的pulling之類的可能。

Q:PA的OIP3嗎?PA對芯片pulling,這個怎么能夠測試確認呢?

A:可以分開兩個板子,一個是PA only,一個是主芯片only,PA only接信號源OK,是不是接主芯片那邊就異常了。這樣也方便接入功分器監(jiān)測PA only接主芯片時,主芯片的輸出指標。

Q:好的,謝謝。1.4M 的OIP3指的是PA本身嗎?

A:鏈路的。

Q:多謝大佬。

A:一般像類似慧智微的PA出廠時都是經(jīng)過嚴格測試過的,通常不會出問題,除非硬件上有環(huán)路自激。所以還要排除環(huán)路自激的可能。

A:感覺有點像環(huán)路自激,換個頻點試試。

Q:這倒確實是有這種可能。多謝多謝。

05

如何通過網(wǎng)分測試PA的輸出功率?

Q:各位大佬,請問一下,網(wǎng)分測試pa。我的網(wǎng)分輸入功率給了-40dBm,網(wǎng)分測試出來的增益是電壓的狀態(tài)下的值么(20log的結(jié)果)?比如15dB,那我想得到輸出功率,是不是需要需要把這個15dB轉(zhuǎn)化成10log的結(jié)果我這么理解對么?

A:你是想通過矢網(wǎng)測PA的輸出功率?輸入-40dBm,增益15dB,測量輸出功率-40dBm + 15=-25dBm (要準確值的話,矢網(wǎng)端口要做功率校準)。

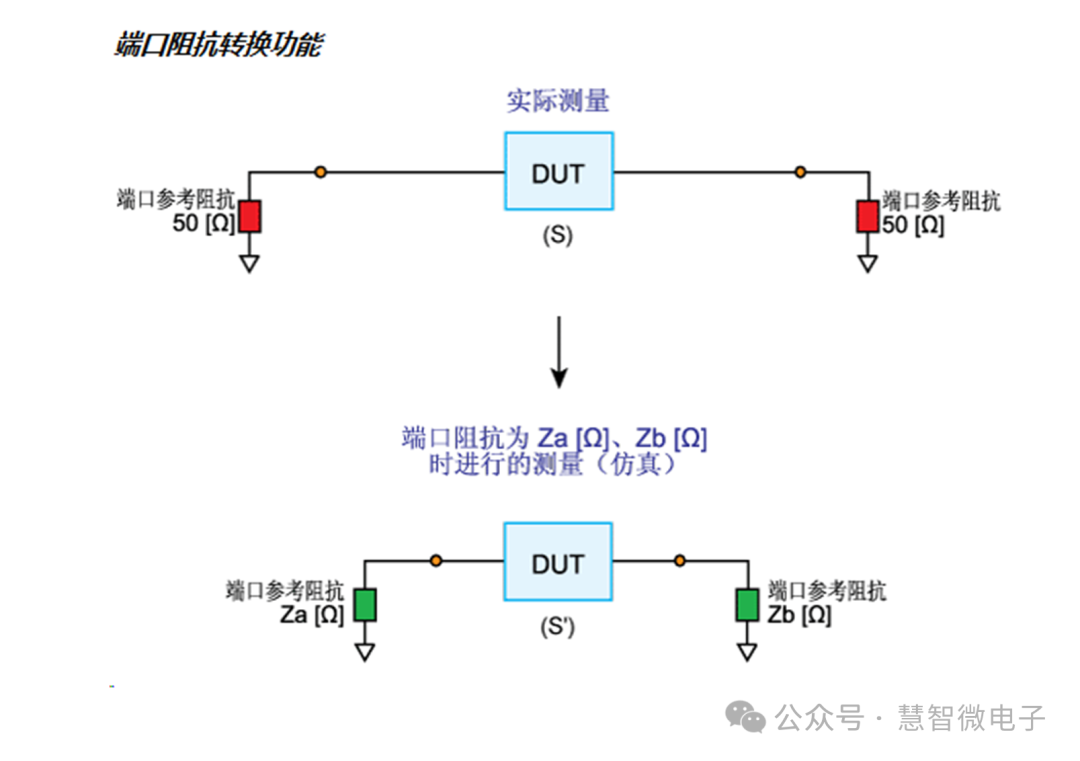

Q:是的,矢網(wǎng)測出來的是不是應(yīng)該是電壓表征的S參數(shù)?

A:這個是和你設(shè)置相關(guān)的;如果阻抗都設(shè)置為50Ω,就無所謂電壓和功率;如果阻抗設(shè)置的不一樣,那么就需要注意了;

Q:因為我想得到輸出功率,如果矢網(wǎng)得到的是電壓表征的S參數(shù),那我是不是應(yīng)該換算成功率表征的S參數(shù)后再加上輸入功率,現(xiàn)在端口都是做了50Ω的匹配的。

A:那應(yīng)該沒問題吧。

Q:謝謝大佬的解答。

06

如何用網(wǎng)分測量芯片的S參數(shù)和駐波比?

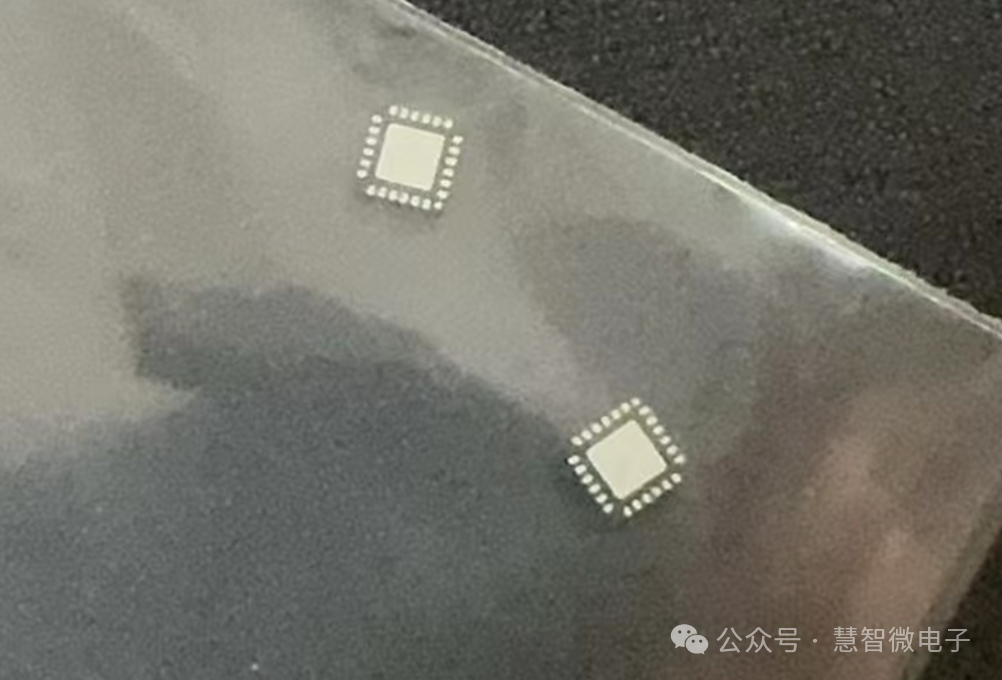

Q:有大佬知道這種芯片如何用網(wǎng)分測量s參數(shù),駐波比等參數(shù)嗎?

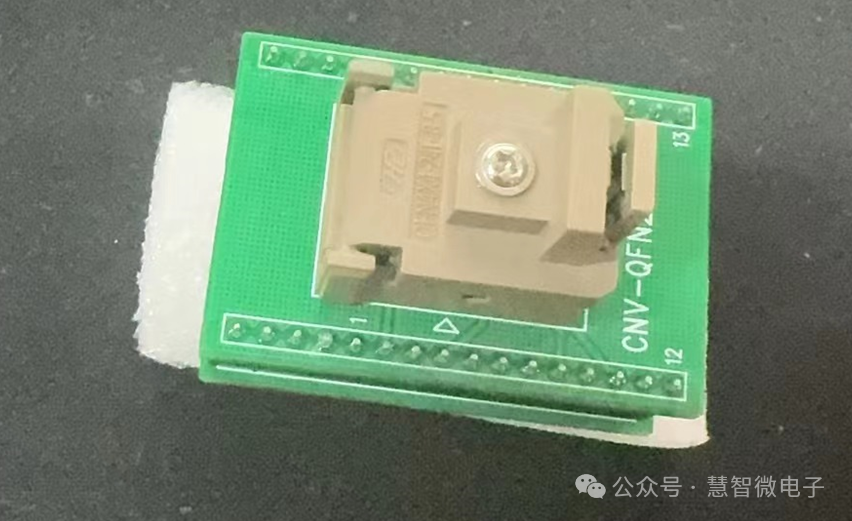

A:要么焊接做成evb,要么做dutboard放socket里面。

Q:okok感謝感謝

A:不做測試板也可以,網(wǎng)分里邊有一個功能叫測試端口延伸。

Q:好的好的我也去了解下謝謝。

Q:他好像有這么個東西。

有個公司找我們組代測試,他們工程師也不會我們的博士最近也很忙,沒人管這個,所以來問問大佬們見過沒。

A:這種的射頻線接到哪里呢?

A:記不大清楚了,找根線,對線進行開路,和短路校準。

Q:圖片里這好像就是個測試座,但是不知道怎么連。

A:我見過的和你說的這種測試座類似,但是芯片引腳通過測試版會引出來個sma接口,用于連接射頻線纜進行測試。

Q:按道理我也覺得是這樣子的,可是這個測試座,也沒有引出來的用于射頻連接的口。

A:網(wǎng)分可以校準到sma接頭,再接上這個測試板,不放芯片,利用網(wǎng)分的端口延伸到socket里面的針腳上,也可以制作trl校準板,這樣更準確一點。

Q:收到收到。我看看去。

07

芯片經(jīng)歷過HTOL實驗后能保證正常工作多少年?

Q:請教各位大佬,有誰知道芯片經(jīng)歷過125攝氏度1000h的HTOL實驗,能保證芯片正常工作多少年嗎?

A:國軍標里好像有模型,按照溫度降低10℃,壽命增加一倍來算,假設(shè)正常工作溫度在55℃,使用壽命是1000h*2^7,大概14.6年。

Q:好的謝謝。請問下是國軍標的哪個標準啊?

A:我以前看到他們演示的是離線版本,很專業(yè),只可惜沒有拿到。估計應(yīng)該是大同小異。

Q:好的,謝謝。我對比了兩種模型的仿真結(jié)果,S參數(shù)仿真結(jié)果區(qū)別不大。這兩種文件的區(qū)別,應(yīng)該廠家在測試方法上的區(qū)別。

A:看你的頻率了。

A:根據(jù)Arrhenius方程在使用溫度不同的情況下,加速因子還有活化能Ea也會有所不同,假設(shè)使用溫度55度活化能0.7eV,125攝氏度1000小時,相當於9年左右。您可以參考JESD47 和JEP122 。

A:器件物理那本書應(yīng)該有。

Q:收到,感謝各位大佬。

08

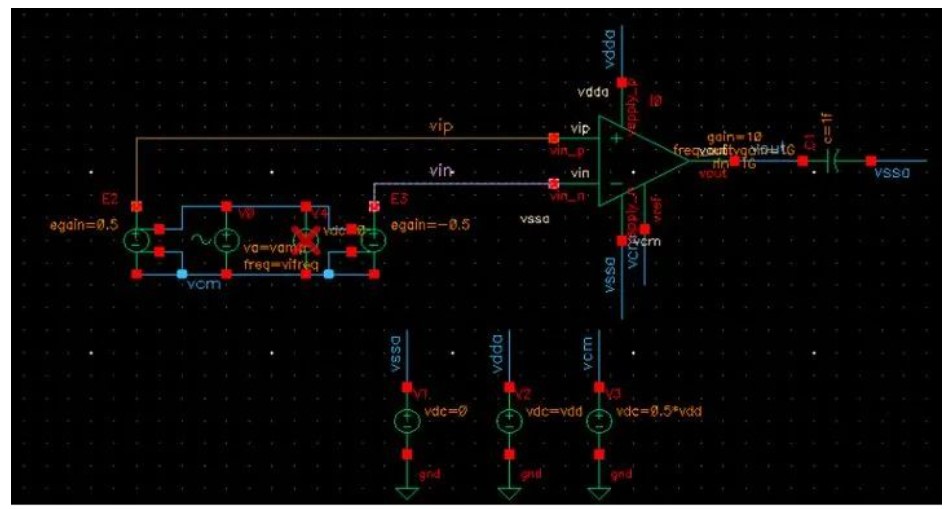

電容接地,版圖上怎么連接的呢?這里需要加微帶線嗎?

Q:問下電容接地,版圖上怎么連接的呢?這里需要加微帶線嗎?

A:上下兩層金屬都連到bvia就行了吧,圖里看起來只連了met1。

Q:懂了,謝謝。

-

變壓器

+關(guān)注

關(guān)注

162文章

7781瀏覽量

139336 -

Cadence

+關(guān)注

關(guān)注

67文章

973瀏覽量

144309 -

仿真

+關(guān)注

關(guān)注

52文章

4269瀏覽量

135746 -

EVM

+關(guān)注

關(guān)注

3文章

921瀏覽量

42095

原文標題:PA輸入信號EVM和ACLR良好,但EVM為何惡化?

文章出處:【微信號:射頻學堂,微信公眾號:射頻學堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

X-FAB宣布采用Cadence EMX Solver電磁仿真技術(shù),加速創(chuàng)新通信和車用射頻設(shè)計

分享PSpice AA仿真中的高級參數(shù)設(shè)置

Cadence仿真

如何在Cadence中搭建仿真電路去仿真擺率?

請問怎么理解cadence里面的port?

XILINX SERDES SI仿真中抖動的設(shè)置

如何在在Vivado中使用Cadence IES模擬進行仿真

看看如何在transient仿真里面設(shè)置吧

Cadence推出EMX Designer,在片上無源元件綜合上提供超過10倍的性能提升

Cadence EMX 3D Planar Solver 通過 Samsung Foundry 8nm LPP 工藝技術(shù)認證

如何在Cadence的EMX仿真中精準設(shè)置長邊PORT

如何在Cadence的EMX仿真中精準設(shè)置長邊PORT

評論