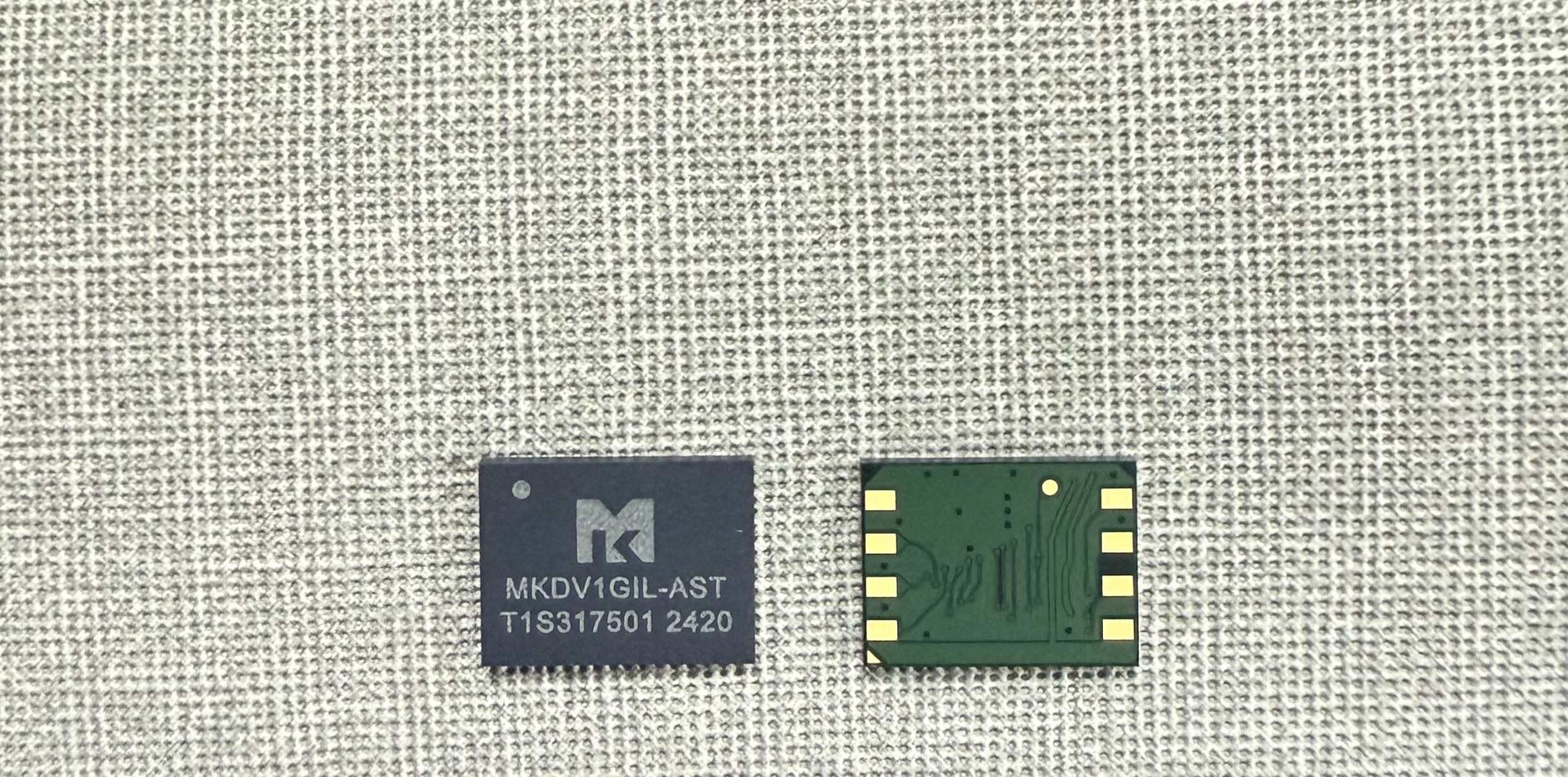

固定延遲UHS-I主機設計實例

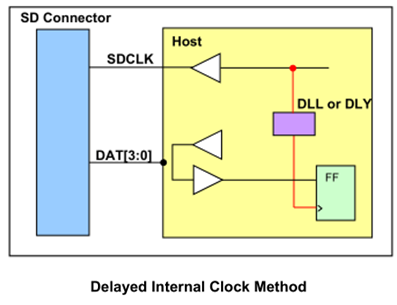

內部時鐘延遲方法采樣時鐘由內部時鐘通過DLL或延遲線創建。

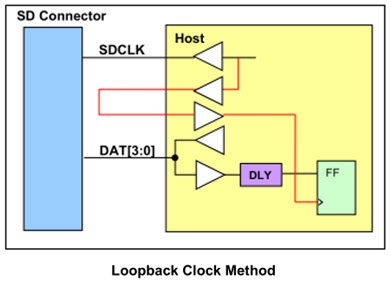

環回時鐘的創建圖

下圖顯示了環回時鐘的一個示例實現。

適用于固定輸出延時定時。

但是,主機設計人員需要注意由于額外路由CLKl跟蹤而產生的過多EMI。

主機需要額外的兩個引腳。

可以通過插入延遲線、R、C或使用DLL來調整接收機觸發器的設置和保持時間。

UHS-1調諧程序

調諧是指在主機中尋找最優采樣點的過程。

一旦SD卡從默認速度轉移到SDR104模式,調諧過程就開始了。

調諧過程掃描UI (Unit Interval),以獲得最佳采樣點。

主機采樣點調諧:

1.主機復位采樣控制塊

2.主機發出發送調優塊命令來讀取調優塊。

3.卡發送調諧塊作為讀取數據。主機接收它并與已知的調優塊模式進行比較。

4.主機將采樣控制塊增加一步。

5.主機為下一個調優塊發送讀取命令。

重復上面的步驟3到步驟5來覆蓋整個UI。

在覆蓋整個Ul之后,主機能夠識別可用的有效窗口。

主機將采樣控制塊設置到有效窗口的中心。

主機采樣點調優完成后,可以開始讀/寫操作。

主機設計建議

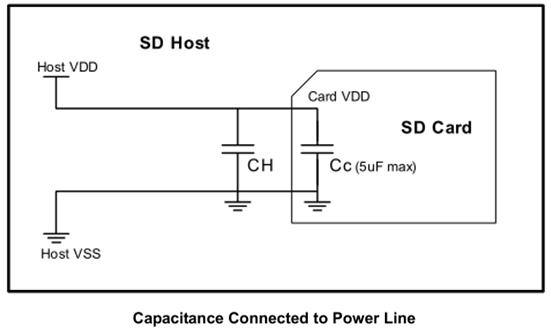

插在電源線上的去耦電容由于插在VDD和VSS之間的卡電容,SD卡插入時產生涌流。

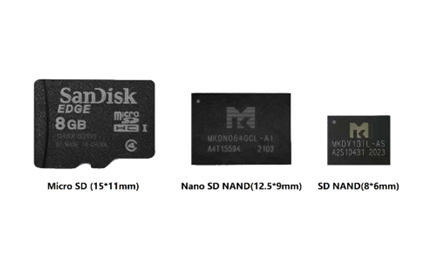

本附錄提供了一種使用安裝在SD NAND附近的去耦電容來降低由浪涌電流引起的電壓降的方法。

如果主機支持熱插入,并且電源電路通常與其他設備一起使用,則主機應考慮并減少浪涌電流的影響。

采用限流電路等另一種方法也是可行的。

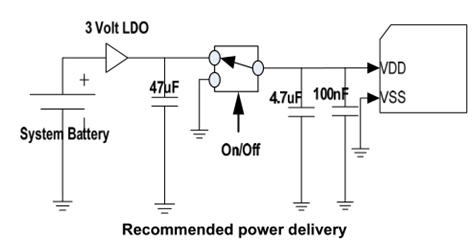

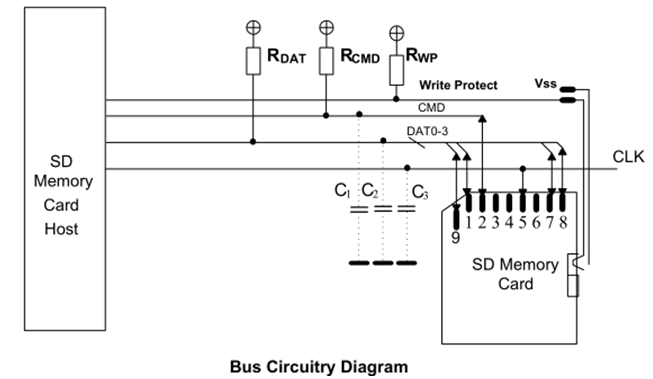

上圖顯示了去耦電容器的典型組成。

SD存儲卡中去耦電容的最大電容定義為5uF。

去耦電容CH用于減小卡熱插拔時的壓降,最好放置在離連接器越近的地方。

在卡連接到主機之前,電容CH以電壓VDD充電,Cc不充電。

當卡剛與主機連接時,卡瞬間短路,電流從CH流向Cc,直到CH的電壓與Cc相等,此時由于CH中充電的能量被移動到Cc,瞬間電壓從Vop略有下降。

這個降電壓在這里定義為Vdrop。

在那之后,電壓回到由電源充電的VDD。

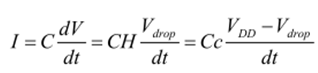

從CH到Cc的浪涌電流計算如下:

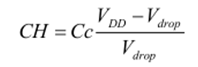

去耦電容CH的計算公式如下:

如果VDD是3.0V。Vdrop為0.3V(最大),以限制電壓降小于VDD的10%。

由于SD內存卡Cc為5uF(最大),CH計算為45uF(最小)。

因此,僅支持SD存儲卡的主機推薦去耦電容為47uF。

SDIO卡Cc定義為10uF(最大),然后計算CH為90uF(最小)。

因此,對于支持SDIO卡的主機,推薦去耦電容為100uF。

去耦電容

4.7uF電容的目的是支持低速浪涌電流。與4.7uF并聯的100nF電容器用于高速浪涌電流。

這兩個電容都可以作為噪聲濾波。

電容器的物理位置應盡可能靠近SD插座VDD和VSS引腳。較小的電容器應靠近SD NAND。

電源開關主要用于SD卡的上電和電源回收。當開關LDO輸出提供給卡時,47uF主要用作4.7uF電容的充電輔助。為了將3伏軌道上的電壓降至最小,47uF充當中間儲層,為4.7uF電容器充電,電源開關未連接到3伏軌道時環繞。

接地將快速可靠地釋放VDD線路上的殘余電壓。這確保了可靠的電源回收。

但是,當開關將卡電源線接地時,作為短路,使充滿電的4.7uF電容放電,產生較大的涌流。

審核編輯 黃宇

-

電路設計

+關注

關注

6689文章

2500瀏覽量

207655 -

SD NAND

+關注

關注

0文章

86瀏覽量

1391

發布評論請先 登錄

相關推薦

SD NAND、SPI NAND 和 Raw NAND 的定義與比較

關于SD NAND 的概述

SD NAND 概述

瀚海微SD NAND之SD 協議(39)SPI模式 Transaction Packets

瀚海微SD NAND之SD 協議(38)寄存器&復位&開解鎖

瀚海微SD NAND之SD 協議(37)SPI總線保護和讀寫

瀚海微SD NAND之SD 協議(36)SPI模式

瀚海微SD NAND之SD 協議(29)硬件接口

瀚海微SD NAND應用之SD協議系統功能和概念 1 基礎知識

淺談SD NAND

瀚海微SD NAND之SD 協議(45)SD電路設計

瀚海微SD NAND之SD 協議(45)SD電路設計

評論