作者:Longley Zhang,AMD工程師;來源:AMD開發(fā)者社區(qū)

就地執(zhí)行(eXecute In Place,下面簡稱XIP),即芯片內(nèi)執(zhí)行,是指應(yīng)用程序可以直接在非易失存儲器或閃存中取指然后譯碼、執(zhí)行,不必再把代碼讀到系統(tǒng)RAM中。它是使用共享內(nèi)存的擴展,以減少所需的總內(nèi)存量。AMD的軟核處理器Microblaze可以通過AXI Quad SPI IP實現(xiàn)XIP的功能。AMD提供參考設(shè)計XAPP1176(見Ref 1,Ref 2),介紹使用 Vivado 通過 AXI Quad SPI 進行就地執(zhí)行(XIP)。用戶可以通過這個參考設(shè)計了解Microblaze實現(xiàn)XIP功能的基本概念和設(shè)計思路。然而這篇文檔使用的Vivado版本是2013.2,這個版本已經(jīng)很舊了,文檔里面提到的一些工具(如:IMPACT) 以及命令(XMCSUTIL)在新版本的Vivado都已經(jīng)不支持了,并且XAPP1176里提供的bootloader比較復(fù)雜。

本博客提供了基于2023.2 Vivado的參考工程,展示如何使用Microblaze就地執(zhí)行(XIP)程序,并提供一個簡單的bootloader。

下面是工程創(chuàng)建流程和程序運行步驟:

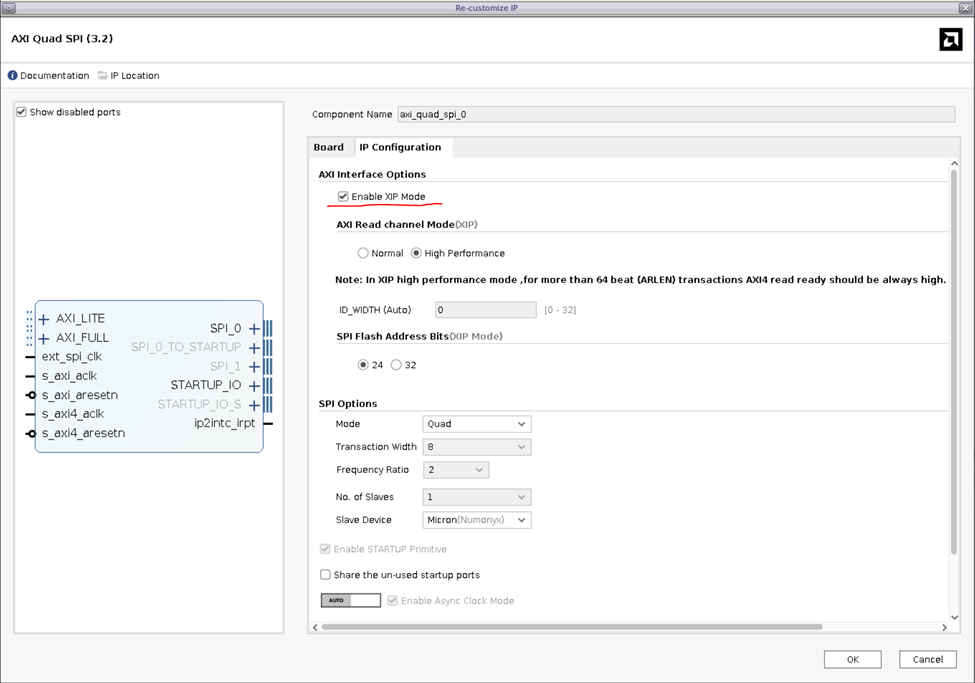

1. 修改2023.2 AC701 Petalinux BSP里自帶的Vivado工程,使能AXI Quad SPI IP里的XIP模式。

或者創(chuàng)建一個基于AC701的Vivado工程運行,然后運行附件的tcl文件。

2. 構(gòu)建Vivado工程,生成bit文件并導(dǎo)出包含bitstream的xsa文件。

3. 在Vitis里,基于導(dǎo)出的xsa文件創(chuàng)建platform工程,創(chuàng)建兩個工程,一個是bootloader,另外一個是XIP的用戶程序。

這個bootloader只是一個運行在BRAM里的簡單程序,作用是把PC跳轉(zhuǎn)到XIP程序的起始位置。

XIP程序可以是任何用戶程序,用戶需要在linker script里把.text等只讀的section放到QSPI flash的地址段,把.data/.bss等讀寫的section放到BRAM。

如果.data section里有已經(jīng)初始化的變量,用戶需要在用戶程序里把.data section復(fù)制到BRAM里。

4. 分別右鍵點擊bootloader工程和XIP工程里的src文件夾,導(dǎo)入附件的工程文件。(在本博客的工程里,bootloader工程文件在bootloader_ar的文件夾里,XIP工程文件在dhry_0文件夾里。)

5. 在XSCT里運行mb-objcopy把xip工程的elf文件轉(zhuǎn)換成bin文件(下面命令把dhry_0.elf轉(zhuǎn)換成dhry_0.b)。

mb-objcopy -O binary -R .vectors.reset -R .vectors.sw_exception -R .vectors.interrupt -R .vectors.debug_sw_break -R .vectors.hw_exception dhry_0.elf dhry_0.b

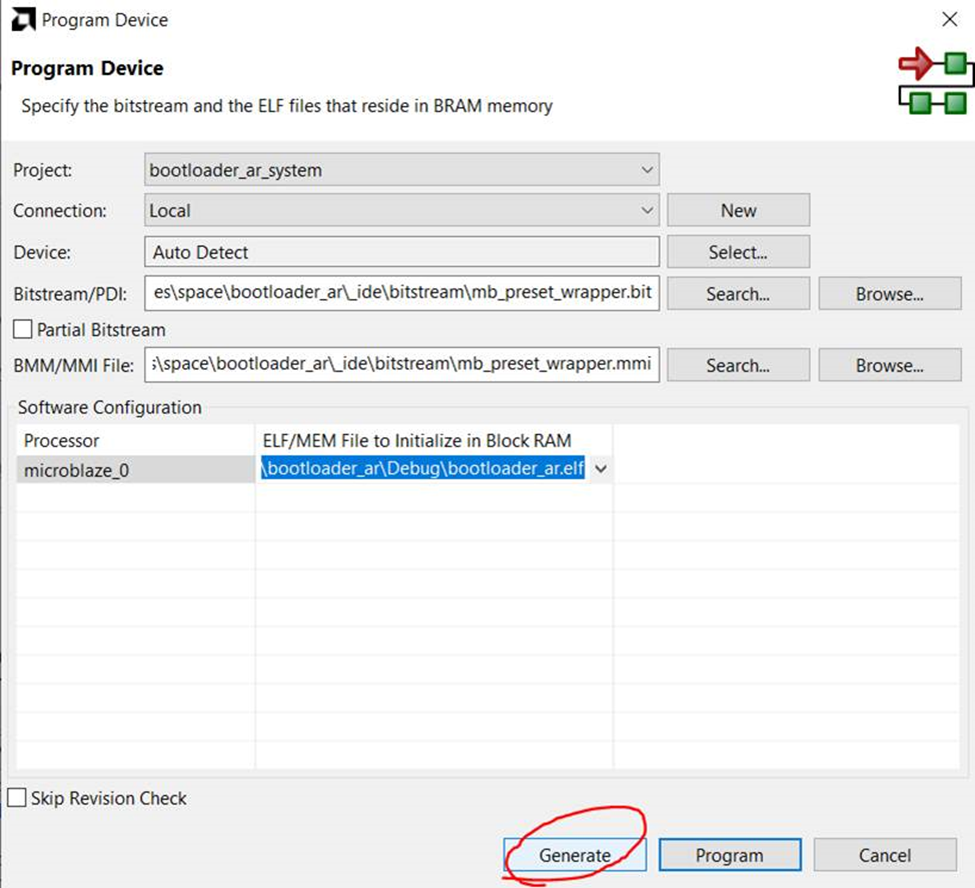

6. 在Vitis里,通過菜單Vitis -> Program Device把bootloader.elf更新到bit文件里,生成新的download.bit。

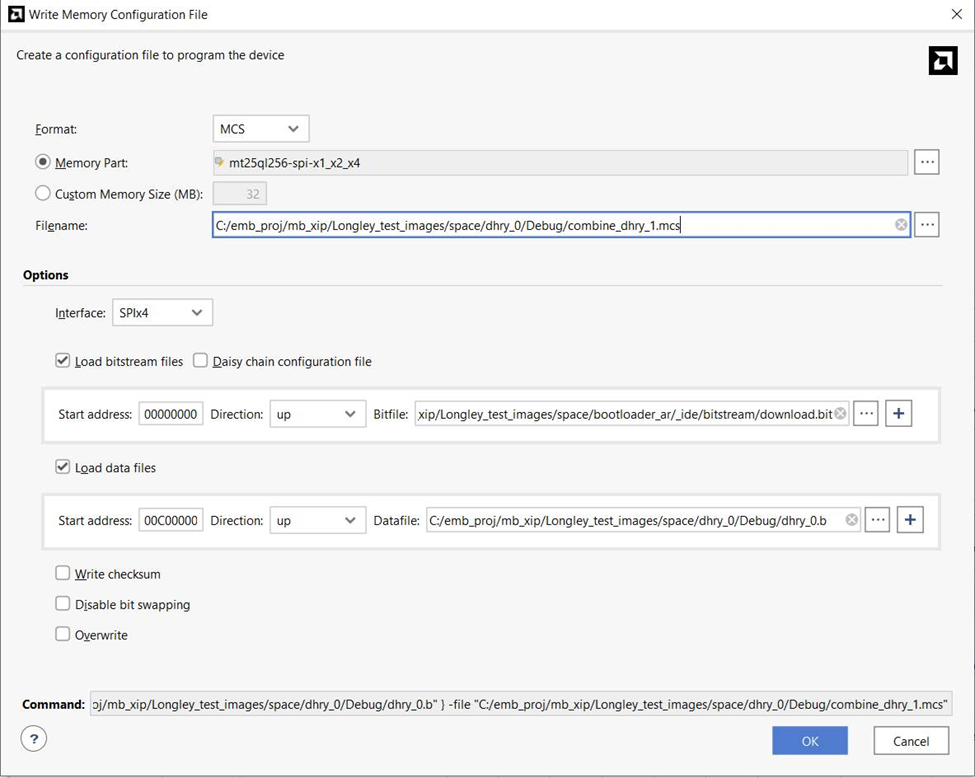

7. 在Vivado里,通過菜單Tools -> Generate Write Memory Configuration File把download.bit和XIP工程的bin文件合并成一個mcs文件(這里相當于XAPP1176里的Merging Two MCS Files)。

8. 把生成的mcs文件燒寫到AC701的QSIP flash里,連接UART線,把AC701設(shè)置為QSPI flash啟動模式并上電啟動。這樣就能看到串口的打印輸出了,輸出內(nèi)容是DHRYSTONE測試的結(jié)果。

-

閃存

+關(guān)注

關(guān)注

16文章

1845瀏覽量

116011 -

存儲器

+關(guān)注

關(guān)注

38文章

7653瀏覽量

167471 -

程序

+關(guān)注

關(guān)注

117文章

3826瀏覽量

83026 -

MicroBlaze

+關(guān)注

關(guān)注

3文章

68瀏覽量

21971

原文標題:如何使用Microblaze 就地執(zhí)行(XIP)程序

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何將AXI VIP添加到Vivado工程中

請問CYW20829能否通過Quad SPI連接固件、用戶數(shù)據(jù)和Quad SPI SRAM?

在AXI QUAD SPI的綜合放置中遇到錯誤

Vivado無法放置任何時鐘資源

[放置30-73]SPI接口IP,如何解決這個嚴重警告?

[放置30-73] axi_quad_spi版本3.2的寄存器'IO1_I_REG'的約束無效

怎么使用AXI Quad SPI IP Core對帶有PROM文件的SPI Flash進行編程

Axi quad spi怎么作為從屬設(shè)備?

如何使用Vivado功能創(chuàng)建AXI外設(shè)

如何使用Vivado Design Suite IP Integrator的調(diào)試AXI接口

基于Vivado/SDK 2018.3的XIP參考設(shè)計

怎么樣利用AXI Quad SPI快速打通Linux至PL端SPI從設(shè)備?

【ZYNQ實戰(zhàn)】利用AXI Quad SPI快速打通Linux至PL端SPI從設(shè)備

使用Vivado通過AXI Quad SPI實現(xiàn)XIP功能

使用Vivado通過AXI Quad SPI實現(xiàn)XIP功能

評論