1、電源需求整理——電源樹(shù)。

我們需根據(jù)電源專(zhuān)題整理出“電源樹(shù)”

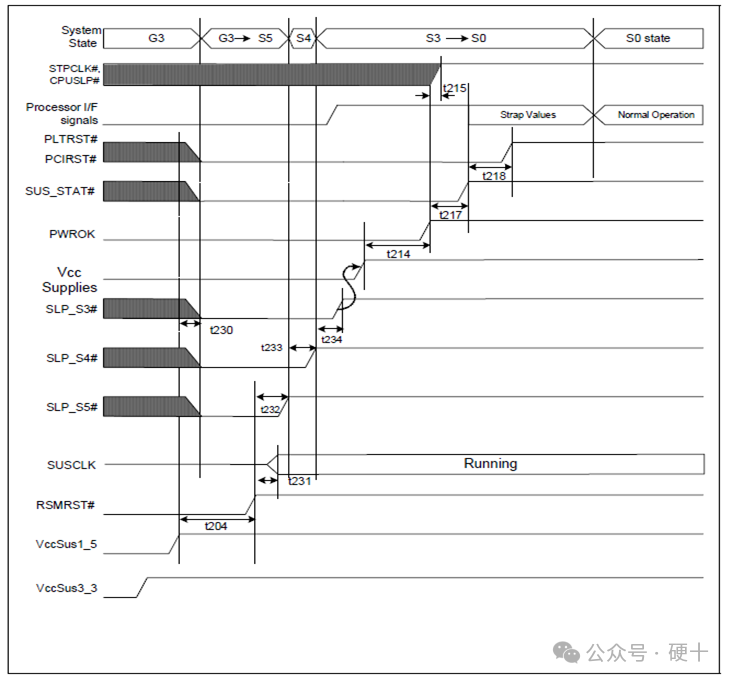

電源專(zhuān)題,需要分析電源需求,每種電源的電壓范圍,電流需求,動(dòng)態(tài)響應(yīng),上電時(shí)序;時(shí)鐘專(zhuān)題,針對(duì)每個(gè)時(shí)鐘的輸入的電平標(biāo)準(zhǔn),頻率,抖動(dòng)等參數(shù),時(shí)鐘時(shí)序,并按照各種時(shí)鐘解決方案進(jìn)行優(yōu)化。每個(gè)管腳怎么用,怎么接,對(duì)接的管腳的電平是否滿(mǎn)足要求,都需要分析清楚并文檔化。例如電源專(zhuān)題:芯片廠家給出的的是一些針對(duì)他自己器件的要求,例如圖是Intel對(duì)其電源上電時(shí)序之間的耦合關(guān)系的要求和一些先后順序的描述。

但是我們?cè)趺磳?shí)現(xiàn)?另外,我們電路板上面還有其他器件,比如網(wǎng)卡、FPGA等等也是復(fù)雜的供電方案、也有一定的上下電時(shí)序要求。并且這些器件之間有些電源是相同電壓的,為了簡(jiǎn)化設(shè)計(jì),絕大多數(shù)情況使用一個(gè)電源給所有相同電壓的器件進(jìn)行供電。例如3.3V電源很可能只有一個(gè)電源輸出,但是要給所有使用了3.3V電壓的器件都供電。這樣就耦合在一起,并且需要考慮所有用電器件的需求,以及他自身的上電時(shí)序要求。

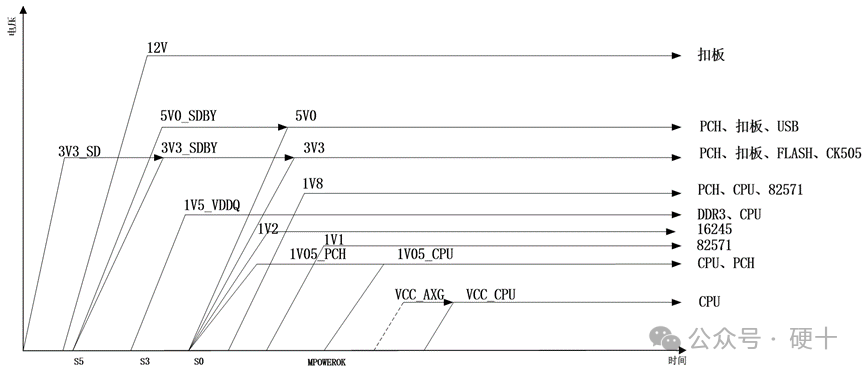

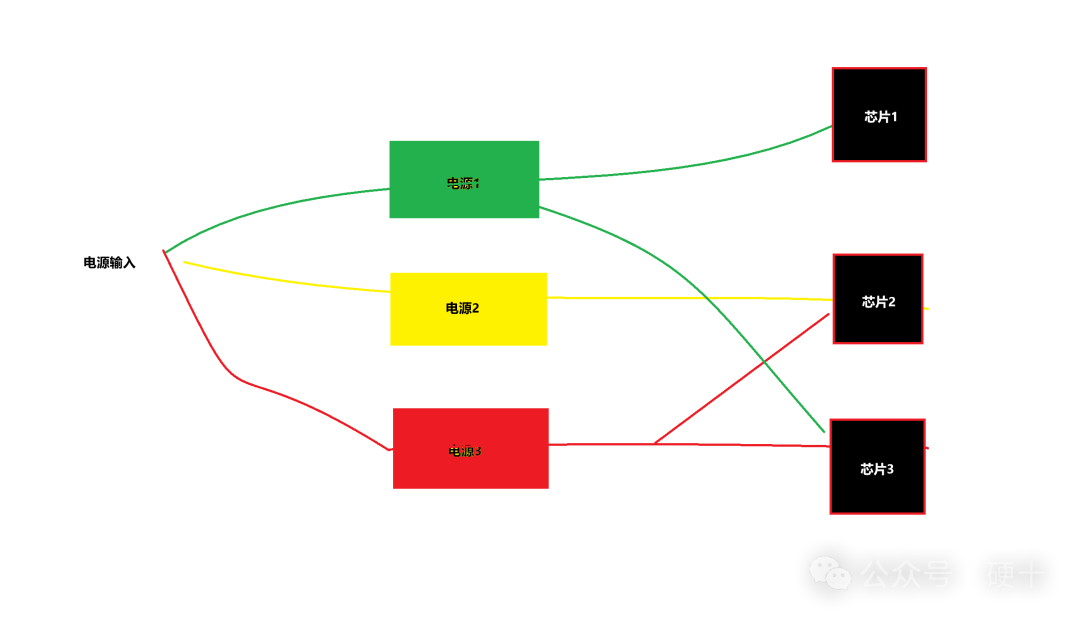

我們會(huì)先梳理出所有器件的用電需求,然后再合并共性需求。整理出整個(gè)單板的供電需求,以及供電時(shí)序的要求,如圖所示。

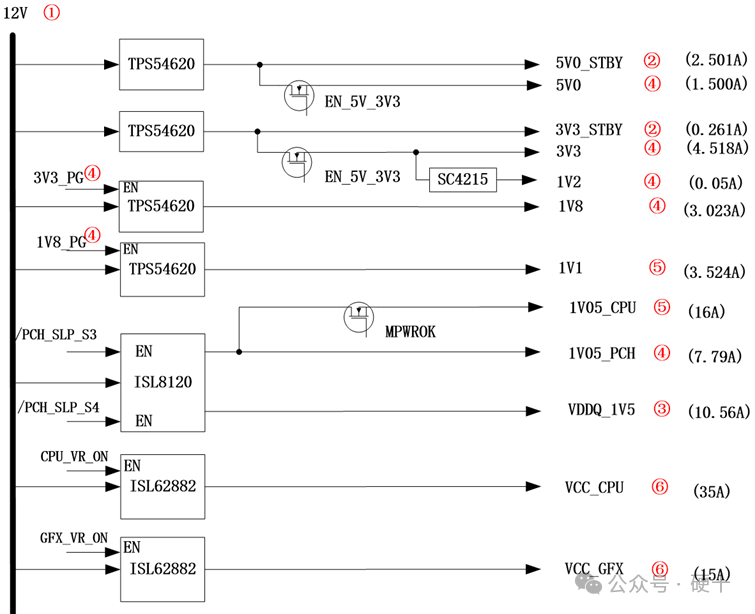

然后再根據(jù)這個(gè)需求,設(shè)計(jì)整板的電源方案,選擇最合理、可靠性、性?xún)r(jià)比的電源方案,實(shí)現(xiàn)我們的整板電源方案。先形成功能框圖,進(jìn)行評(píng)審。

關(guān)鍵圖表和文檔

電源需求分析表:列出所有器件的電源需求,包含電壓范圍、電流需求、動(dòng)態(tài)響應(yīng)和上電時(shí)序等信息。

共性需求合并圖:展示不同電壓的器件合并后的供電需求。

整板電源方案框圖:展示整板的電源架構(gòu)設(shè)計(jì),包括各個(gè)電源模塊和它們之間的連接關(guān)系。

上電時(shí)序圖:詳細(xì)說(shuō)明各個(gè)電源模塊的上電順序和時(shí)序要求,確保滿(mǎn)足所有器件的需求。

至此,整理清楚電源設(shè)計(jì)的需求。

2、根據(jù)電源輸入和輸出情況,思考電源“模塊”的布局

電源的輸入一般是一種電源,是由背板、適配器、PoE、USB等形式進(jìn)行直流輸入。一般來(lái)說(shuō),電源的輸入比較單一,或者多路輸入,但是進(jìn)行合路設(shè)計(jì)。

電源的輸出,就是上一小節(jié)整理的電源用電器件的各種電源種類(lèi)的整理合并。然后我們根據(jù)器件的位置關(guān)系,整理出大致的一個(gè)器件布局。

當(dāng)然器件布局的分布跟很多因素有關(guān),此處我們不展開(kāi)。但是我們?cè)趦?yōu)化走線、散熱、結(jié)構(gòu)、干擾等因素之后。我們重點(diǎn)看一看,主芯片的“大電流”電源的位置。

我們首先應(yīng)該優(yōu)先考慮主芯片及配套大功率芯片(例如:DDR)的電源管腳分布。

特別是我們需要根據(jù)主芯片的電源分布情況,考慮“關(guān)鍵電源平面”的分配。我們需要考慮各種電源從哪個(gè)平面流入CPU。在完成“流入”這個(gè)任務(wù)的時(shí)候,需要盡可能的做到:

1、各個(gè)電源平面減小“耦合”,避免各種電源平面交織在一起。

2、用最小的路徑完成任務(wù),避免“繞遠(yuǎn)路”。

3、減小“換層”。

4、關(guān)鍵的電源盡可能“完整的電源平面”。

所以我們?cè)趧?dòng)手布放“DC/DC”電源的時(shí)候,要先考慮電源流向,做好規(guī)劃。

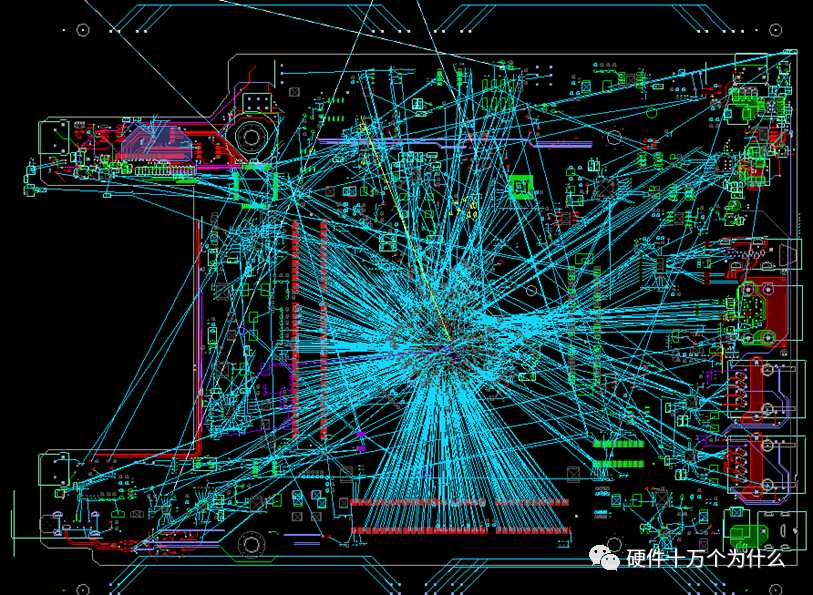

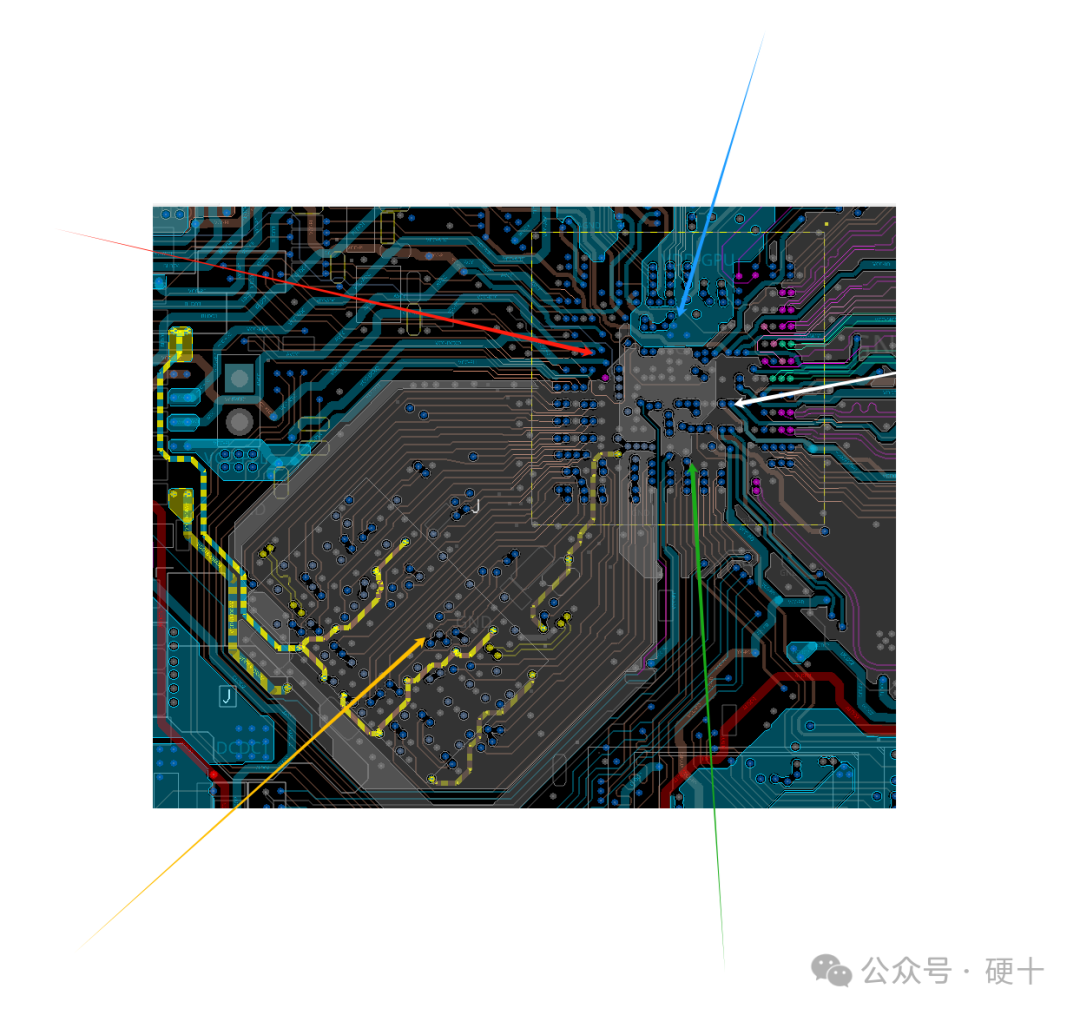

硬件工程師需要構(gòu)想出整個(gè)供電的拓?fù)洌鎸?shí)的拓?fù)浔壬蠄D復(fù)雜很多。

3、輸入電源不要滿(mǎn)板跑

這是一條很簡(jiǎn)單的原則,但是容易被大家忽略。

第一、輸入電源是外部供電,其引入的干擾不可控;

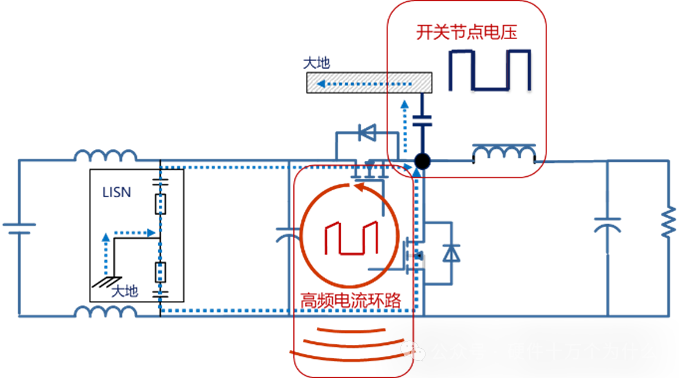

第二、輸入電源給每個(gè)DC/DC供電,每個(gè)DC/DC的輸入電容都往往都會(huì)有大功率的電流跳變,需要控制這個(gè)電流環(huán)的大小。

第三、即使通過(guò)空電流環(huán)的大小,輸入電源與DC/DC之間會(huì)仍然會(huì)形成跳變的電流環(huán),形成一個(gè)感性干擾源。

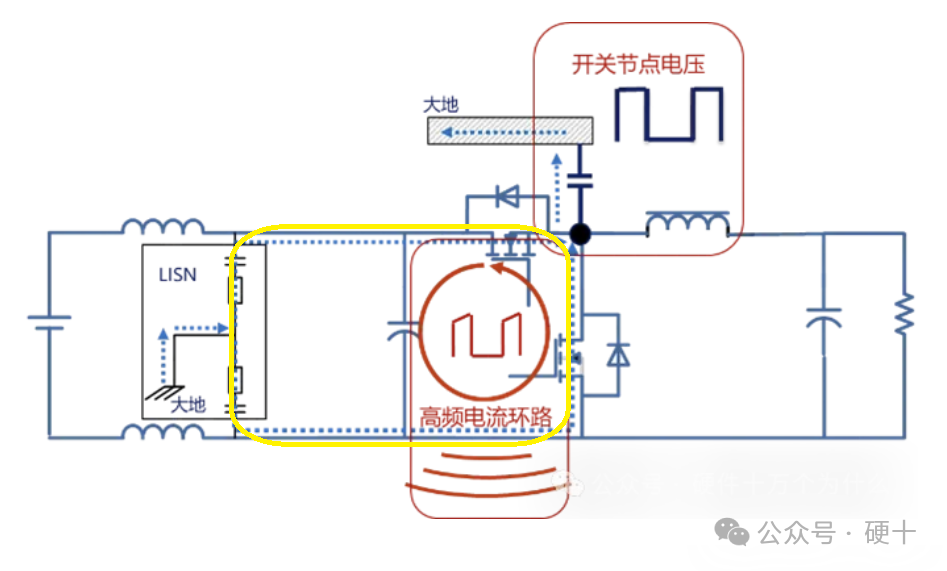

我們既要控制紅色的環(huán),也要控制黃色的環(huán)。

4、Buck電路的輸入電容盡可能靠近上管和下管。

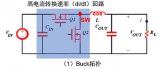

就是上圖中描述的高頻電流環(huán)要盡可能的小。

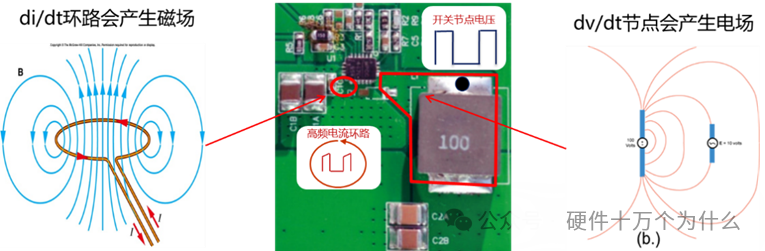

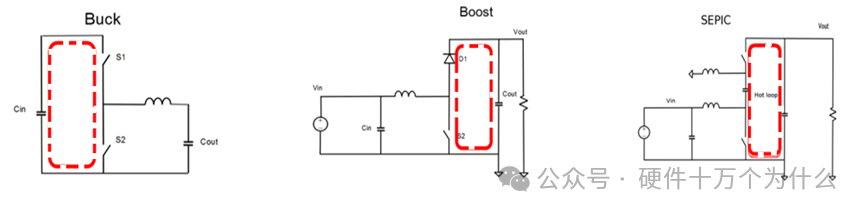

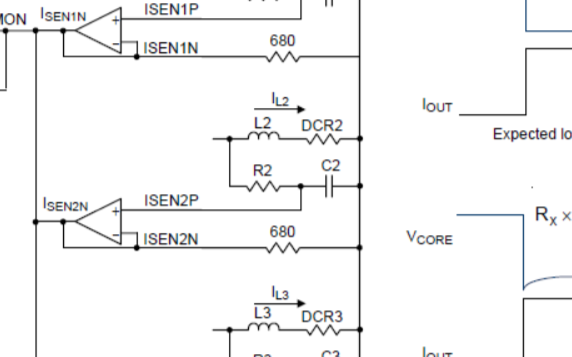

首先,我們需要找出不同拓?fù)涞母哳l電流環(huán)路。如圖所示,虛線的環(huán)路便是di/dt變化比較大的電流高頻環(huán)路,可以看到BUCK電路,電流高頻環(huán)路存在于輸入電容和兩個(gè)開(kāi)關(guān)管(或者一個(gè)開(kāi)關(guān)管和一個(gè)二極管)形成的閉合環(huán)路,而B(niǎo)OOST電路作為對(duì)偶拓?fù)洌娏鞲哳l環(huán)路存在于輸出電容和兩個(gè)開(kāi)關(guān)管。而SEPIC電路的電流高頻環(huán)路存在于兩個(gè)開(kāi)關(guān)管和兩個(gè)電容形成的環(huán)路中,如圖所示。

可以看到高頻電流環(huán)路存在于開(kāi)關(guān)管和連接開(kāi)關(guān)管的電容形成的回路,因?yàn)殡娏髯兓顒×业耐ǔT陂_(kāi)關(guān)管之間,電流是在兩個(gè)開(kāi)關(guān)管之間切換,而通常電感由于電流不能突然變化,di/dt受到限制,而不是我們重點(diǎn)考察高頻電路環(huán)路的部分。

圖幾種拓?fù)涞母哳l電流環(huán)路

找到高頻電流環(huán)路后,我們需要抑制該噪聲源引起的近場(chǎng)磁場(chǎng)。最有效的方式就是減少該環(huán)路的面積,通常電流大小需要滿(mǎn)足功率輸出的要求,不能隨意減小。

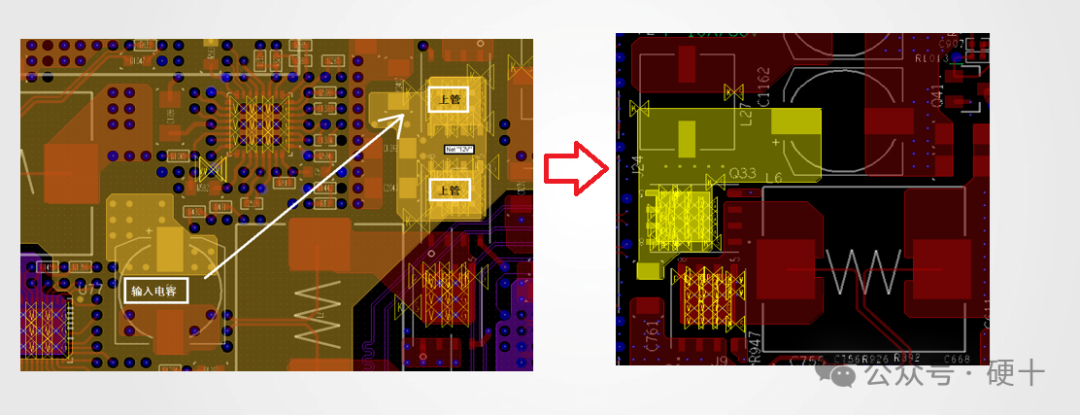

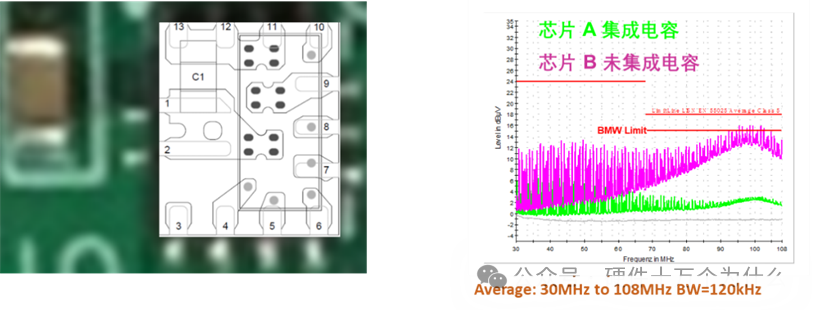

對(duì)于高頻電流環(huán)路來(lái)說(shuō),減小環(huán)路面積還要特別注意輸入電容的放置,如圖所示,將電容放置在芯片背面(減小了和開(kāi)關(guān)管的距離),所測(cè)得噪聲大小要遠(yuǎn)小于其他兩種方式(電容放在側(cè)面和用較長(zhǎng)的引線連接電容)。

不同電容情況的輻射對(duì)比

隨著先進(jìn)封裝的發(fā)展,更多的芯片將輸入電容集成到芯片中,可以進(jìn)一步減小高頻環(huán)路的面積,以獲得更好的EMC特性,如圖所示。

芯片集成電容的輻射情況

分別測(cè)試集成電容和未集成電容的兩顆芯片A和B,同樣的芯片和PCB布局,可以看到CISPR25傳導(dǎo)高頻部分,集成電容的芯片具有更低的高頻噪聲,具有較大的優(yōu)勢(shì)通過(guò)傳導(dǎo)測(cè)試。

5、去耦電容盡可能靠近“用電器件”

去耦電容式干嘛用的?我們搞清楚了,也就知道如何布放了

最終我們要求在用電器件的接收端接收到良好質(zhì)量的電源,我們需要整個(gè)電源平面的所有的噪聲。對(duì)于電源的噪聲來(lái)源:穩(wěn)壓芯片輸出的電壓不是恒定的,會(huì)有一定的紋波;穩(wěn)壓電源無(wú)法實(shí)時(shí)響應(yīng)負(fù)載對(duì)于電流需求的快速變化。穩(wěn)壓電源響應(yīng)的頻率一般在200kHz以?xún)?nèi),能做正確的響應(yīng),超過(guò)了這個(gè)頻率則在電源的輸出短引腳處出現(xiàn)電壓跌落;負(fù)載瞬態(tài)電流在電源路徑阻抗和地路徑阻抗產(chǎn)生壓降;外部的干擾。

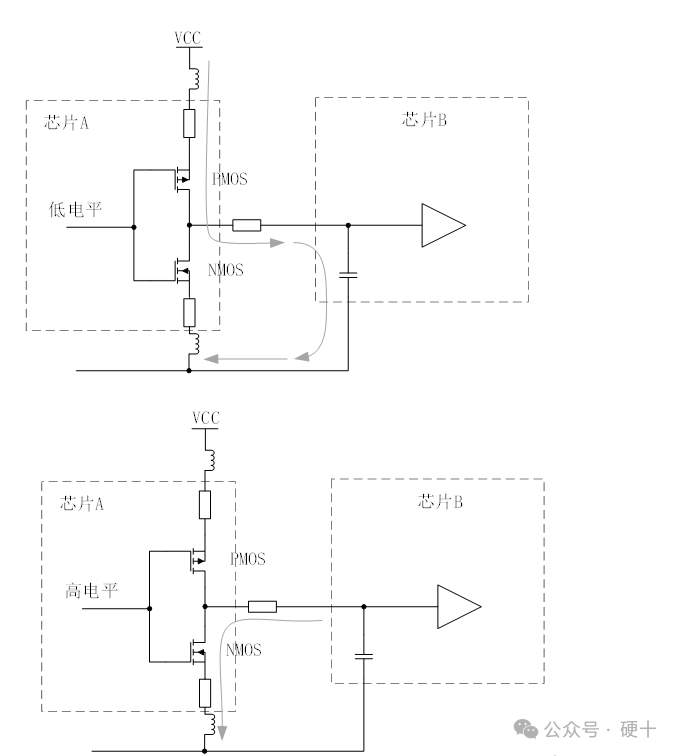

此處提到“負(fù)載瞬態(tài)電流”,這個(gè)問(wèn)題不是由電源輸出端的電源模塊或者電源芯片所產(chǎn)生,而是由用電負(fù)載自身的負(fù)載變化所產(chǎn)生,這個(gè)負(fù)載變化又是由于大量數(shù)字信號(hào)在“跳變”所產(chǎn)生。集成電路是由無(wú)數(shù)的邏輯門(mén)電路組成,基本的輸出單元我們可以看成是CMOS反相器,如圖所示。

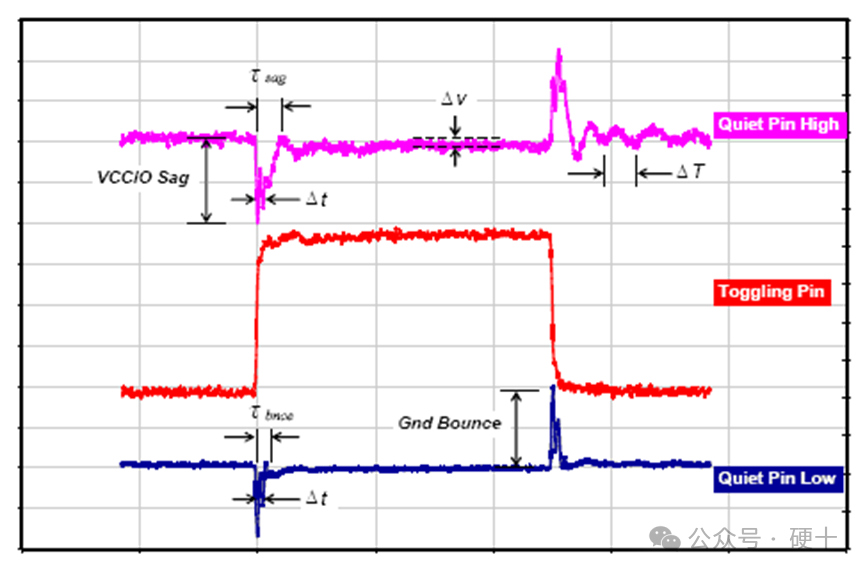

當(dāng)控制信號(hào)是一個(gè)低電平的時(shí)候,上面PMOS打開(kāi),此時(shí)輸出是高電平。打開(kāi)的瞬間,VCC通過(guò)LVCC和R,對(duì)芯片B的輸入管腳進(jìn)行充電。當(dāng)控制信號(hào)是一個(gè)高電平的時(shí)候,下面的NMOS打開(kāi),此時(shí)輸出的是低電平。打開(kāi)的瞬間,芯片B的輸入管腳儲(chǔ)存的電量經(jīng)過(guò)NMOS進(jìn)行放電。在CMOS反相器輸出狀態(tài)發(fā)生變化的時(shí)候,流過(guò)的電流正是變化的電流。于是,在走線、過(guò)孔、平面層和封裝(鍵合引線、引腳)等這些具有電感的連接部件上,便會(huì)感應(yīng)出電壓。例如標(biāo)準(zhǔn)的GND地電位應(yīng)該是0V,但是芯片與地之間的鏈接部件存在電感,就會(huì)感應(yīng)出電壓VGND,那么芯片上的“地”電位就被抬高了,高于0V。如圖13.2所示,當(dāng)CMOS輸出信號(hào)同時(shí)從低電平到高電平切換時(shí),VCC上會(huì)觀測(cè)到一個(gè)負(fù)電壓的噪聲,同時(shí)也會(huì)影響到GND,并有可能引起一個(gè)振蕩。當(dāng)輸出信號(hào)從高電平到低電平切換時(shí), GND上會(huì)觀測(cè)到一個(gè)正電壓的噪聲,同時(shí)也會(huì)影響到VCC,并有可能引起一個(gè)振蕩。

一個(gè)CMOS會(huì)造成這樣的干擾,如果有很多CMOS同時(shí)工作,用電器件對(duì)電源平面和GND平面造成的干擾會(huì)很?chē)?yán)重。這就是隨著芯片的管腳越來(lái)越多,電流越來(lái)越大,集成度越來(lái)越高造成的我們不得不非常重視電源完整性。

(1)芯片的集成度越來(lái)越大,芯片內(nèi)部晶體管數(shù)量也越來(lái)越大;晶體管組成內(nèi)部的門(mén)電路組合邏輯 延遲線 狀態(tài)機(jī)及其它邏輯。

(2)芯片外部電源引腳提供給內(nèi)部晶體管一個(gè)公共的電源節(jié)點(diǎn),當(dāng)晶體管狀態(tài)轉(zhuǎn)換時(shí)必然引起電源噪聲在芯片內(nèi)部傳遞。

(3)內(nèi)部晶體管工作需要內(nèi)核時(shí)鐘或是外部時(shí)鐘同步,但是由于內(nèi)部延遲及各個(gè)晶體管不可能?chē)?yán)格同步,造成部分晶體管完成狀態(tài)轉(zhuǎn)換,另一部分可能處于轉(zhuǎn)換狀態(tài),這樣一來(lái)處于高電平門(mén)電路的電源噪聲會(huì)傳到其它門(mén)電路的輸入部分。

經(jīng)過(guò)上面分析,大家也非常能夠理解,為什么要將去耦電容靠近用電器件的電源管腳放置了。

去耦電容(decoupling capacitor)通常被用于電源系統(tǒng)中,目的是提供對(duì)電源噪聲的短時(shí)、高頻響應(yīng),以維持穩(wěn)定的電源電壓供應(yīng)給集成電路(IC)或其他用電器件。將去耦電容放置在靠近用電器件的位置有幾個(gè)關(guān)鍵的理由:

1. 降低電感效應(yīng):在電源供電線路中,電源線和地線都有一定的電感。當(dāng)用電器件瞬時(shí)需要大電流時(shí),由于電感的存在,線路中會(huì)產(chǎn)生電壓降,導(dǎo)致用電器件供電電壓下降。通過(guò)在用電器件附近放置去耦電容,可以在用電瞬間提供瞬時(shí)電流,抵消電感引起的電壓降。

2. 降低電源回路的阻抗:去耦電容在高頻上具有較低的阻抗。將去耦電容放置在用電器件附近,可以降低電源回路的總阻抗,使電源更容易提供瞬時(shí)高頻電流需求。

3. 減小電壓波動(dòng)的傳播:電源線路上的電壓波動(dòng)會(huì)沿著線路傳播。通過(guò)將去耦電容靠近用電器件,可以減小電壓波動(dòng)的傳播距離,確保用電器件獲得更穩(wěn)定的電源電壓。

4. 最小化電源噪聲對(duì)鄰近電路的影響:去耦電容可以吸收電源線上的噪聲,防止噪聲通過(guò)電源線傳播到鄰近的電路。這對(duì)于保持鄰近電路的穩(wěn)定性和性能至關(guān)重要。

因此,為了最大程度地提高去耦電容的效果,它通常被放置在用電器件附近,以確保對(duì)瞬時(shí)電流需求的快速響應(yīng),并最小化電源系統(tǒng)中的電感和電阻的影響。

小封裝和小容值的去耦電容更應(yīng)該靠近電源管腳的主要原因與這些電容的高頻響應(yīng)和電流傳輸?shù)奶匦杂嘘P(guān)。

高頻響應(yīng):小封裝和小容值的電容通常在高頻范圍內(nèi)具有更好的響應(yīng)特性。由于高頻信號(hào)的波長(zhǎng)短,電容的物理尺寸和電感對(duì)其阻抗的影響較小。因此,小型電容更能夠提供對(duì)高頻噪聲的有效去耦。

電流傳輸速度:小封裝的電容通常具有較低的等效電感,使其能夠更快地傳輸電流。在高頻情況下,電流需要迅速響應(yīng)用電器件的需求。通過(guò)將小電容靠近電源管腳,可以降低電流路徑的電感,提高對(duì)瞬時(shí)電流需求的快速響應(yīng)能力。

電源噪聲的局部處理:小容值的電容主要用于處理局部的、瞬時(shí)的高頻噪聲。通過(guò)將這些電容靠近電源管腳,可以在電源引入電路板或芯片的地方提供即時(shí)的去耦效果,而不是在較遠(yuǎn)的位置。這有助于保持用電器件的電源穩(wěn)定性,減小對(duì)整個(gè)電路的影響。

采用小封裝和小容值的去耦電容靠近電源管腳,有助于優(yōu)化高頻噪聲去耦效果,并提供對(duì)瞬時(shí)電流需求的快速響應(yīng)。這樣的設(shè)計(jì)有助于維持用電器件的穩(wěn)定性和性能。

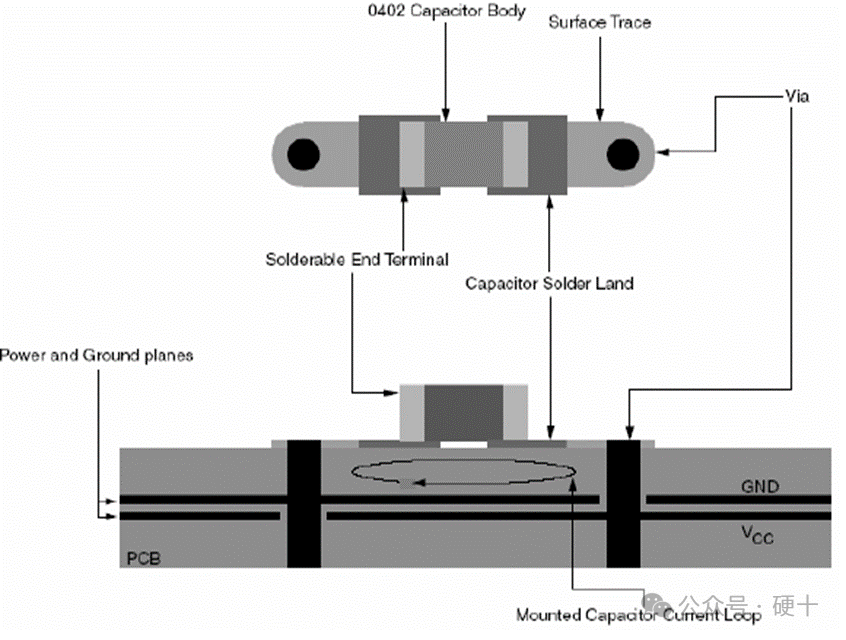

安裝電容時(shí),要從焊盤(pán)拉出一下段引線通過(guò)過(guò)孔和電源平面連接,接地段也一樣。則電容的電流回路是:電源平面→過(guò)孔→引出線→焊盤(pán)→電容→焊盤(pán)→引出線→過(guò)孔→低平面。

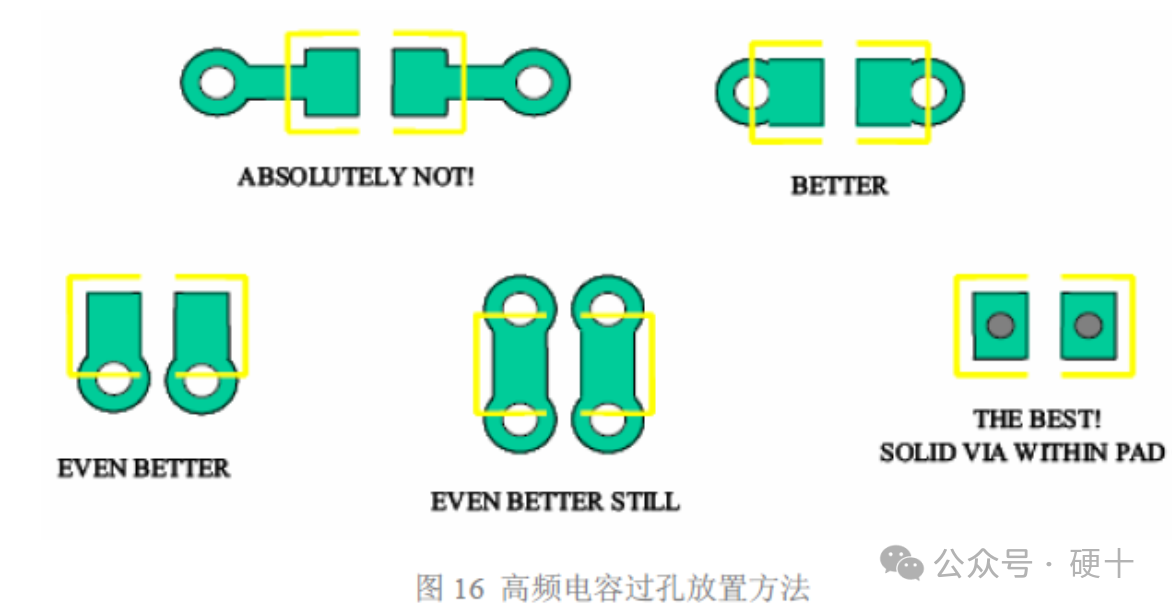

放置過(guò)孔的基本原則就是讓這一環(huán)路面積最小,減小寄生電感。下圖顯示幾種安裝方法。

?第一種方法從焊盤(pán)引出很長(zhǎng)的線然后連接到過(guò)孔,這會(huì)引入很大的寄生電感,一定要避免這樣做。

?第二種方法在焊盤(pán)二端打過(guò)孔,比第一種方法路面積小的多,寄生電感也較小,可以接受。

?第三種方法在焊盤(pán)側(cè)面打孔,進(jìn)一步減小了環(huán)路面積,寄生電感比第一個(gè)更小,是比較好的方法。

?第四種方法焊盤(pán)二側(cè)面打孔,和第三種方法相比,電容的每端都是通過(guò)并聯(lián)的過(guò)孔接入電源和地平面,比第三種的寄生電感還小,只要空間允許,盡量使用。

?最后一種方法在焊盤(pán)上直接打孔,寄生電感最小,但是PCB需要做塞孔處理,否則焊接會(huì)出現(xiàn)漏錫的情況。

-

電源

+關(guān)注

關(guān)注

185文章

18275瀏覽量

255025 -

pcb

+關(guān)注

關(guān)注

4354文章

23421瀏覽量

406838 -

布局

+關(guān)注

關(guān)注

5文章

272瀏覽量

25283

原文標(biāo)題:PCB布局與電源設(shè)計(jì)

文章出處:【微信號(hào):晶揚(yáng)電子,微信公眾號(hào):晶揚(yáng)電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

電源的PCB布局要點(diǎn)

PCB布局-地與電源等(47頁(yè)P(yáng)PT)

PCB板布局時(shí)的電源干擾與抑制

優(yōu)化電源模塊的最佳PCB布局方法

如何做好非隔離式開(kāi)關(guān)電源的PCB布局

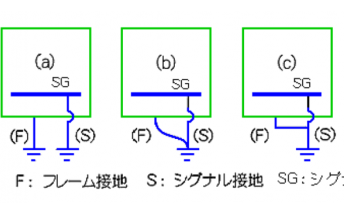

PCB布局的接地和電源的理解原理說(shuō)明

G-NAVP TM控制拓?fù)涞脑O(shè)計(jì)方法和PCB布局規(guī)則

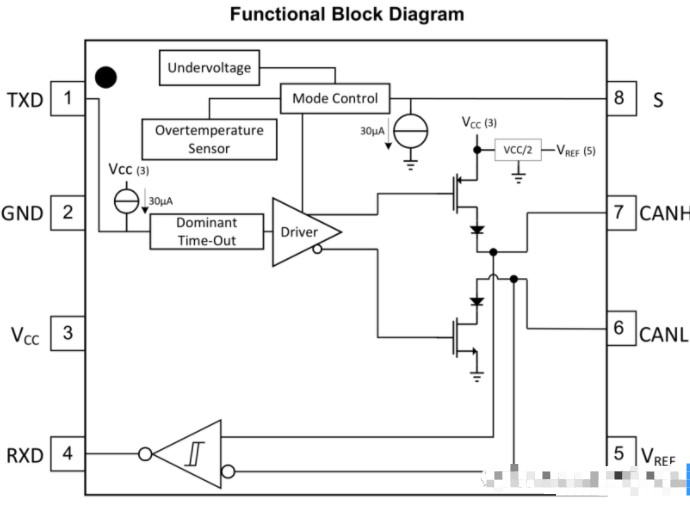

分享一個(gè)CAN收發(fā)器芯片SN65HVD1050

DC電源模塊的 PCB設(shè)計(jì)和布局指南

PCB布局與電源如何設(shè)計(jì)

PCB布局與電源如何設(shè)計(jì)

評(píng)論