Microsemi 于 2017 年開始在其 FPGA 中提供 RISC-V 軟核,Lattice 于 2020 年開始提供,英特爾 (Altera) 于 2021 年開始提供,因此 Xilinx 是最后一家這樣做的主要供應商(2024年5月30日)。

Microsemi 和 Gowin 的 FPGA 中也有 RISC-V 硬核,類似于 Zynq。對于 Microsemi 來說,由五個 64 位 SiFive U54/S51 內核組成的集群(四個支持 Linux,一個“real-time”),根據FPGA等級分別以 600 或 666 MHz 運行,基本上是 FPGA 中降級的 HiFive Unleashed。

所以目前FPGA廠商不管硬核或者軟核都向RISC-V靠攏,對于一些“新”廠商,可以理解;對于像Xilinx或者Altera這種老牌廠商本身自己有基于RISC的軟核,為什么也向RISC-V發展呢?

下面我們先簡單看下RISC-V的發展,然后再分析一下這些FPGA廠商為什么選擇RISC-V。

RISC-V 發展

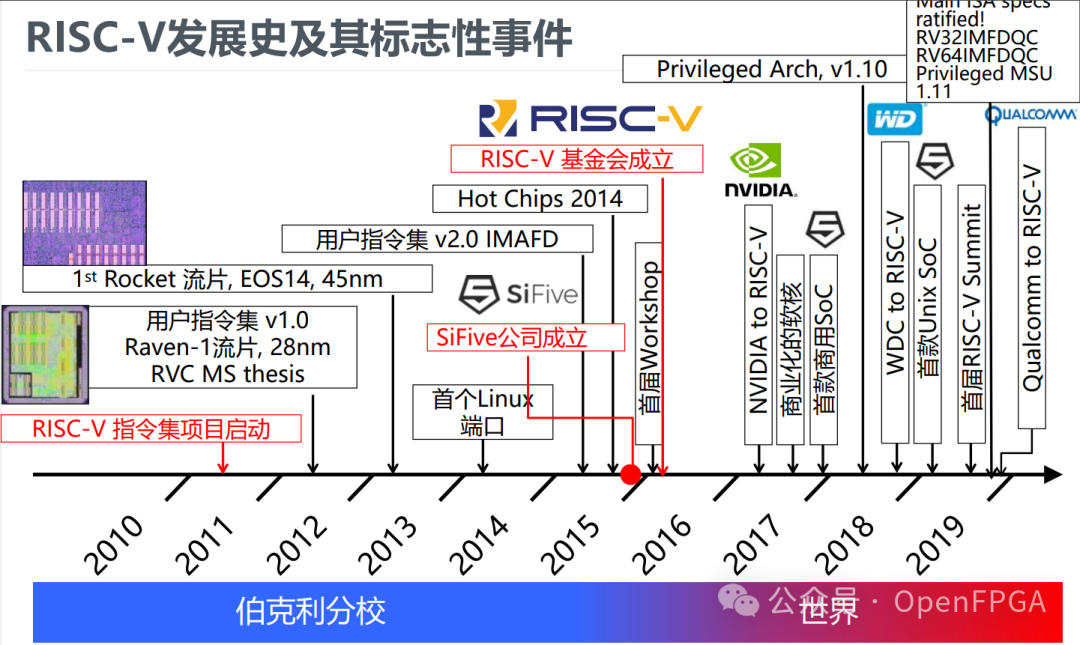

RISC-V(英語發音為“risk-five”)是一個基于精簡指令集(RISC)原則的開源指令集架構(ISA),簡易解釋為與開源軟件運動相對應的一種“開源硬件”。該項目于2010年在加州大學伯克利分校啟動,但許多貢獻者是該大學以外的志愿者和行業工作者。

其發展史及其標志性事件如下圖所示:

目前已經有很多大公司加入到RISC-V“大家庭”中了,下面列舉了部分廠商:

RISC-V VS RISC VS ARM

乍一看,很多人可能會認為 RISC-V 是 RISC 的變體,而 RISC 是一種指令集架構。畢竟,它們的名稱相似,因此很容易造成混淆。但這與事實相去甚遠。下面我們簡單介紹一下RISC-V和RISC,就會明白他們真正的區別。

什么是 RISC?

其實 RISC 是一個廣義術語,意為“精簡指令集計算機”。基本上,RISC 計算機本質上是為運行更簡單的單個指令而設計的。與 CISC(復雜指令集計算機)相比,RISC 處理器對幾乎所有指令都使用統一的指令長度。相比之下,CISC 指令更復雜,可以執行低級和多步驟操作。

簡單來說,RISC 處理器可以執行更簡單、統一的指令,而 CISC 可以執行復雜度和范圍各不相同的指令。每個 RISC 指令一次只能執行一件事,而 CISC 指令可以同時執行多件事。由于指令以更簡單的代碼編寫,并且本質上更簡單,因此 RISC 處理器通常需要更多指令才能完成與 CISC 處理器相同的任務。可以通過提高 RISC CPU 使用流水線執行這些任務的速度來抵消這種差異。由于它們更簡單,RISC 處理器的設計速度也可以比 CISC 處理器更快,并且可以運行更高效的代碼。

由于 RISC 本身不是一種架構,而是一個廣義的術語,因此許多 CPU 架構都可以被視為 RISC。最著名的 RISC處理器架構之一是 ARM,它為我們的智能手機以及一些筆記本電腦和計算機提供支持。其他包括 PowerPC,它長期用于 Apple 電腦和游戲機。同時,x86 可以被視為 CISC 設計,因為它更復雜。

RISC 一詞是由加州大學伯克利分校的 David Patterson 在 1980 年至 1984 年間領導的伯克利 RISC 研究項目創造的。事實證明,該項目非常成功,而“RISC”一詞后來涵蓋了所有精簡指令集計算機 - 甚至斯坦福大學在同一時間開發的競爭性 MIPS 項目最終也被稱為 RISC 架構。至于那個特定的伯克利項目,它后來被 Sun Microsystems 開發的 SPARC 微架構所采用 - 該架構最終成為我們智能手機中 ARM 架構的靈感來源。

什么是 RISC-V?

雖然 RISC 本身并不是一個特定的架構,但可能對一種使用 RISC 名稱的架構感到困惑,那就是 RISC-V。它是由加州大學伯克利分校開發的指令集架構 (ISA),旨在體現 RISC 處理器的原理,同時也是一個開源標準。雖然最著名的 RISC 架構 ARM 是專有的,需要芯片制造商的許可,但 RISC-V 是免費的,一般來說,每個人都可以免費使用。

但與 ARM 不同的是,RISC-V 的開發和發布旨在推出一種開源、可擴展且可部署在任何設備上而無需支付任何版稅的 CPU 設計。據設計人員稱,擁有一個免費使用的 CPU 架構可以大大降低軟件成本。

所以我們對比 RISC 和 RISC-V 并沒有什么意義,我們簡單對比一下ARM VS RISC-V。

建模與架構

從歷史上看,ARM 一直主導著微處理器市場,從低功耗設備到高性能處理器。這主要歸功于其許可模式,該模式允許各公司授權 IP 并根據自己的應用進行定制。此外,ARM 還開發了多個處理系列,例如用于高性能應用的 Cortex-A、用于實時應用的 Cortex-R 和用于節能應用的 Cortex-M — 每個系列都成為各種應用的非官方認可的性能標準。

另一方面,RISC-V 架構的靈感來源于 ARM 的專有建模。伯克利的研究人員最初將該架構作為一種開源替代方案,以促進技術創新。自那以后,它受到了谷歌和 Nvidia 等多家大型科技公司的青睞。

ARM 擁有成熟的軟件和硬件,可以幫助公司加快開發周期。它還擁有一系列具有成熟功能集的選擇。另一方面,RISC-V 的架構提供了 ARM 設備無法提供的靈活性和一定程度的定制性。考慮到原始性能,ARM 將勝過任何 RISC-V 處理器。盡管 ARM 繼續保持其性能領先地位,但事實證明 RISC-V 可以提供更高的計算密度。這意味著將獲得具有相同性能的更小芯片。這在許多應用中都是有利的,例如智能手表等可穿戴設備。

開放性和許可

RISC-V 和 ARM 都是指令集架構 (ISA)。但它們的主要區別在于 RISC-V 是開源 ISA,而 ARM 是私有 ISA (使用需要授權)。

指令集

RISC-V 具有固定的指令集架構,其中包含基本整數指令集和可選擴展指令集,用于浮點運算、矢量處理等功能。ARM 具有多個指令集,包括 ARMv7、ARMv8 和各種擴展,如用于 SIMD(單指令、多數據)操作的 NEON。

靈活性和定制性

RISC-V 具有更大的靈活性和定制性,因為它是開源的,使設計人員能夠根據自己的特定需求定制 ISA。ARM 雖然通過其擴展提供了一定程度的可配置性,但由于其專有性質而受到限制。

生態系統和行業

ARM 擁有完善的生態系統,包括各種處理器、開發工具和來自不同供應商的支持。它廣泛應用于移動設備、嵌入式系統,并越來越多地用于服務器和數據中心。RISC-V 的生態系統仍在發展,但已獲得顯著的關注,尤其是在學術界、研究界和初創公司。它也在物聯網、邊緣計算和一些服務器應用中受到關注。

性能和能效

ARM 一直將能效作為重點關注領域,并占據市場主導地位。他們已經提供了專注于低功耗設備的能效和易用性的選項。此外,他們還提供適用于手機等高端應用的硬件浮點和DSP 擴展選項。

還恰好有大量的節能功能可用。其中一些包括動態電壓和頻率調整,允許處理器根據實時要求降低或增加芯片的電壓和時鐘。另一方面,RISC-V 允許更小的硅片占用空間,這將使其具有功耗優勢。此外,固定的 32 位指令格式和 16 位壓縮指令擴展可以幫助其實現更節能的代碼實現。總體而言,雖然 RISC-V 提供了降低功耗設備的潛力,但它還沒有達到這個水平。在 RISC-V 開始從 ARM 手中奪取市場份額之前,仍需要投入大量工作和時間。

成本和可訪問性

由于無需支付與 ARM 相關的許可費用,因此實施 RISC-V 內核對公司而言可能更具成本效益。ARM 內核通常需要支付許可費用,這會增加采用 ARM 架構的設備的生產成本。

指令編碼

RISC-V 使用定長指令編碼,簡化了解碼邏輯。ARM 采用可變長度指令編碼,允許更緊湊的代碼,但解碼邏輯可能更復雜。

FPGA廠商擁抱RISC-V

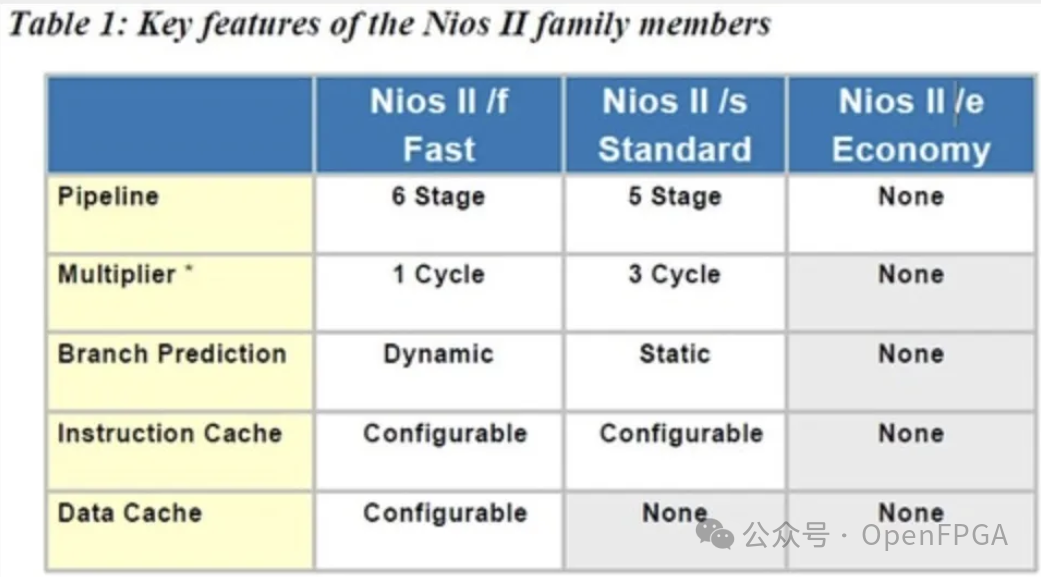

首先,不論Altera的niso還是Xilinx 的 microblaze甚至Lattice的LatticeMico8/32 都是基于RISC的,那為什么目前主流FPGA廠商基本都推出了基于RISC-V的硬核或者軟核,個人認為這些廠商主要從以下幾點考慮:

創新和發展

RISC-V處于剛起步階段,其發展潛力很大,可以在降低功耗、性能、安全等方面進行優化,同時又可以保持與其他設計的兼容性。同時RISC-V還支持需要加速和特殊功能的情況下自定義指令。當然,其未來怎么發展無從得知,現在加入這個領域,能占有一席之地。

RISC軟核的疲態

不論NISO還是MicroBlaze都已經發展了很多年了,經過多年的發展,目前兩者都是比較穩定的,但是FPGA本身的結構決定了其性能也有局限性,這個情況下,Altera采用多核化,而Xilinx也從PowerPC“進化”到 ARM 硬核,才逐漸被市場接受。

生態

對于處理器來說,生態才是最重要的,FPGA中的軟核一直不溫不火的另一個原因就是生態。之前所有的廠商都在“自建生態”,導致FPGA平臺更換后就需要針對新的平臺進行系統性的學習和適應,而且目前市場上得主流生態是ARM,想找一個會Nios II或者MicroBlaze的專職人員基本難于登天,所以目前都是FPGA人員兼職開發軟核(這并不是一個好的發展方向)。

還有一個問題,生態不行或者使用的人員少,就意味著沒有成熟的案例可以參考或者學習,更不用說是移植了,同時遇到問題沒有人能夠討論或者協助解決。所以對于軟核的使用大家都會遇到“新手期”長的問題。目前接入一個免費開源未來可能成為主流的ISA架構領域還是很有必要的。

RISC-V架構的特點

除了上面說到得一些特點外,RISC-V還有一個特點就是-凍結式ISA。基本說明被凍結,并且已批準的可選擴展名也被凍結。由于ISA的穩定性,因此可以放心地將軟件開發應用于RISC-V。為RISC-V編寫的軟件可能在所有類似的RISC-V內核上運行。未來有可能你在NISO-V上開發的軟件可以很方便的移植到MicroBlaze-V上。

FPGA的定制性

我們都知道RISC-V指令集采用了結構化的指令集定義方式,這種方式的特點就是非常方便的實現指令的裁剪和擴展。我們都知道FPGA的優勢之一就是可編程性,這就非常適合RISC-V的裁剪和擴展,可以搭建出實現任意指令的軟核。這時候我們可以針對特定的應用(目前FPGA的定制化),定制合適的指令,就可以以最小的邏輯實現低功耗適合我們應用的處理器。比如我們只實現串口或者SPI接口等簡單的應用我們就不需要很復雜的指令,而針對復雜的處理架構就需要多一點的指令。

戰略意義

之前傳出Arm和NVIDIA正在擦除“火花”,Intel和Arm的關系正在從微妙走向詭異。所以Intel對于RISC-V指令集肯定心有所動。網上還流傳出Intel要收購基于RISC-V指令集的處理器IP提供商SiFive的傳聞(后被證明不實),所以這些巨頭的動向會影響整個行業的風向,這意味著想要在行業內不被淘汰,追隨或者超越這些行業巨頭的腳步未嘗不是一個好的選擇。

總結

目前主流FPGA廠商都推出了基于RISC-V的軟核,表明軟核處理器依然有著它獨特的作用和強大的生命力。未來發展可期,未來基于RISC-V的硬核SOC-FPGA也并不遙遠~

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618814 -

RISC-V

+關注

關注

46文章

2583瀏覽量

48887

原文標題:為什么FPGA廠商擁抱RISC-V?不繼續發展RISC

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA與RISC-V淺談

關于RISC-V芯片的應用學習總結

RISC-V MCU技術

《RISC-V能否復制Linux 的成功?》

RISC-V,即將進入應用的爆發期

RISC-V近期市場情況調研

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

RISC-V發展及FPGA廠商為什么選擇RISC-V

RISC-V發展及FPGA廠商為什么選擇RISC-V

評論