產(chǎn)品簡(jiǎn)述

MS5583N 是一款高分辨率模數(shù)轉(zhuǎn)換器,內(nèi)部集

成高階 Σ-Δ 調(diào)制器、低噪聲可編程增益放大器、多

路輸入選擇器和多種內(nèi)部數(shù)字濾波器。其轉(zhuǎn)換速率

從 250SPS 到 4kSPS。此外,芯片內(nèi)部集成失調(diào)校準(zhǔn)

寄存器和增益校準(zhǔn)寄存器。

MS5583N 采用 QFN24 封裝,其額定工作溫度為

-40°C 至+85°C, 最 大 工 作 溫 度 范 圍 為 -40°C 至

+125°C。

主要特點(diǎn)

?SNR:122dB (@250SPS, PGA=1)

?THD:-118dB

?正常工作功耗:21mW (PGA=1,2,4,8)

?掉電模式功耗:10μW

?低噪聲 PGA:5 nV/ Hz

?集成雙通道多路輸入選擇器

?可配置數(shù)字濾波器

?數(shù)據(jù)轉(zhuǎn)換速率:250SPS 至 4kSPS

?失調(diào)和增益校準(zhǔn)

?同步 SYNC 輸入控制

?數(shù)字電源電壓:1.8V 至 3.3V

?最大工作溫度范圍:-40°C 至 125°C

應(yīng)用

?能量檢測(cè)

?地震波檢測(cè)

產(chǎn)品規(guī)格分類(lèi)

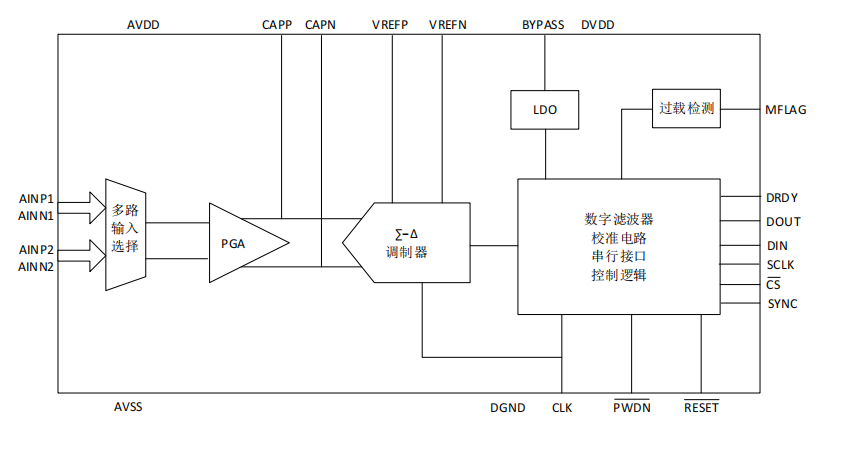

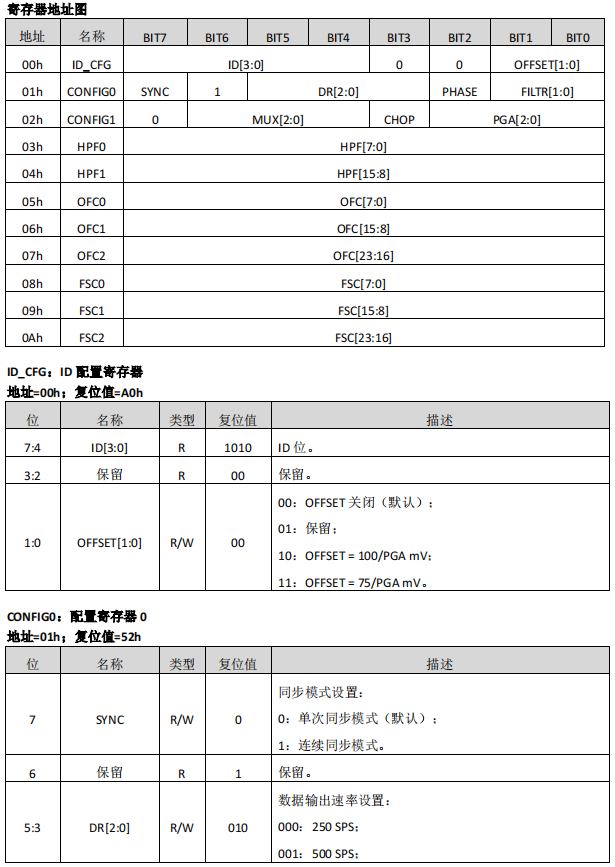

內(nèi)部框圖

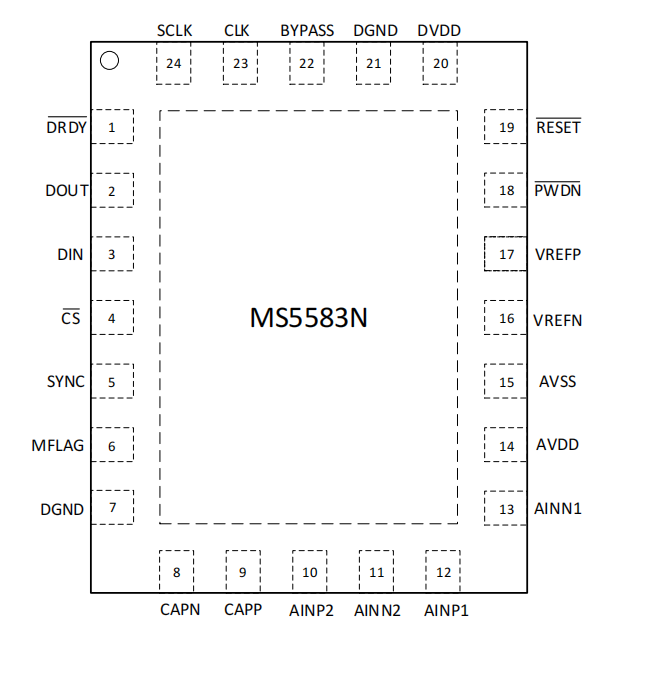

管腳圖

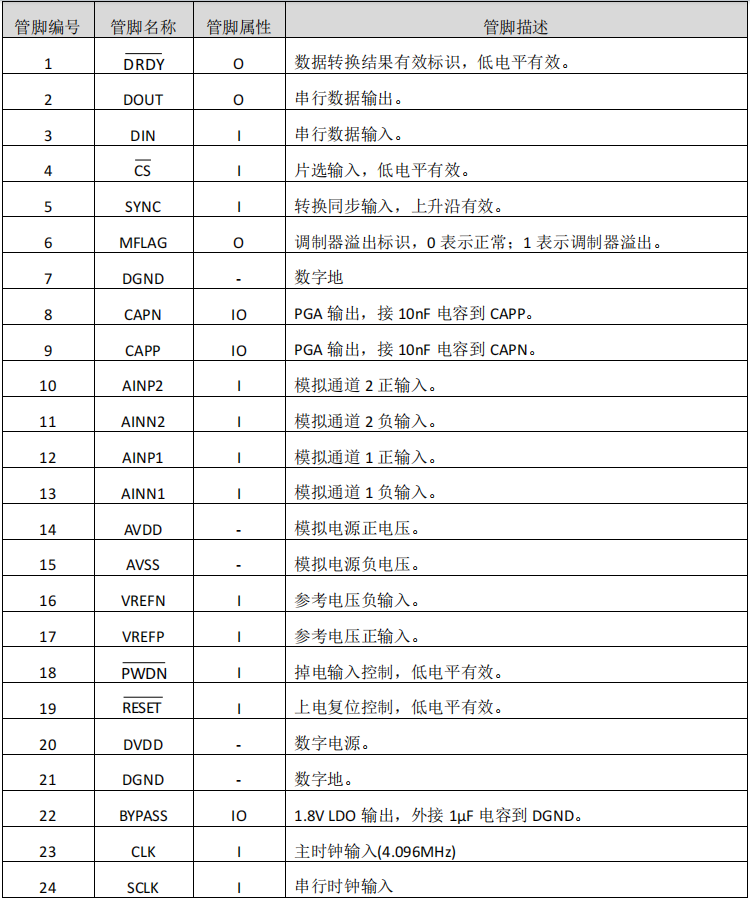

管腳說(shuō)明

如有需求請(qǐng)聯(lián)系——三亞微科技 王子文(16620966594)

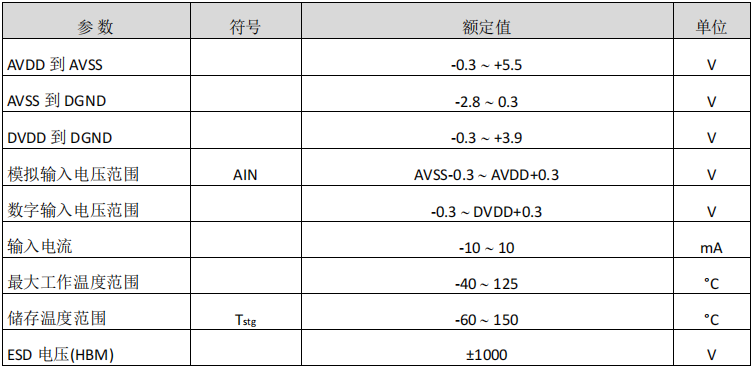

極限參數(shù)

芯片使用中,任何超過(guò)極限參數(shù)的應(yīng)用方式會(huì)對(duì)器件造成永久的損壞,芯片長(zhǎng)時(shí)間處于極限工作

狀態(tài)可能會(huì)影響器件的可靠性。極限參數(shù)只是由一系列極端測(cè)試得出,并不代表芯片可以正常工作在

此極限條件下。

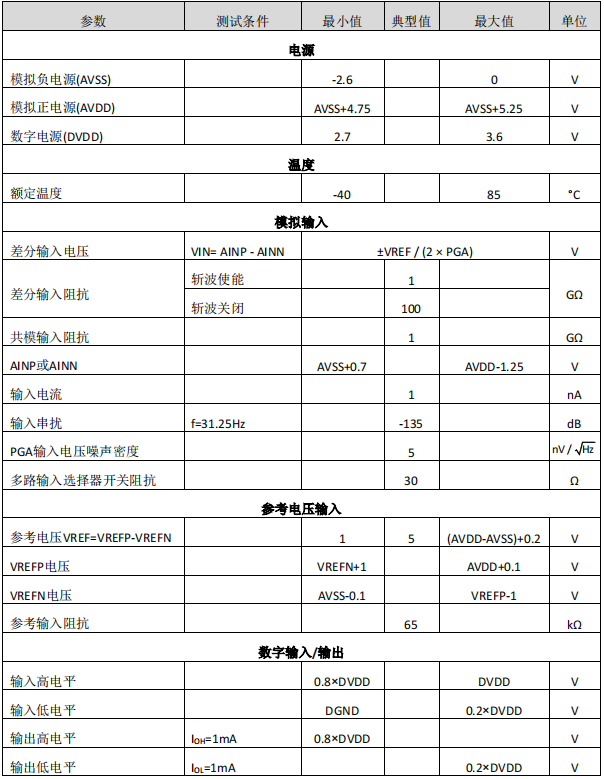

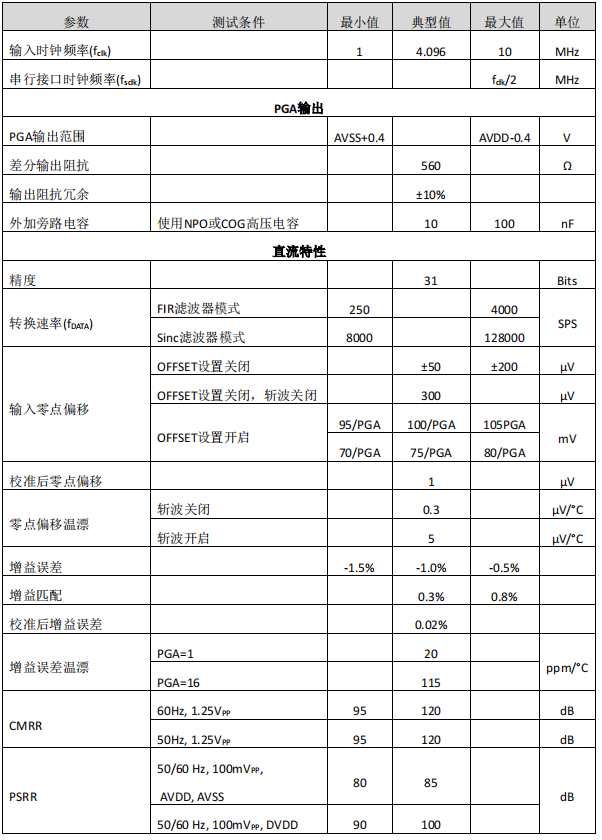

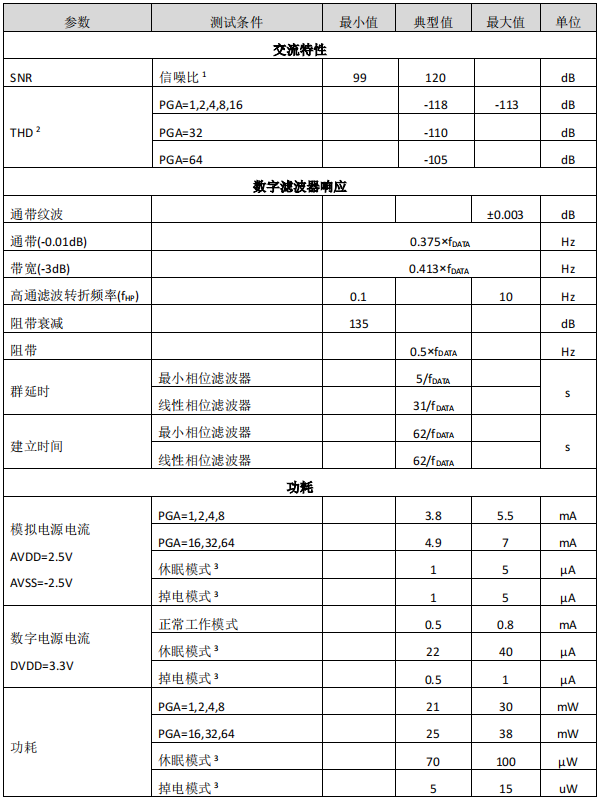

電氣參數(shù)

額 定 溫 度-40°C到 +85°C; 典 型 溫 度25°C,AVDD=2.5V,AVSS=-2.5V;DVDD=3.3V,VREFP=2.5V,

VREFN=-2.5V,PGA=1,fclk=4.096MHz,OFFSET bit=1(使能),CHOP bit=1(使能)和fDATA=

1000SPS(除非另外標(biāo)注)。

如有需求請(qǐng)聯(lián)系——三亞微科技 王子文(16620966594)

注:1. 設(shè)置為內(nèi)部 400Ω 短路,參考“模擬輸入通道”說(shuō)明。

2. 輸入信號(hào)=31.25Hz,-0.5dBFS。

3. 關(guān)閉時(shí)鐘 CLK 輸入。

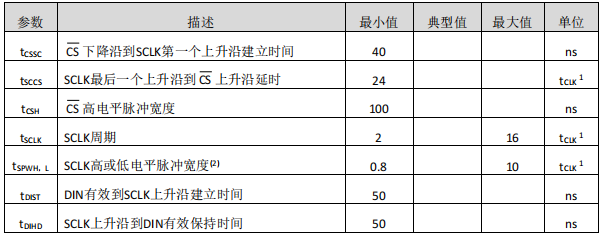

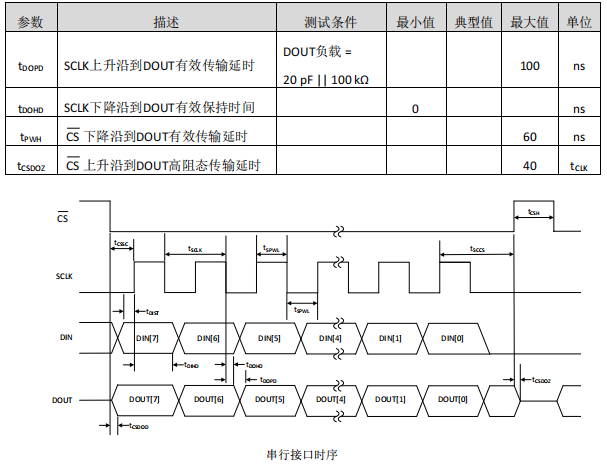

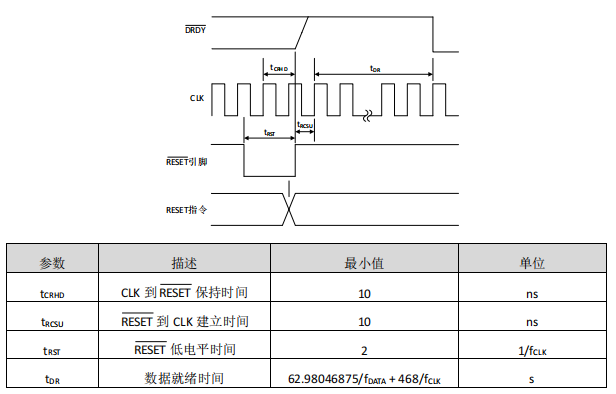

時(shí)序參數(shù)

DVDD=1.65V 到 3.6V,DGND=0V。除非另外標(biāo)注,參數(shù)為全溫度范圍。

注:1. 系統(tǒng)時(shí)鐘 tCLK= 1 / fCLK,默認(rèn)時(shí)鐘頻率 fCLK= 4.096 MHz。

2. 保持 SCLK 為低電平,并經(jīng)過(guò) 64 個(gè) DRDY 下降沿后重置串行接口。

開(kāi)關(guān)參數(shù)

除非另外標(biāo)注,參數(shù)為全溫度范圍。

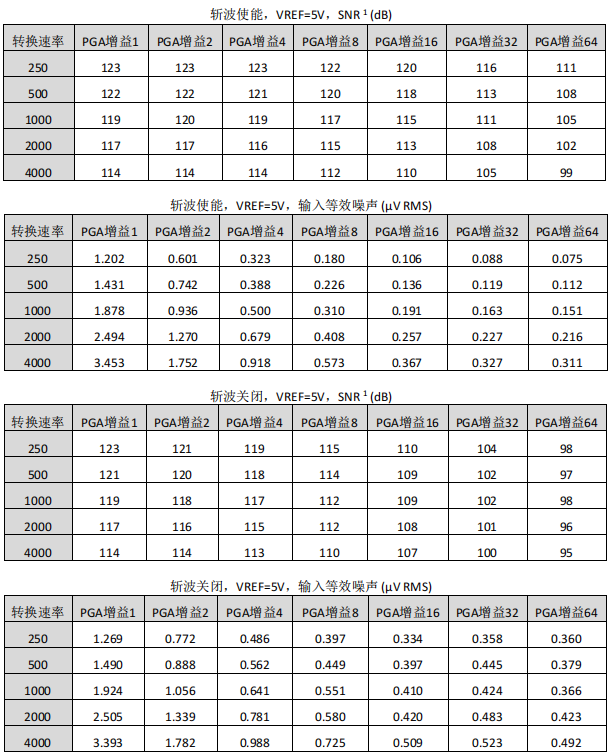

輸入等效噪聲和信噪比

下表給出一些轉(zhuǎn)換速率和 PGA 增益設(shè)置下的 MS5583N 的信噪比和輸入等效均方根噪聲。

注 1: 在典型溫度 25°C 和 VREF=5V。ADC 噪聲積分的帶寬為 0.1Hz 至 0.413X 轉(zhuǎn)換速率。

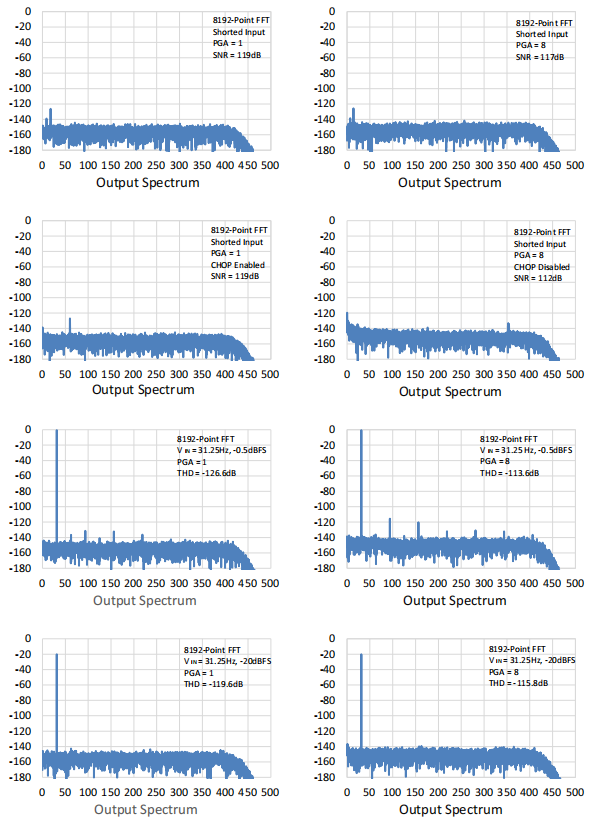

典型圖表

功能描述

概述

MS5583N 是一款高分辨率、低功耗的模數(shù)轉(zhuǎn)換器,可廣泛應(yīng)用于能量檢測(cè)、地震波檢測(cè)等環(huán)

境。在 250SPS 到 4kSPS 轉(zhuǎn)換速率下,可提供 31bit 轉(zhuǎn)換精度。器件集成低噪聲、高輸入阻抗可變

增益放大器、輸入多路選擇器∑-Δ 調(diào)制器、數(shù)字濾波器和 SPI 接口。

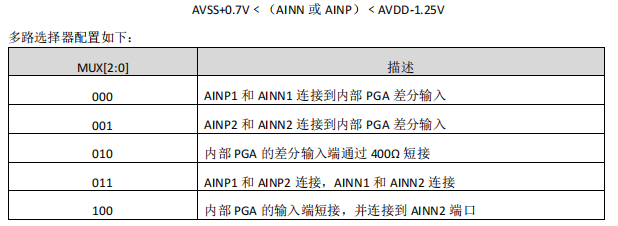

模擬輸入通道

模數(shù)轉(zhuǎn)換器的兩路輸入選擇器輸出到內(nèi)部 PGA 的輸入,通過(guò)寄存器 MUX[2:0]可以設(shè)計(jì)輸入選擇。

由于內(nèi)部 PGA 的輸入范圍受限,所以外部模擬輸入的輸入范圍如下:

模擬輸入 PGA

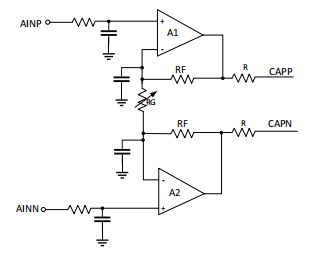

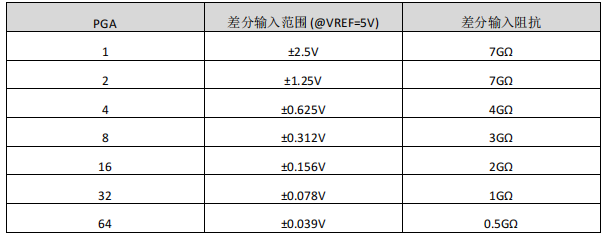

MS5583N 內(nèi)部集成一個(gè)低漂移、低噪聲、高輸入阻抗的可編程放大器。通過(guò)寄存器 PGA[2:0],增

益可設(shè)置成 1、2、4、8、16、32 或 64 倍。

可以通過(guò)設(shè)置打開(kāi)或關(guān)閉斬波,當(dāng)斬波開(kāi)啟時(shí),可以去除放大器的失調(diào)、失調(diào)漂移和 1/f 噪聲,

PGA 輸出到 CAPP 和 CAPN 端口,并連接到調(diào)制器的輸入。必須連接一個(gè) 10nF 電容(或更大)到 CAPP

和 CAPN 端口,PGA 的內(nèi)部示意圖如下:

PGA 的輸入阻抗和輸入范圍隨著增益設(shè)置的變化而變化,具體如下:

時(shí)鐘源

MS5583N 采用外部時(shí)鐘。

調(diào)制器

MS5583N 內(nèi)部集成 4 階 Σ-Δ 調(diào)制器。當(dāng)輸入幅度過(guò)大,MFLAG 端口會(huì)輸出高電平,表示調(diào)制器已

處于輸入過(guò)驅(qū)狀態(tài),最小 MFLAG 信號(hào)持續(xù)時(shí)間為 fclk/8。

調(diào)制器通過(guò)開(kāi)關(guān)電容采樣 PGA 的輸出電壓,會(huì)導(dǎo)致一個(gè)平均輸入電流和等效輸入阻抗。在 CLK 時(shí)

鐘為 4.096MHz 時(shí),調(diào)制器等效輸入阻抗約為 55kΩ。

偏移

MS5583N 可以通過(guò)內(nèi)部寄存器 OFFSET1 和 OFFSET0,設(shè)置調(diào)制器的偏移電壓為 100mV/PGA 或

75mV/PGA。

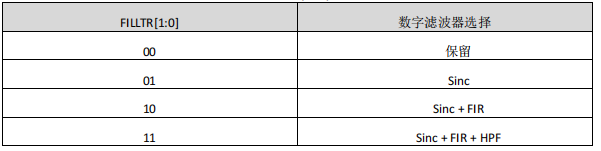

數(shù)字濾波器

可通過(guò)調(diào)整數(shù)字濾波器,權(quán)衡分辨率和轉(zhuǎn)換速率。數(shù)字濾波器由三個(gè)級(jí)聯(lián)濾波器組成:5 階

Sinc 濾波器,F(xiàn)IR 低通濾波器以及一階高通濾波器(HPF)。下表顯示濾波器選項(xiàng)。

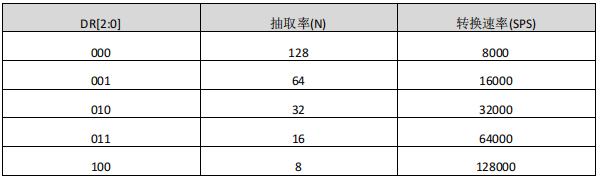

通過(guò)寄存器 DR[2:0]位,設(shè)置 Sinc 濾波器的抽取率,從而影響 ADC 數(shù)據(jù)轉(zhuǎn)換速率,如下表顯示。

FIR 低通濾波器可選線(xiàn)性相位和最小相位兩種相位響應(yīng)模式。在線(xiàn)性相位模式下,濾波器對(duì)不同頻

率輸入信號(hào)的延遲時(shí)間是恒定的,但是延遲和穩(wěn)定時(shí)間較大。在最小相位模式下,延遲時(shí)間較小,但

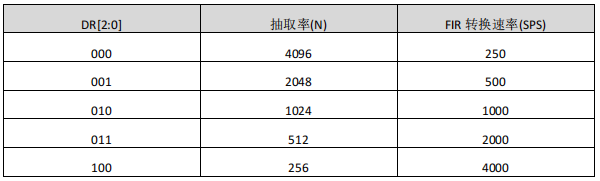

在不同頻率下的延遲時(shí)間不恒定。下表列出 FIR 低通濾波器的抽取率與轉(zhuǎn)換速率的關(guān)系。

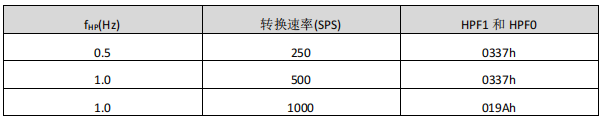

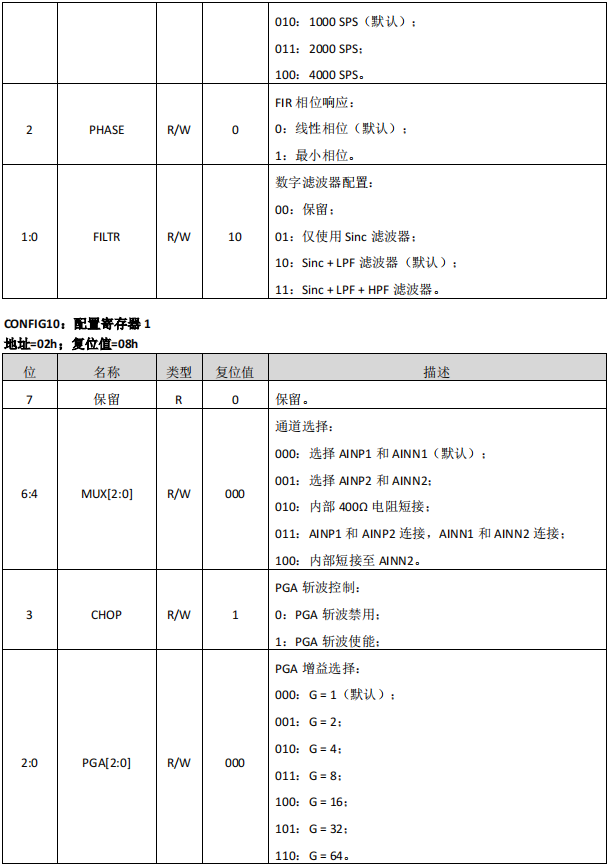

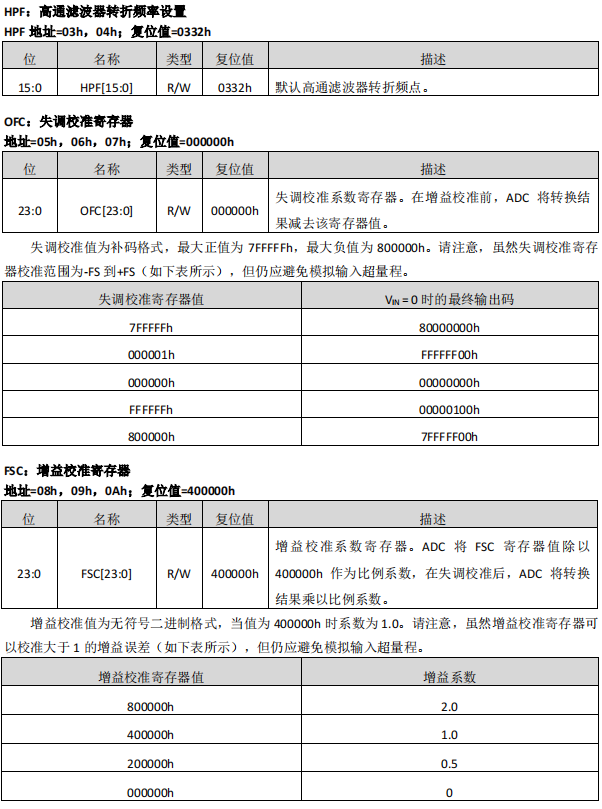

高通濾波器轉(zhuǎn)折頻點(diǎn)由寄存器 HPF1 和 HPF0 以十六進(jìn)制編程。

下表列出示例值。

主時(shí)鐘輸入 CLK

MS5583N 外部主時(shí)鐘典型輸入為 4.096MHz,ADC 的轉(zhuǎn)換速率隨著主時(shí)鐘變化。

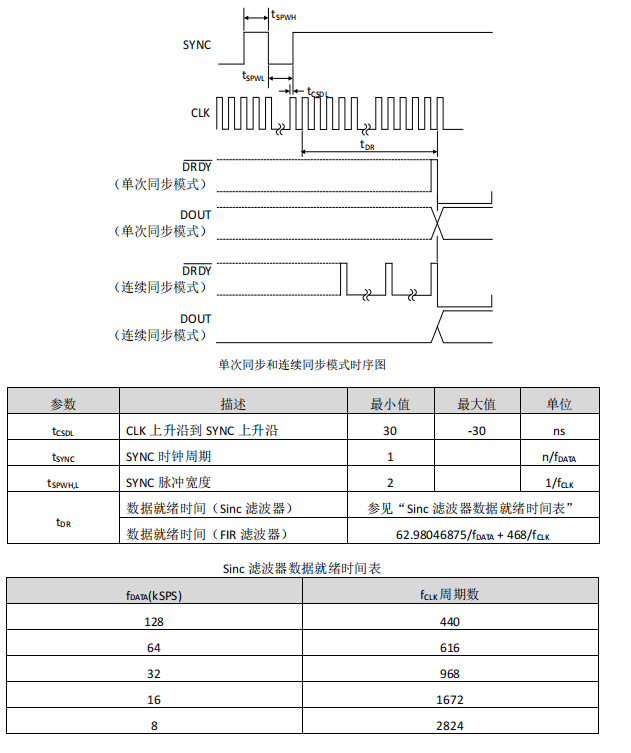

同步轉(zhuǎn)換

MS5583N 可通過(guò)兩種方式同步:SYNC 引腳和 SYNC 指令。芯片具有單次同步和連續(xù)同步兩種模式。

在單次同步模式中,單個(gè)同步信號(hào)同步一次。在連續(xù)同步模式中,既可以通過(guò)單個(gè)同步信號(hào)進(jìn)行同步,

也可以通過(guò)連續(xù)時(shí)鐘輸入 SYNC 引腳來(lái)同步轉(zhuǎn)換,其頻率為轉(zhuǎn)換速率的整數(shù)倍。

單次同步模式

在單次同步模式中,當(dāng)同步信號(hào)產(chǎn)生時(shí),MS5583N 將停止并重啟轉(zhuǎn)換。新的轉(zhuǎn)換數(shù)據(jù)就緒時(shí)間如

下圖表所示:

連續(xù)同步模式

在連續(xù)同步模式中,可以使用單脈沖同步信號(hào)或連續(xù)時(shí)鐘。當(dāng)使用單脈沖同步信號(hào)時(shí),芯片會(huì)像

單次同步模式一樣重新同步。在連續(xù)同步模式下, DRDY 不受影響正常工作,DOUT 一直保持低電平,

直到 63 個(gè) DRDY 周期后數(shù)據(jù)就緒。

輸入 SYNC 引腳的連續(xù)時(shí)鐘,其頻率必須是轉(zhuǎn)換速率的整數(shù)倍,否則芯片將重新同步。芯片將在

SYNC 第一個(gè)上升沿開(kāi)始同步,在此期間,對(duì) ADC 寄存器進(jìn)行任何寫(xiě)操作會(huì)使芯片重新同步。重新同

步將使 SYNC 引腳上的同步控制失效。可通過(guò)在一個(gè)轉(zhuǎn)換周期內(nèi),先后發(fā)送 STANDBY 和 WAKEUP 指令

來(lái)重新使能 SYNC 引腳的同步控制。

復(fù)位

MS5583N 可通過(guò)兩種方式復(fù)位:將 RESET 引腳置低或發(fā)送 RESET 指令。將 RESET 引腳置低并保持

至少 2 個(gè)系統(tǒng)時(shí)鐘周期可強(qiáng)制復(fù)位,在 RESET 置高前,芯片保持在復(fù)位狀態(tài)。發(fā)送 RESET 指令后,芯

片將在第一個(gè)系統(tǒng)時(shí)鐘的上升沿開(kāi)始復(fù)位。

MS5583N 復(fù)位后,寄存器回到默認(rèn)狀態(tài),并且芯片在系統(tǒng)時(shí)鐘下個(gè)上升沿開(kāi)始同步轉(zhuǎn)換。具體時(shí)

序參見(jiàn)下列圖表。

掉電

MS5583N 可通過(guò)將 PWDN 引腳置低且關(guān)閉 CLK 輸入,進(jìn)入掉電模式。當(dāng) PWDN 引腳置低時(shí),芯片

回到默認(rèn)狀態(tài),并禁用內(nèi)部電路以最小化功耗。

在掉電模式中,芯片數(shù)字輸入端口不允許懸空,同時(shí)輸出仍然有效。

休眠

發(fā)送 STANDBY 指令且 CS 置低,發(fā)送 STANDBY 指令后,SPI 接口和寄存器仍保持活動(dòng)狀態(tài)。在 CS

置高后,芯片退出休眠模式。

上電

MS5583N 上電過(guò)程中,內(nèi)部上電復(fù)位電路產(chǎn)生一個(gè)復(fù)位脈沖,可復(fù)位全部數(shù)字電路,復(fù)位時(shí)間為

2 16 個(gè)系統(tǒng)時(shí)鐘周期。

數(shù)字接口

芯片提供兼容 SPI 的串行通信接口和數(shù)據(jù)就緒信號(hào)。

CS

CS 引腳用于激活 SPI 通信。 CS 必須在數(shù)據(jù)傳輸之前和 SPI 通信期間置低。當(dāng) CS 為高時(shí),DOUT 引

腳進(jìn)入高阻態(tài),串行接口將被重置,并忽略此時(shí)的讀取和寫(xiě)入。

將 CS 置高時(shí),數(shù)據(jù)轉(zhuǎn)換及數(shù)據(jù)就緒功能仍能繼續(xù)工作。

SCLK

SCLK 用作串行通信的時(shí)鐘。在 SCLK 上升沿從 DIN 輸入數(shù)據(jù),在 SCLK 下降沿從 DOUT 輸出數(shù)據(jù)。

DIN

在 SCLK 上升沿從 DIN 輸入數(shù)據(jù),即使在數(shù)據(jù)被讀出時(shí),芯片也會(huì)識(shí)別寫(xiě)入的指令。因此,在讀取

數(shù)據(jù)過(guò)程中,DIN 需要保持低電平。

DOUT

在 SCLK 下降沿從 DOUT 輸出數(shù)據(jù)。

SPI 復(fù)位

可通過(guò)將 CS 引腳拉高來(lái)復(fù)位串行接口。若 SPI 空閑時(shí)間超過(guò) 64 個(gè)轉(zhuǎn)換周期,芯片將會(huì)自動(dòng)重置

接口。

DRDY

DRDY 引腳變低電平表示一次新的轉(zhuǎn)換完成。在連續(xù)讀取數(shù)據(jù)模式下,在 DRDY 下一次變低的 4 個(gè)

CLK 周期前完成讀取,否則新的轉(zhuǎn)換數(shù)據(jù)將會(huì)覆蓋之前的數(shù)據(jù)。 DRDY 引腳變低電平后,在 SCLK 的第

一個(gè)下降沿被強(qiáng)制置高。即使 CS 為高時(shí), DRDY 仍可指示新的轉(zhuǎn)換已完成。

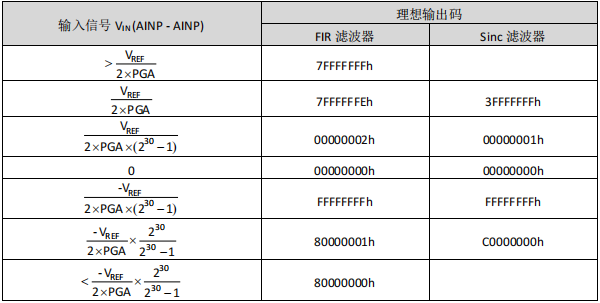

數(shù)據(jù)結(jié)構(gòu)

芯片輸出數(shù)據(jù)格式為 32 位二進(jìn)制補(bǔ)碼。下表為不同輸入信號(hào)的理想輸出碼。注意在 Sinc 濾波器

模式下,輸出數(shù)據(jù)縮放為 1/2。

單次轉(zhuǎn)換操作

MS5583N 可使用 STANDBY 指令的軟件控制方式來(lái)執(zhí)行單次轉(zhuǎn)換操作,以便大大降低功耗。首先,

發(fā)送 STANDBY 指令,使芯片進(jìn)入休眠模式。然后,當(dāng)需要轉(zhuǎn)換時(shí)再發(fā)送 WAKEUP 指令,并等 DRDY 變

低,便可直接讀取轉(zhuǎn)換數(shù)據(jù)。最后,再發(fā)送 STANDBY 指令。每當(dāng)需要轉(zhuǎn)換時(shí),即可重復(fù)上述操作。

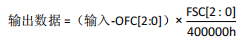

失調(diào)和增益校準(zhǔn)寄存器

在產(chǎn)生最終輸出碼之前,可以對(duì)轉(zhuǎn)換數(shù)據(jù)進(jìn)行失調(diào)和增益校準(zhǔn)。計(jì)算公式如下:

失調(diào)和增益校準(zhǔn)寄存器的值既可以直接寫(xiě)入,也可以通過(guò)校準(zhǔn)指令自動(dòng)設(shè)置。不同的 PGA 設(shè)置對(duì)

應(yīng)特定的失調(diào)和增益校準(zhǔn)。因此 PGA 改變時(shí),這些準(zhǔn)寄存器需要重新校準(zhǔn)。

失調(diào)校準(zhǔn)指令

失調(diào)校準(zhǔn)可以通過(guò)發(fā)送 OFSCAL 命令來(lái)觸發(fā)。在發(fā)送指令前,需要將零輸入信號(hào)施加于芯片。該

指令執(zhí)行后,芯片會(huì)將 16 個(gè)轉(zhuǎn)換數(shù)據(jù)平均后的值寫(xiě)入 OFC 寄存器。

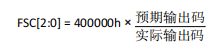

增益校準(zhǔn)指令

增益校準(zhǔn)可以通過(guò)發(fā)送 GANCAL 命令來(lái)觸發(fā)。在發(fā)送指令前,需要將滿(mǎn)幅輸入信號(hào)施加于芯片。

該指令執(zhí)行后,芯片會(huì)將 16 個(gè)轉(zhuǎn)換數(shù)據(jù)平均后的值寫(xiě)入 FSC 寄存器。

用戶(hù)校準(zhǔn)

MS5583N 可外部計(jì)算校準(zhǔn)值并寫(xiě)入校準(zhǔn)寄存器中。步驟如下:

1. 設(shè)置 OFSCAL[2:0] = 0h,GANCAL[2:0] = 400000h。

2. 將零輸入信號(hào)施加于芯片,待系統(tǒng)穩(wěn)定后,將讀取數(shù)據(jù)求平均,數(shù)據(jù)量越大越準(zhǔn)確,然后將平均值

寫(xiě)入 OFC 寄存器。

3. 將滿(mǎn)幅輸入信號(hào)施加于芯片,待系統(tǒng)穩(wěn)定后,將讀取數(shù)據(jù)求平均,數(shù)據(jù)量越大越準(zhǔn)確,而后將平均

值寫(xiě)入 FSC 寄存器。

增益校準(zhǔn)值公式如下:

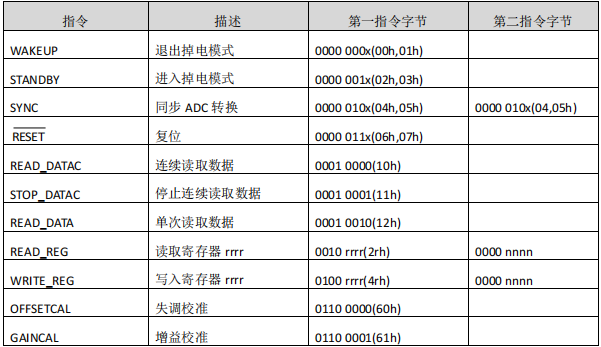

指令

可通過(guò) 13 個(gè)指令來(lái)控制芯片。其中對(duì)于芯片寄存器數(shù)據(jù)的讀寫(xiě)指令(READ_REG 和 WRITE_REG),

需要額外的字節(jié)作為指令的一部分。發(fā)送指令期間, CS 必須保持低電平,兩個(gè)指令字節(jié)之間必須間隔

24 個(gè)系統(tǒng)時(shí)鐘周期。

1. n = 讀寫(xiě)寄存器數(shù) - 1;

2. r = 寄存器地址;

3. x = 任意值;

WAKEUP(0000 000x)

在執(zhí)行 STANDBY 指令后,可通過(guò) WAKEUP 指令使芯片上電。正常工作時(shí)該指令無(wú)效,因此在讀取

數(shù)據(jù)時(shí),DIN 可以保持低電平。

STANDBY(0000 001x)

發(fā)送 STANDBY 指令后,芯片進(jìn)入掉電模式。 CS 置高或發(fā)送 WAKEUP 指令后,芯片退出掉電模式。

SYNC(0000 010x)

SYNC 指令會(huì)復(fù)位 ADC 并重啟轉(zhuǎn)換。為了同步多個(gè) ADC,該指令必須同時(shí)發(fā)送至所有芯片。在此

命令期間,SYNC 引腳必須保持高電平。

RESET(0000 011x)

復(fù)位指令可復(fù)位所有寄存器和數(shù)字濾波器。該指令等效于 RESET 引腳。時(shí)序可參考“復(fù)位”章節(jié)。

READ_DATAC(0001 0000)

READ_DATAC 指令可使能連續(xù)讀取數(shù)據(jù)模式(默認(rèn)模式)。在該模式下,可直接從芯片讀出轉(zhuǎn)換

數(shù)據(jù)。當(dāng) DRDY 變低時(shí),代表新數(shù)據(jù)已就緒,隨后 MSB 出現(xiàn)在 DOUT 上,可以在 SCLK 上升沿讀取數(shù)據(jù)。

DRDY 將在 SCLK 第一個(gè)下降沿回到高電平。32 位數(shù)據(jù)讀取完成后,DOUT 將變低。

STOP_DATAC(0001 0001)

發(fā)送 STOP_DATAC 指令可退出連續(xù)讀取數(shù)據(jù)模式,并同時(shí)進(jìn)入單次讀取數(shù)據(jù)模式。在該模式下,

需要通過(guò)發(fā)送 RDATA 指令來(lái)讀取轉(zhuǎn)換數(shù)據(jù)。發(fā)送該指令后,需等 DRDY 變?yōu)榈碗娖剑拍茉?SCLK 上升

沿讀取有效數(shù)據(jù)。

READ_DATA(0001 0010)

READ_DATA 指令可讀取最近一次的轉(zhuǎn)換結(jié)果至輸出寄存器。可將 CS 置高來(lái)退出單次讀取數(shù)據(jù)模

式。

READ_REG(0010 rrrr, 0000 nnnn)

通過(guò) READ_REG 指令,可讀取寄存器的數(shù)據(jù)。讀取的寄存器的數(shù)量等于指令第二字節(jié)數(shù)+1。

READ_REG 指令的兩字節(jié)結(jié)構(gòu)如下:

1. 第一指令字節(jié):2rh,其中 r 是第一個(gè)讀取的寄存器地址;

2. 第二指令字節(jié):0nh,其中 n = 待讀取寄存器數(shù)-1。

WRITE_REG(0100 rrrr, 0000 nnnn)

通過(guò) WRITE_REG 指令,可對(duì)寄存器寫(xiě)入數(shù)據(jù)。寫(xiě)入的寄存器的數(shù)量等于指令第二字節(jié)數(shù)+1。

WRITE_REG 指令兩字節(jié)結(jié)構(gòu)如下:

1.第一指令字節(jié):2rh,其中 r 是第一個(gè)寫(xiě)入的寄存器地址;

2.第二指令字節(jié):0nh,其中 n = 待寫(xiě)入寄存器數(shù)-1。

OFFSETCAL(0110 0000)

OFFSETCAL 指令啟動(dòng)失調(diào)校準(zhǔn)。當(dāng)失調(diào)校準(zhǔn)時(shí),模擬輸入必須接至零電平。當(dāng)該指令完成后,OFC

寄存器會(huì)自動(dòng)更新。

GAINCAL(0110 0001)

GAINCAL 指令啟動(dòng)增益校準(zhǔn)。當(dāng)增益校準(zhǔn)時(shí),模擬輸入必須設(shè)置為滿(mǎn)幅。當(dāng)該指令完成后,F(xiàn)SC

寄存器會(huì)自動(dòng)更新。

如有需求請(qǐng)聯(lián)系——三亞微科技 王子文(16620966594)

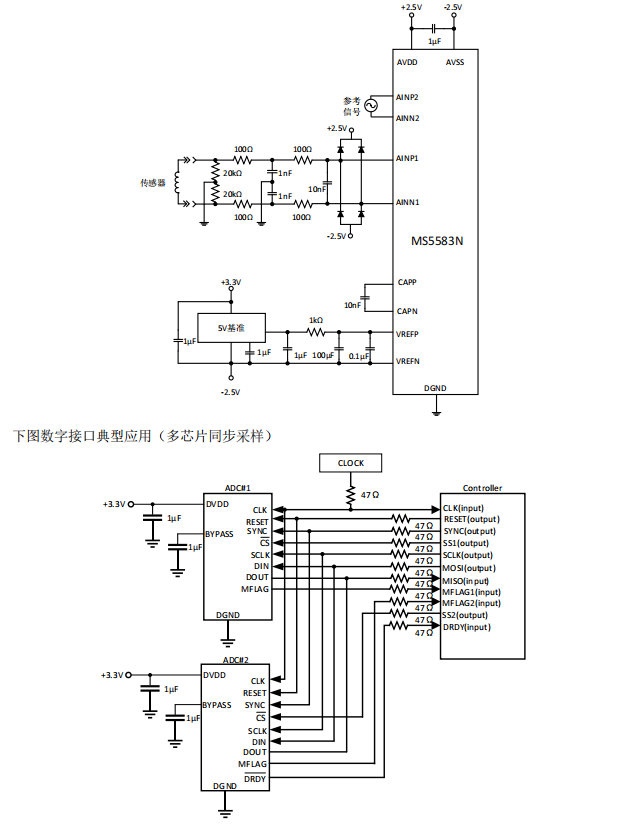

典型應(yīng)用圖

下圖是 MS5583N 用作地震檢波器應(yīng)用的示意圖。

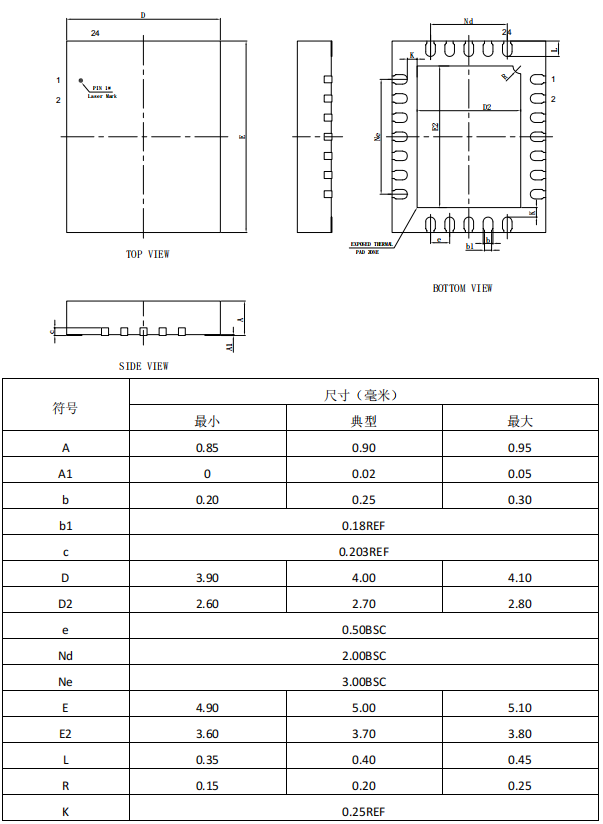

封裝外形圖

QFN24

——愛(ài)研究芯片的小王

審核編輯 黃宇

-

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3311瀏覽量

128055

發(fā)布評(píng)論請(qǐng)先 登錄

LT8722如何實(shí)現(xiàn)高分辨率的脈沖?

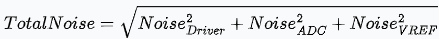

探討電壓基準(zhǔn)噪聲對(duì)模數(shù)轉(zhuǎn)換器(ADC)的有效位數(shù)(ENOB)和無(wú)噪聲分辨率的影響

MS1112——16-bit 多輸入內(nèi)置基準(zhǔn)模數(shù)轉(zhuǎn)換器

使用DM642 DSP和THS8200驅(qū)動(dòng)器的高分辨率視頻

使用MSP430高分辨率定時(shí)器的PWM DAC

高分辨率音頻和傳統(tǒng)音頻區(qū)別

鼎陽(yáng)科技|高分辨率產(chǎn)品增長(zhǎng)39.42%,引領(lǐng)高端市場(chǎng)新浪潮!

高速、高分辨率光傳感器的價(jià)值

LDC1101 1.8V高分辨率、高速電感數(shù)字轉(zhuǎn)換器數(shù)據(jù)表

什么是高分辨率示波器?它有哪些優(yōu)勢(shì)?

ADS1284高分辨率模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

TLV1562高速可編程分辨率模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

Moritex 5X 高分辨率遠(yuǎn)心鏡頭 助力晶圓檢測(cè)

ADS1283高分辨率模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

MS5583N——高分辨率模數(shù)轉(zhuǎn)換器介紹

MS5583N——高分辨率模數(shù)轉(zhuǎn)換器介紹

評(píng)論