- ALINX NVMeIP -

在當(dāng)下數(shù)據(jù)驅(qū)動的時代,企業(yè)對高性能存儲解決方案的需求不斷增加。NVMe AXI IP 憑借其支持大數(shù)據(jù)量、高速傳輸、低延遲等存儲性能優(yōu)勢,成為眾多開發(fā)者和企業(yè)的理想選擇。

NVMe專為 SSD 而生,通過直接利用 PCIe 通道,避免 SATA 協(xié)議和外置控制器(PCH)的額外延遲,使性能大幅提升,尤其在隨機 I/O 操作中表現(xiàn)突出。

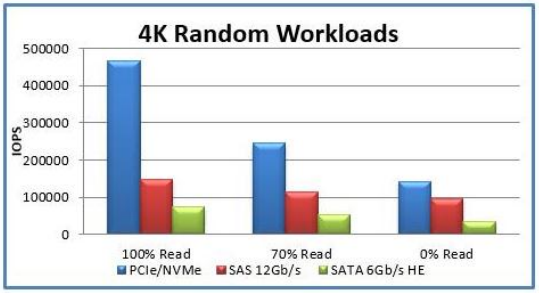

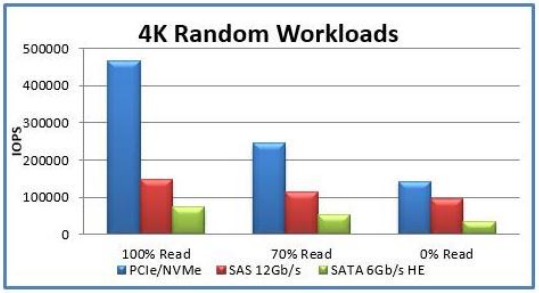

NVMe PCIe SSD的 IOPs 性能可達高端企業(yè)級 SATA SSD 的十倍(具體場景為高隊列深度的隨機讀寫),同時支持自動功耗狀態(tài)切換和動態(tài)能耗管理功能,顯著降低功耗。

( NVMe/SAS/SATA 存儲設(shè)備單讀性能對比)

NVMe 協(xié)議憑借其高速傳輸、低延遲、高效能存儲和高可靠性的特點,在數(shù)據(jù)中心、邊緣計算、企業(yè)存儲、AI 服務(wù)器和云計算等領(lǐng)域有著廣泛應(yīng)用。

ALINX NVMe IP 詳情

ALINX NVMe IP 針對當(dāng)前數(shù)據(jù)密集型應(yīng)用進行了深度優(yōu)化,顯著縮短了延遲時間,提升數(shù)據(jù)吞吐量,滿足云計算、大數(shù)據(jù)分析、人工智能、虛擬現(xiàn)實/增強現(xiàn)實( VR/AR )等前沿領(lǐng)域的迫切需求。

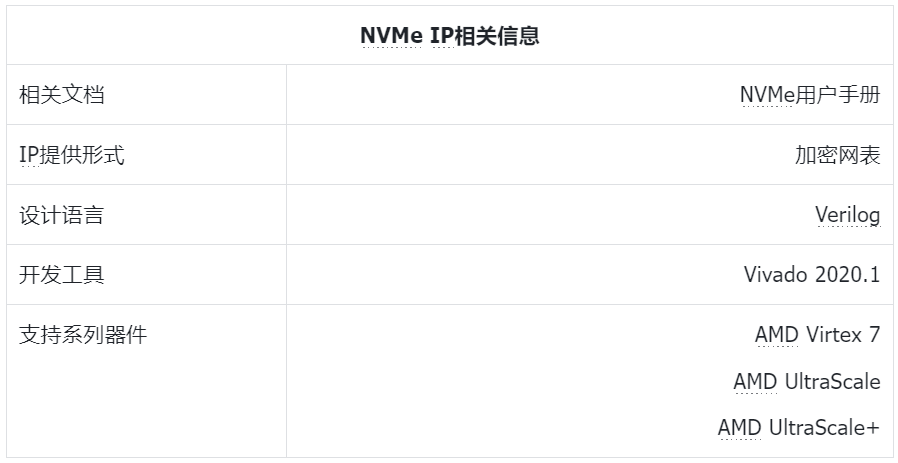

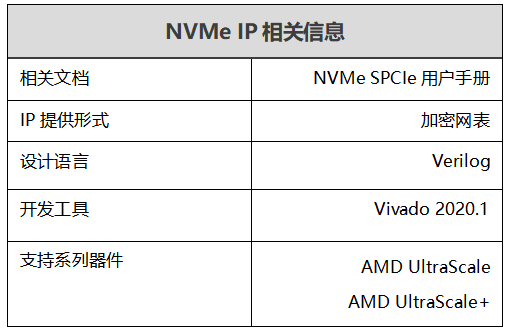

兼容性方面,NVMe IP 不依賴 CPU,全部由 FPGA 完成處理,需要 FPGA 具有足夠的資源和適當(dāng)?shù)挠布С帧LINX NVMe IP 目前支持AMD Virtex 7/ AMD UltraScale/AMD UltraScale+系列器件。

技術(shù)支持方面,ALINX 提供完善的技術(shù)支持和高效的定制化服務(wù),由經(jīng)驗豐富的 IP 研發(fā)團隊專人對接,全程協(xié)助客戶完成 IP 集成和性能優(yōu)化,確保客戶需求快速實現(xiàn)。

考慮到每個應(yīng)用場景都有其獨特需求,ALINX NVMe AXI IP 為開發(fā)者提供了豐富的定制選項,允許根據(jù)特定的應(yīng)用需求對其性能進行精準調(diào)整,包括不限于優(yōu)化特定工作負載下的數(shù)據(jù)傳輸速率,根據(jù)不同的存儲容量需求進行配置等。

以下是 ALINX NVMe IP 的詳細介紹:

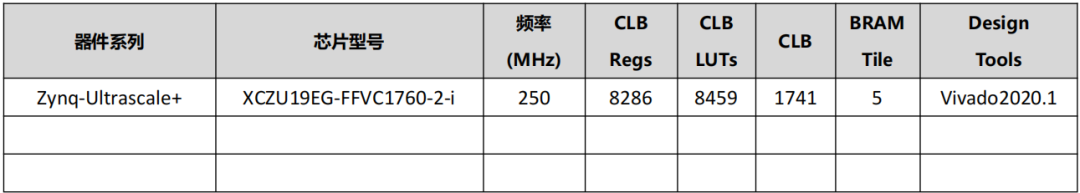

IP 資源消耗表

注:IP 實際邏輯資源消耗受實例化中其他邏輯資源消耗影響

產(chǎn)品特性

功能支持:命令支持(Identify、Write、Read、Flush),兼容 NVMe 1.4 協(xié)議,支持 PCIe Gen 1.0-4.0;

性能參數(shù):

(1)最大隊列深度:每個隊列支持 65535 個 I/O 命令;

(2)傳輸速率:基于 PCIe 3.0 X4,讀寫速率均可達 3000MB/s;

靈活性:支持多種存儲單元(512 字節(jié) / 4096 字節(jié));

支持定制化服務(wù):包括數(shù)據(jù)傳輸速率優(yōu)化和存儲容量配置;

版本支持:支持兩個版本(AXI FULL 版本 / AXI Stream 版本);

參考設(shè)計:XCZU19EG + FMC子板(FH1402)+SAMSUNG 980 M.2 SSD。

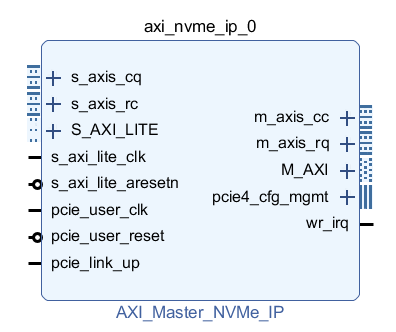

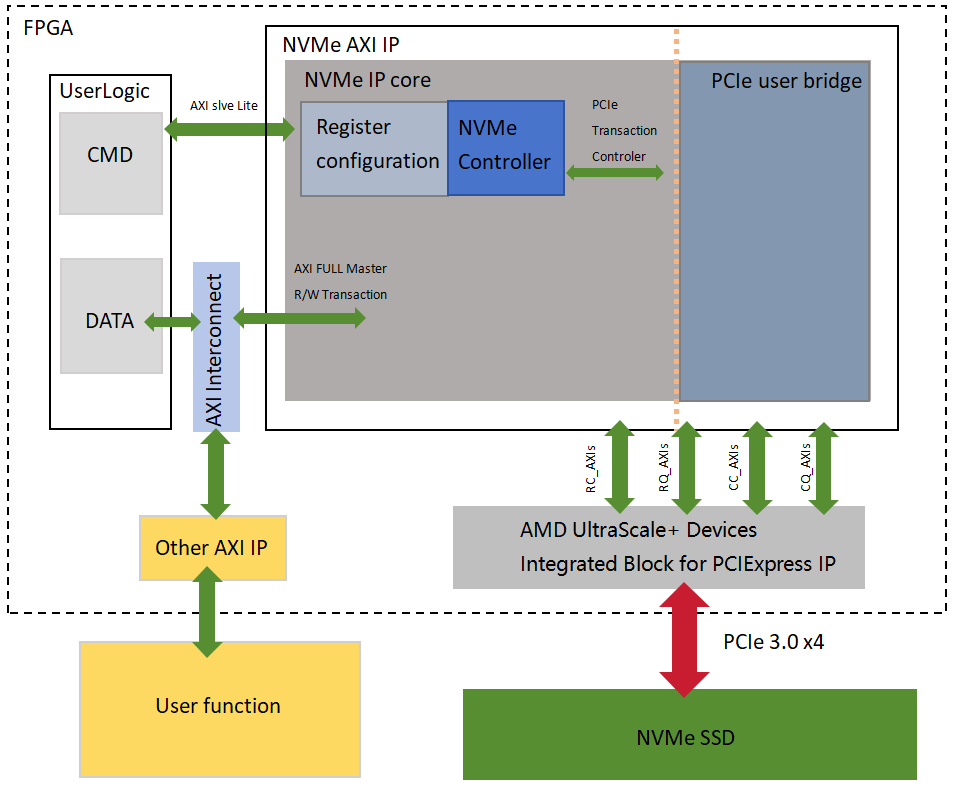

AXI-Master-FULL 版本

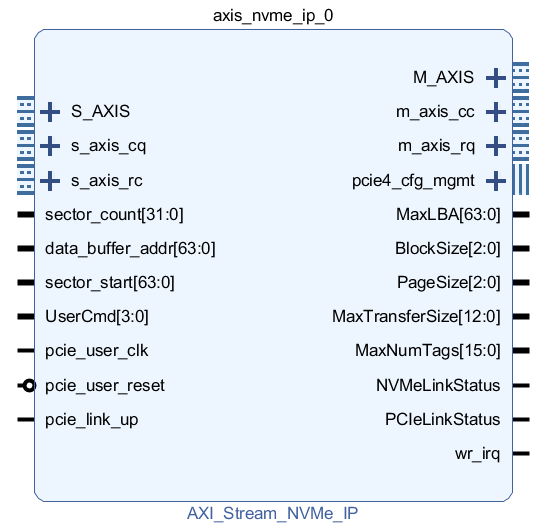

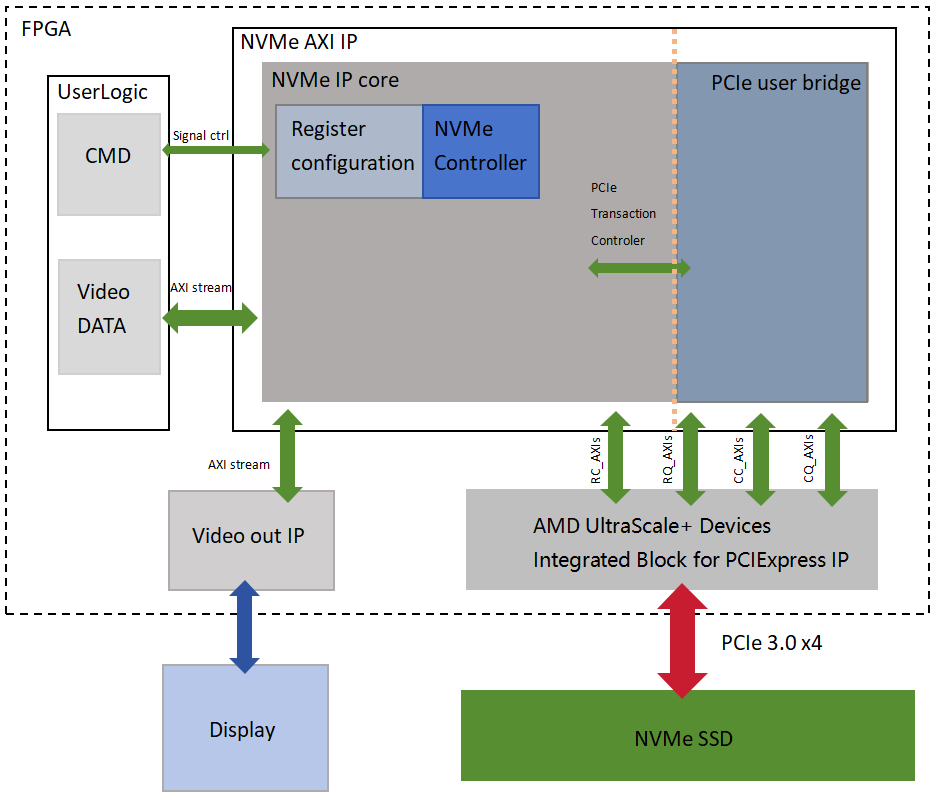

AXI-Stream 版本

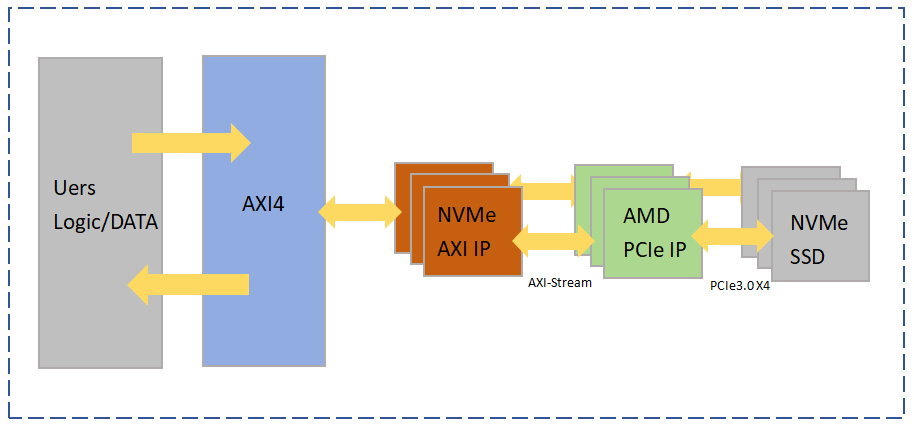

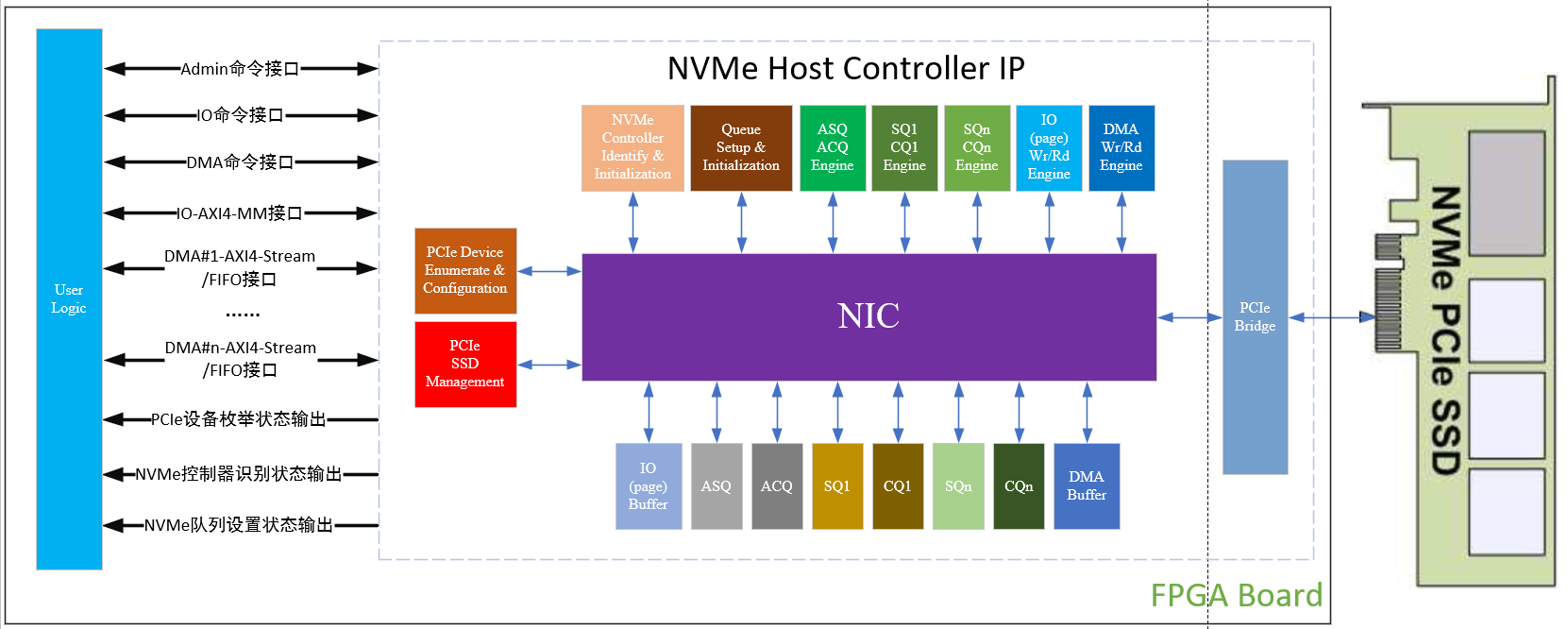

NVMe AXI IP 應(yīng)用交互

NVMe AXI IP 通過 PCIe Bridge 實現(xiàn) PCIe 協(xié)議交互,支持 AXI FULL 和 AXI Stream 兩種接口模式。用戶數(shù)據(jù)通過 AXI Interconnect 接入后,經(jīng)過 NVMe AXI IP 的協(xié)議邏輯處理,被打包為 PCIe TLP 包并寫入 NVMe SSD 存儲;同樣,數(shù)據(jù)從 NVMe SSD 提取后,通過協(xié)議解析和 AXI 接口傳遞到上層邏輯。

Example 舉例

AXI-Master-FULL 版本

AXI 讀寫:在系統(tǒng)正常啟動后,NVMe AXI IP 自動初始化并建立 PCIe 鏈路連接。初始化完成后,用戶的數(shù)據(jù)流通過 AXI Interconnect IP 傳送到 NVMe AXI IP 的 AXI Master FULL 接口,進行 NVMe 協(xié)議的處理。數(shù)據(jù)被打包為 TLP 層 PCIe 包,并通過 RC/RQ/CC/CQ AXI Stream 接口與 AMD UltraScale+ 設(shè)備的 PCIe 集成模塊(Integrated Block for PCIExpress)連接,最終寫入 NVMe SSD 存儲。當(dāng)需要讀取數(shù)據(jù)時,NVMe AXI IP 從 NVMe SSD 通過 RC/RQ/CC/CQ AXI Stream 接口提取數(shù)據(jù),再通過 AXI Master FULL 接口與 AXI Interconnect IP 連接,將數(shù)據(jù)傳輸?shù)狡渌?AXI 總線接口供用戶邏輯使用。

AXI-Stream 版本

AXI Stream 讀寫:在系統(tǒng)正常啟動后,NVMe AXI IP 自動進行初始化并建立連接。初始化完成后,用戶的數(shù)據(jù)流通過 AXI Stream 接口輸入到 NVMe AXI IP,執(zhí)行 NVMe 協(xié)議的交互處理。數(shù)據(jù)被打包為 TLP 層 PCIe 包,通過 RC/RQ/CC/CQ AXI Stream 接口與 AMD UltraScale+ 設(shè)備的 PCIe 集成模塊連接,最終存儲到 NVMe SSD。當(dāng)從 NVMe SSD 讀取數(shù)據(jù)時,NVMe AXI IP 使用 RC/RQ/CC/CQ AXI Stream 接口提取數(shù)據(jù),并通過 AXI Stream 接口傳輸給連接的視頻輸出 IP,進而通過視頻接口進行數(shù)據(jù)展示。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21989瀏覽量

615233 -

控制器

+關(guān)注

關(guān)注

114文章

17022瀏覽量

183276 -

接口

+關(guān)注

關(guān)注

33文章

8967瀏覽量

153347 -

SSD

+關(guān)注

關(guān)注

21文章

2955瀏覽量

119224 -

nvme

+關(guān)注

關(guān)注

0文章

243瀏覽量

23150

原文標題:【新品速遞】一文詳解 ALINX NVMe IP 特性

文章出處:【微信號:ALINX,微信公眾號:ALINX】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA NVMe Host Controller IP,NVMe主機控制器

Xilinx FPGA NVMe主機控制器IP,高性能版本介紹應(yīng)用

Xilinx FPGA高性能NVMe SSD主機控制器,NVMe Host Controller IP

高性能NVMe主機控制器,Xilinx FPGA NVMe Host Accelerator IP

NVMe控制器IP設(shè)計之接口轉(zhuǎn)換

NVMe協(xié)議研究掃盲

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

NVMe Host Controller IP實現(xiàn)高性能存儲解決方案

ALINX VERSAL SOM產(chǎn)品介紹

芯驛電子ALINX推出全新IP核產(chǎn)品線

芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線,覆蓋 TCP/UDP/NVMe AXI IP 核

一文詳解 ALINX NVMe IP 特性

ALINX發(fā)布100G以太網(wǎng)UDP/IP協(xié)議棧IP核

ALINX NVME SPCle IP 特性詳解

淺談ALINX NVMe IP產(chǎn)品特性

淺談ALINX NVMe IP產(chǎn)品特性

評論