電流采樣是FOC中基礎(chǔ)且重要的一個(gè)步驟,只有電流采樣準(zhǔn)確了整個(gè)算法才能獲得好的效果。電流采樣是采集續(xù)流電流,也就是在三個(gè)下管導(dǎo)通的時(shí)候采樣,采集中間時(shí)刻的電流,可以反映平均電流(用電感續(xù)流來理解,在電感續(xù)流的時(shí)候,中間時(shí)刻的電流就可以反應(yīng)平均電流)。電流采樣方式一般分為三電阻、雙電阻、單電阻采樣,其優(yōu)缺點(diǎn)如下圖所示。

1.2.

采樣電阻的位置

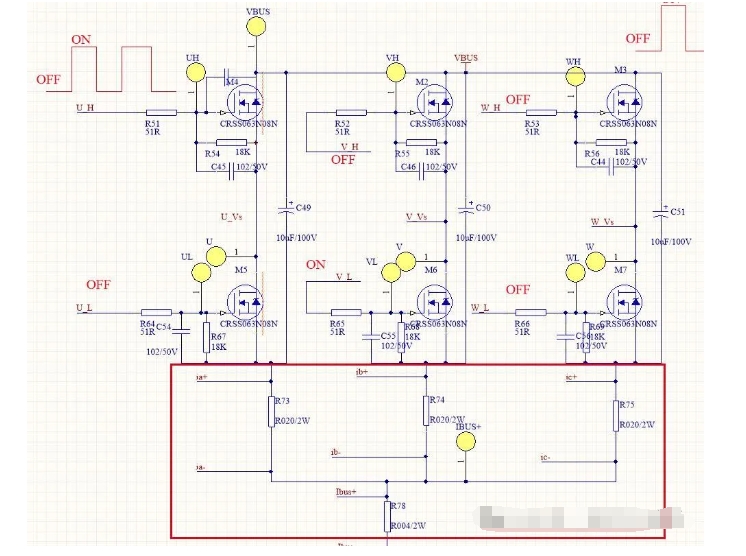

這里使用下采樣電阻,也就是電流采樣電阻放在下端,有兩個(gè)好處:一是共模電壓接近0V,信號處理相對比較容易。二是在一個(gè)PWM周期內(nèi)采樣電阻存在不通電的情況,這樣可以降低采樣電阻的功率。另外,母線上還有一個(gè)母線電阻,這個(gè)電阻有兩個(gè)作用。一是用于單電阻采樣;二是采集母線電流,實(shí)現(xiàn)過流保護(hù)。另外,存在將電阻串在相線上的情況,如下圖所示。此時(shí)相比下電阻采樣,采集的電流就不同了,因?yàn)殡娏魇冀K是連續(xù)的,不存在采樣窗口的問題。為了采集平均電流,可以采集三上橋臂導(dǎo)通的中間時(shí)刻的電流。但是這種方案運(yùn)放的共模電壓也高了,并且由于電流始終流過電阻,所以電阻的功率要比下電阻采樣要高。

1.3.

采樣窗口問題

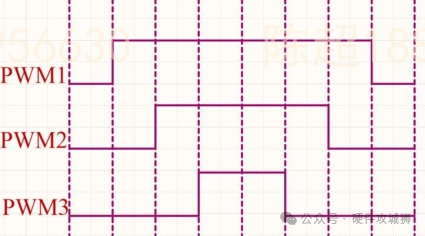

當(dāng)下管的PWM占空比很小的時(shí)候,如下圖所示的PWM3。由于ADC采樣需要保持一定的時(shí)間,所以占空比很小的時(shí)候采集到的數(shù)據(jù)就可能不準(zhǔn)。由KCL可知此時(shí)的三相電流的和為0,此時(shí)如果是三電阻采樣方案,那么可以使用另外兩相占空比大的算出第三相的電流。而如果是雙電阻采樣那么就沒辦法了,只能就這樣使用,或者限制下管的最小占空比,這樣才能保證采樣的電流是準(zhǔn)確的。對于單電阻采樣來說,需要根據(jù)不同的開關(guān)組合得到對應(yīng)的電流,而且需要在一個(gè)PWM周期內(nèi)采樣兩次,依靠算法來重構(gòu)三相電流,所以是最困難的一種方案。

2.運(yùn)放電路

為了降低采樣電阻的功耗,一般采樣電阻的阻值都很小。那么其兩端的壓差也很小,如果直接輸入單片機(jī)的ADC進(jìn)行采集,那么單片機(jī)很難分辨出來。所以為了提高分辨率,需要對電壓進(jìn)行放大。此外,這么小的電壓信號在放大之前也很容易受到干擾,所以對于PCB的布局布線有要求,需要盡量減小干擾。注意:采集到的電流信號不需要進(jìn)行濾波處理,因?yàn)闉V波會造成信號延遲。

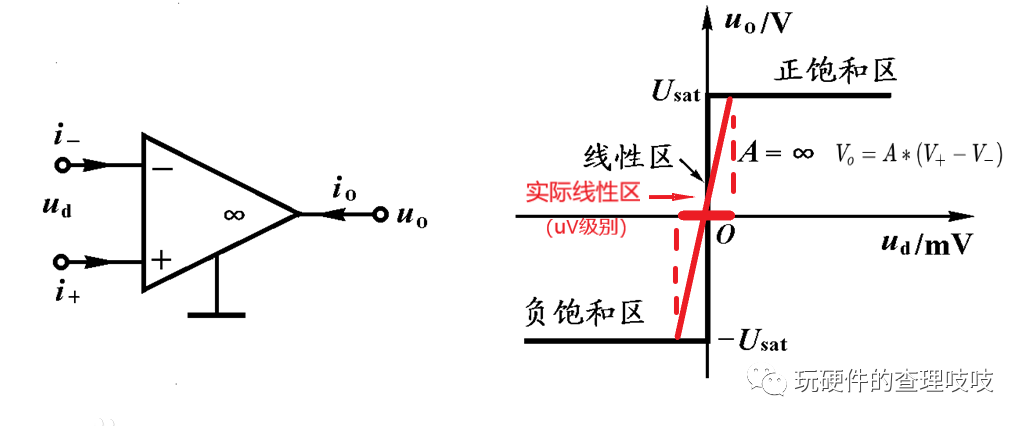

2.1.運(yùn)放和比較器

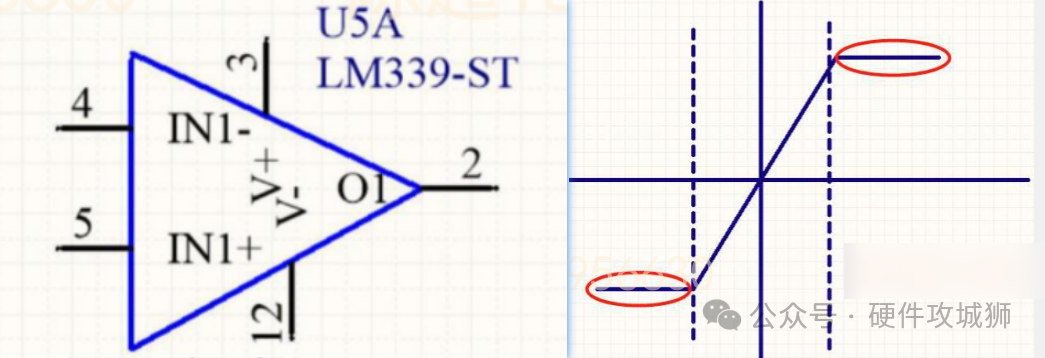

如下圖所示,比較器的兩個(gè)輸入端接兩個(gè)模擬信號,比較器的輸出是一個(gè)數(shù)字信號,即高低電平。但是比較器內(nèi)部是集電極開路或者漏極開路輸出,所以需要在比較器的輸出端接上拉電阻。比較器輸出數(shù)字信號,他的跳邊沿很陡。也就是說比較器的輸出要么飽和,要么截止,而運(yùn)放一般工作在放大區(qū)。所以按照輸出特性曲線來說,比較器工作在下圖的紅圈處(注意下面的紅圈也可以認(rèn)為是負(fù)飽和區(qū),只不過一般運(yùn)放的負(fù)端接GND,那么就是0V,也認(rèn)為是截止)。而運(yùn)放工作在虛線內(nèi)的放大區(qū)。為了讓比較器的輸出沿更陡,一般接一個(gè)正反饋。而運(yùn)放工作在線性區(qū)。為了讓運(yùn)放不飽和,一般會接一個(gè)負(fù)反饋,抑制運(yùn)放的飽和,讓他工作在線性區(qū)。此外,運(yùn)放接入正反饋,也可以當(dāng)做比較器來使用。

2.2.

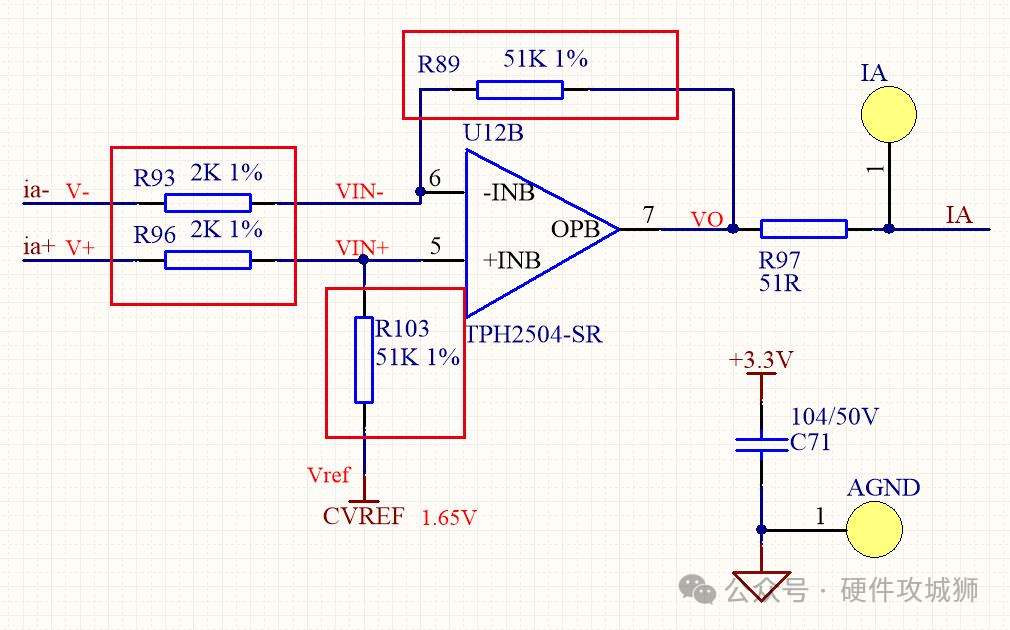

差分放大

所謂差分就是對兩個(gè)信號求差,差分放大就是對兩個(gè)信號的差值進(jìn)行放大。其實(shí)這里根據(jù)采樣電路就決定了使用的就是差分,因?yàn)樾枰?jì)算的是采樣電阻兩端的壓差,也就是電位差,這就是差分。差分放大的好處是可以消除共模干擾,所謂共模就是信號對地來說,共模干擾就是信號相對于地這個(gè)參考點(diǎn)來說的干擾。如下圖所示,如果Ia+和Ia-都存在對地的干擾,那么信號作差之后共模干擾就會減小,這樣運(yùn)放輸出的信號就更加準(zhǔn)確。

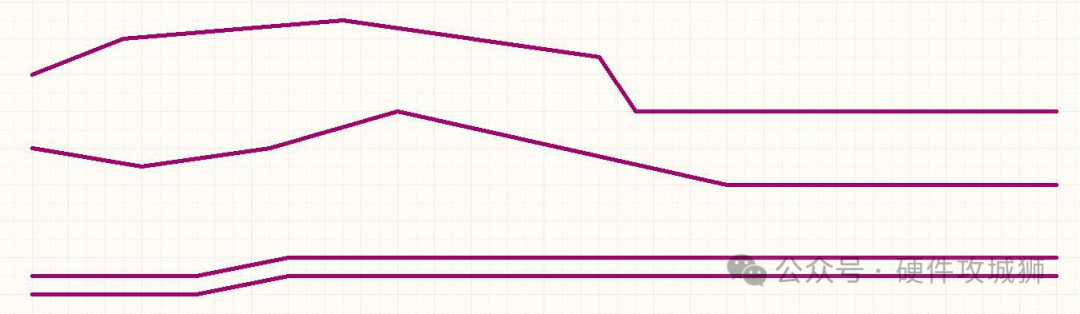

差分接法雖然可以減小共模干擾的影響,但是也存在差模干擾。所謂差模干擾,就是兩根信號線之間的干擾。這是因?yàn)閮蓚€(gè)信號線之間的環(huán)路有磁場的變化,這樣就會引入干擾。所以差模干擾跟信號走線也有關(guān)系,如果兩根信號線之間的環(huán)路比較大的話,空間就會大,這樣磁場變化引起的干擾也就會越大。因此差分接法走線的時(shí)候也盡量要走差分線,這樣可以把環(huán)路空間減小,起到抑制差模干擾的作用。如下圖所示,上面的走線圍城的面積空間大,環(huán)路大,這樣信號線上有電流流過時(shí),就會產(chǎn)生空間磁場,就會有磁耦合產(chǎn)生干擾。而下面的走線形式環(huán)路小,空間小,這樣產(chǎn)生的干擾就小,下面這種形式的走線就是差分走線。

實(shí)際的PCB中,差分走線的間距放一倍的線寬就行,一般是0.3mm。并且走線必須要同一層,不在同一層的話需要打孔,打孔的話就會產(chǎn)生寄生電容,這樣就會對信號產(chǎn)生影響,所以走線最好在同一層。

2.3.偏置電壓

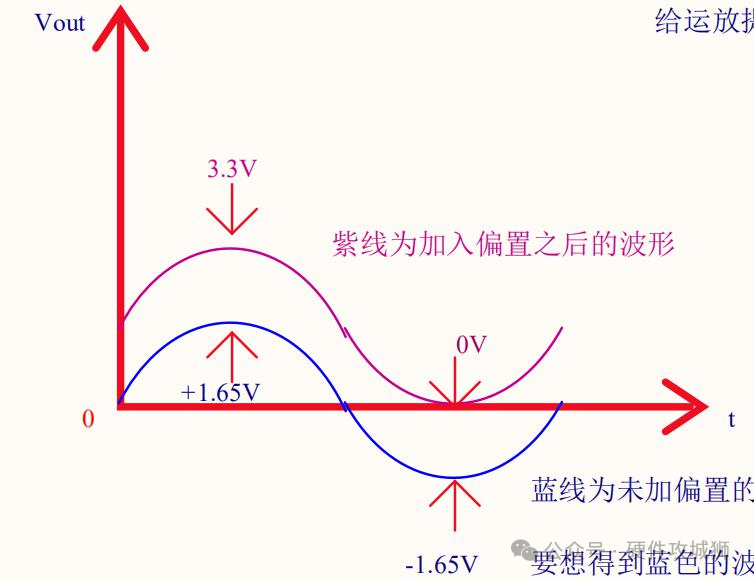

由于采樣電阻上的電流可以從下往上流,也可以從上往下流,也就是兩端的電壓可正可負(fù),那么輸入運(yùn)放的差分電壓就是正負(fù)電壓。如果運(yùn)放是正負(fù)電源供電,那么此時(shí)運(yùn)放可以輸出放大的正負(fù)電壓,但是單片機(jī)沒法檢測負(fù)壓信號,所以運(yùn)放只能單電源供電。如果運(yùn)放是單電源供電,那么又無法輸出負(fù)壓,所以需要對負(fù)壓進(jìn)行處理,也就是對負(fù)壓進(jìn)行電壓抬升,如下圖所示。這個(gè)抬升電壓也很簡單,根據(jù)波形對稱,再考慮單片機(jī)的AD采樣電壓為3.3V,所以選擇3.3V的一半。

2.4.運(yùn)放放大倍數(shù)的選擇

為了提高分辨率,讓運(yùn)放的輸出越接近3.3V越好,留一點(diǎn)余量一般考慮輸出3V即可。這里的運(yùn)放輸出3V,指的是采樣電阻流過電機(jī)的額定電流時(shí)運(yùn)放的輸出。所以這里也能看出來,如果電機(jī)的工況能夠確定,這里的運(yùn)放放大倍數(shù)也能確定。也就是如果選了個(gè)大電機(jī),而工況都是小負(fù)載電流很小,那么按照電機(jī)額定電流設(shè)計(jì)的電路板的分辨率就會低,控制效果不好。這也解釋了為什么ODrive在云臺電機(jī)這種小電流的電機(jī)上沒有進(jìn)行電流采樣,因?yàn)樗轻槍Υ箅娏髟O(shè)計(jì)的,小電流的時(shí)候分辨率太低了。對于以下電阻的取值,需要根據(jù)放大倍數(shù)來選擇。反饋電阻一般不建議大于100K,因?yàn)楦鶕?jù)大量測試大于100K的話容易引入噪音,也就是干擾。最后根據(jù)運(yùn)放的虛短和虛斷就可以求得運(yùn)放的輸出和輸入之間的關(guān)系。

![]()

在匹配好放大倍數(shù)的前提下,這里的2K電阻考慮到了一定的限流作用,而且功耗會低一些。其他沒有很多的考慮,這里選擇1K的電阻,然后和反饋電阻匹配好放大倍數(shù)也可以。

此外,有的時(shí)候會在運(yùn)放的兩個(gè)輸入端接入一個(gè)pF級別的電容,用于濾除差分干擾。但是只要能夠控制這個(gè)差分回路,可以不用接這個(gè)電容,接了這個(gè)電容可能會對信號造成延遲。所以即使加,也是加入一個(gè)很小的電容,pF級別。運(yùn)放的輸出到單片機(jī)的ADC引腳之間有一個(gè)電阻R97,這個(gè)電阻一般取值為幾十歐姆,要考慮ADC內(nèi)部的采樣保持電容的充電時(shí)間。這個(gè)電阻是充電阻抗,可以破壞走線寄生參數(shù)帶來的震蕩。因?yàn)樽呔€上存在寄生參數(shù),很容易滿足震蕩條件,加了電阻的話可以破壞震蕩條件。(?)

2.5.運(yùn)放選型

運(yùn)放選型一般從供電電壓、帶寬、速度(壓擺率)等角度考慮。供電電壓一般參考單片機(jī)的電壓來選擇, 比如3.3V的單片機(jī)就選擇3.3V供電的運(yùn)放。帶寬就是在這個(gè)頻率范圍內(nèi),放大的信號不出現(xiàn)衰減或失真,一般經(jīng)驗(yàn)值選擇5-20M。壓擺率表示運(yùn)放的輸出速度,也就是輸出電壓的變化率,一般選擇在5-10V/us。此外, 采樣電阻上的信號的頻率并不等于載波頻率,而是跟轉(zhuǎn)速有關(guān)系,也就是一個(gè)電周期的頻率大小。電流采樣的運(yùn)放不一定要選擇高速運(yùn)放,一般來說壓擺率選擇5V/us也足夠使用。

-

運(yùn)放

+關(guān)注

關(guān)注

49文章

1202瀏覽量

54330 -

電流采樣

+關(guān)注

關(guān)注

2文章

50瀏覽量

17203

原文標(biāo)題:電流采樣與運(yùn)放電路

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

偏置電流是怎樣影響運(yùn)放電路的?

請教幾個(gè)關(guān)于OPA2171AIDR運(yùn)放電流采樣的問題

整理了一個(gè)電壓轉(zhuǎn)動電流的運(yùn)放電路

電子領(lǐng)軍人物60分鐘講透馬達(dá)驅(qū)動電流環(huán)設(shè)計(jì)

張飛直播福利分享

請問F2812 AD采樣對傳感器運(yùn)放電路有什么要求?

【專輯精選】MOSFET系列教程與設(shè)計(jì)資料

運(yùn)放電路優(yōu)點(diǎn)

什么是偏置電流?偏置電流是怎樣影響運(yùn)放電路的?

偏置電流是怎樣影響運(yùn)放電路的?

電流采樣電阻一般選多大 電流采樣與運(yùn)放電路圖

電流采樣與運(yùn)放電路分享

電流采樣與運(yùn)放電路分享

評論