在高功率電子設(shè)計中,為了滿足更大的電流需求和提升系統(tǒng)可靠性,常常需要將多個MOSFET器件并聯(lián)使用。

然而,MOSFET的并聯(lián)應(yīng)用并非簡單的器件堆疊,它涉及諸多技術(shù)挑戰(zhàn),如電流均衡、熱管理和驅(qū)動匹配等。本文將從專業(yè)的角度,詳細探討MOSFET并聯(lián)在高功率設(shè)計中的原理、挑戰(zhàn)、解決方案和實際應(yīng)用。

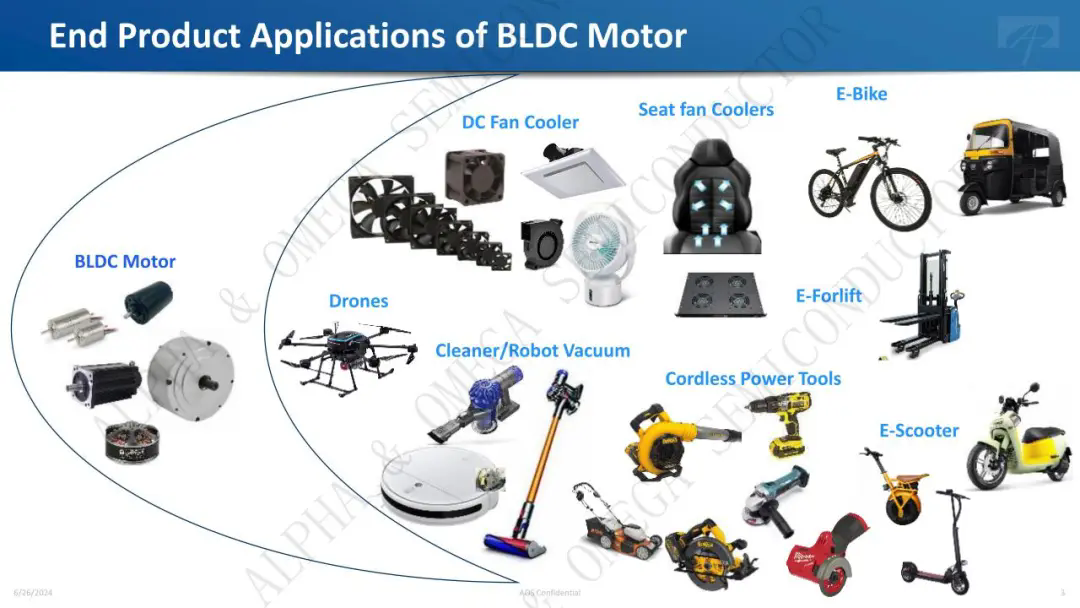

隨著電力電子技術(shù)的快速發(fā)展,MOSFET(金屬氧化物半導(dǎo)體場效應(yīng)晶體管)以其開關(guān)速度快、導(dǎo)通電阻低和驅(qū)動簡單等優(yōu)勢,廣泛應(yīng)用于開關(guān)電源、逆變器和電機驅(qū)動等領(lǐng)域。在高功率應(yīng)用中,單個MOSFET可能無法承受所需的高電流或功率,因此,采用多個MOSFET并聯(lián)的方式成為常見的解決方案。然而,MOSFET并聯(lián)涉及復(fù)雜的電氣和熱設(shè)計挑戰(zhàn),必須謹慎處理。

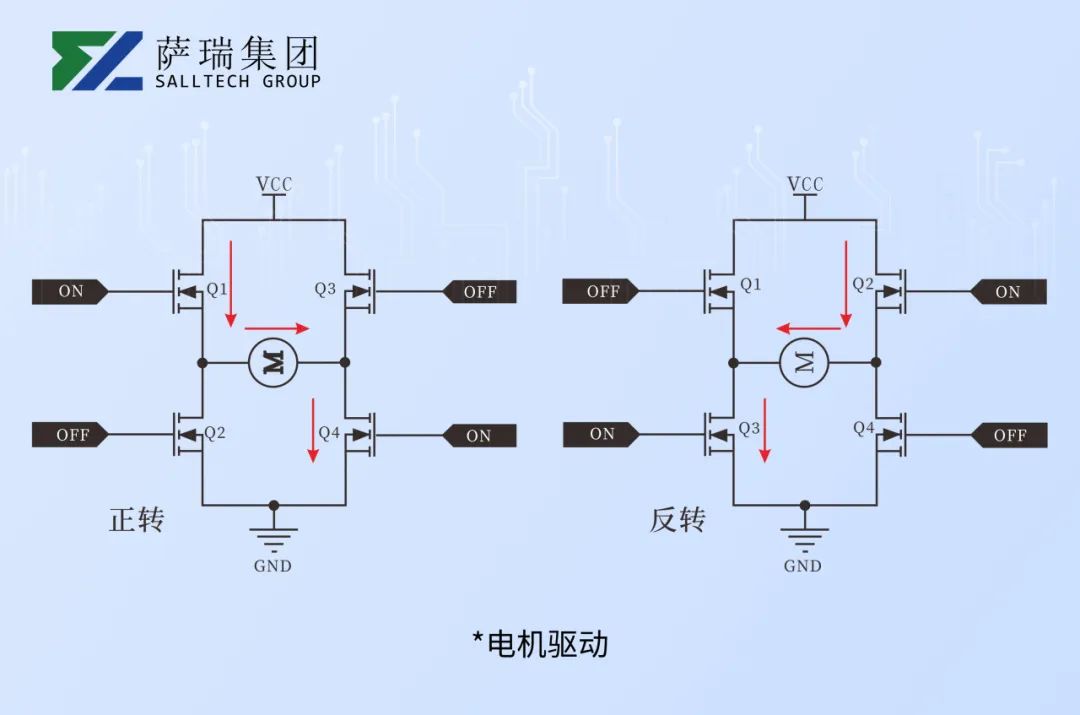

MOSFET并聯(lián)電機驅(qū)動

電路的MCU是輸出直流信號,但它的驅(qū)動能力是有限的,如需要驅(qū)動較大功率MOS管,來產(chǎn)生大電流驅(qū)動電機,設(shè)計占空比大小比例達到調(diào)整轉(zhuǎn)速目的。

電機驅(qū)動主要采用N溝道MOSFET構(gòu)建H橋驅(qū)動電路,H橋是典型的直流電機控制電路,因為它的電路外形類似字母H,故曰“H 橋”。4個開關(guān)MOS組成H的4條垂直腿,而電機就是H中的橫杠。為使電機正常運轉(zhuǎn),電路要求對角線上的一對MOS是導(dǎo)通的,應(yīng)用不同電流方向來達到控制電機正反轉(zhuǎn)的目的。

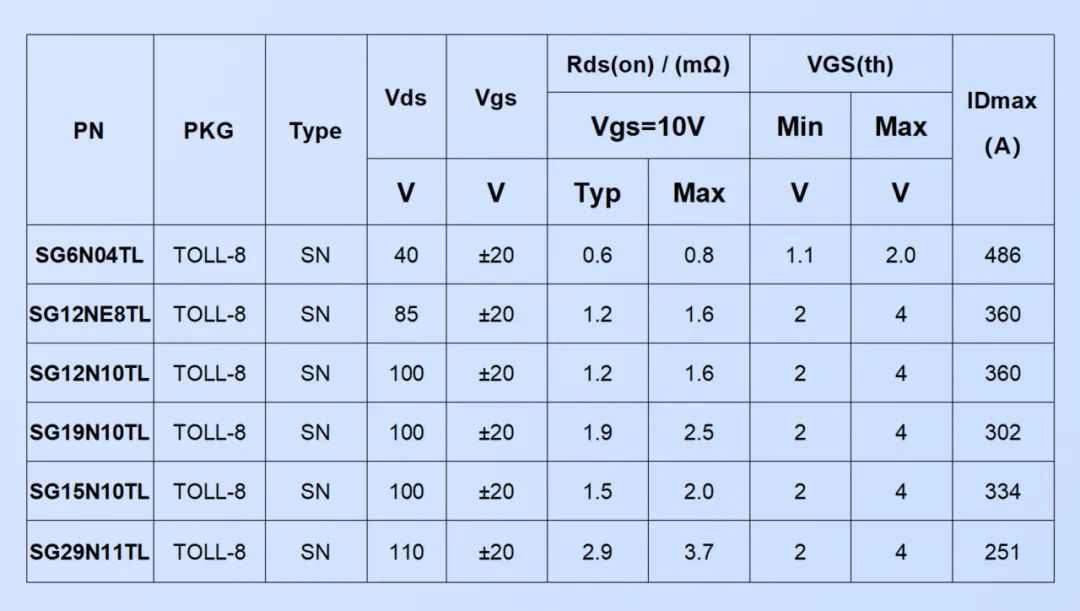

MOSFET應(yīng)用選型

TOLL選型參數(shù)表

為了便于研究MOSFET并聯(lián)時的電流均流特性,進行了簡化處理,研究了以下MOSFET并聯(lián)時的均流特性。

MOSFET并聯(lián)面臨的挑戰(zhàn)

閾值電壓不匹配電流不均衡

由于制造工藝的差異,即使是同一批次的MOSFET,其閾值電壓(VTH)、導(dǎo)通電阻(RDS(on))和跨導(dǎo)(gm)等參數(shù)也存在偏差。這些差異會導(dǎo)致并聯(lián)器件之間的電流分配不均,可能導(dǎo)致個別器件過載。

多管并聯(lián)應(yīng)用參數(shù)設(shè)計影響均流效果

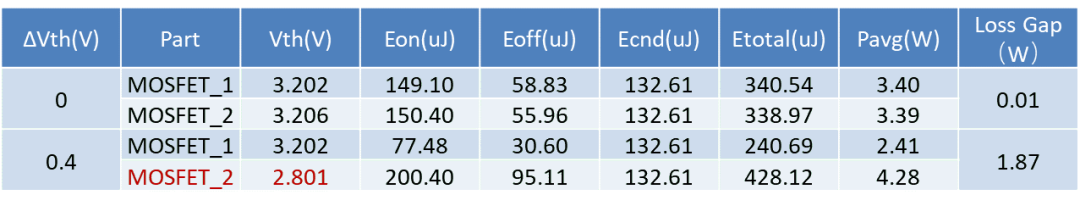

當(dāng)并聯(lián)的兩個MOSFETs具有相同的參數(shù),如內(nèi)在閾值電壓(Vth)、Rg和Ciss時,它們的開通能量(Eon)和關(guān)斷能量(Eoff)非常相似,功率損耗的差距僅為0.01W。當(dāng)2號MOSFET被Vth較低的器件替換時,其Eon和Eoff顯著增大,功率損耗比Vth較高的1號MOSFET器件高出1.87W,如表1所示。

Two MOSFETs parallel Test Result (Ton=250ns, Toff=100ns, Fs=10KHz)▲

MOSFET開關(guān)速度是影響電流平衡的另一個因素。在測試中,采用了更長的開通時間(Ton)和關(guān)斷時間(Toff),以及較高的外部驅(qū)動電阻Rg,此時不同Vth的器件之間的功率損耗差距會變大,如表2所示。當(dāng)關(guān)斷時間為100ns時,Vth較低的2號MOSFET與1號MOSFET之間的總功率損耗差(包括開關(guān)損耗和導(dǎo)通損耗)約為1.87W;而當(dāng)關(guān)斷時間為300ns時,功率損耗差距將增大到4.46W。其原因在于,當(dāng)關(guān)斷時間更長時,兩個MOSFET的Vgs達到Vth的間隔時間變長,從而使得功率損耗差距也變大。

根據(jù)測試結(jié)果,具有相同Vth值的MOSFET并聯(lián)時,MOSFET外部驅(qū)動速度的快慢是實現(xiàn)更好電流平衡性能的關(guān)鍵因素。

Two MOSFETs Parallel Test Result (Ton=380ns, Toff=300ns, Fs=10KHz)▲

MOSFET柵極驅(qū)動不匹配電流不平衡

驅(qū)動參數(shù)的一致性,包括驅(qū)動回路的電阻、電容和電感,是影響電流平衡特性的另一個因素。

當(dāng)兩個MOSFET并聯(lián)且其驅(qū)動回路的電容不同,具有較大輸入電容(Ciss)的MOSFET的開通時刻將比另一個MOSFET延遲,這會導(dǎo)致具有較大Ciss的MOSFET的開通能量(Eon)較小。然而,關(guān)斷過程則不同,較大的Ciss會導(dǎo)致關(guān)斷時刻延遲,從而導(dǎo)致較大的關(guān)斷能量(Eoff)。

通常情況下,當(dāng)兩個MOSFET并聯(lián)時,具有較大Ciss的MOSFET的Eon較小,但Eoff較大。

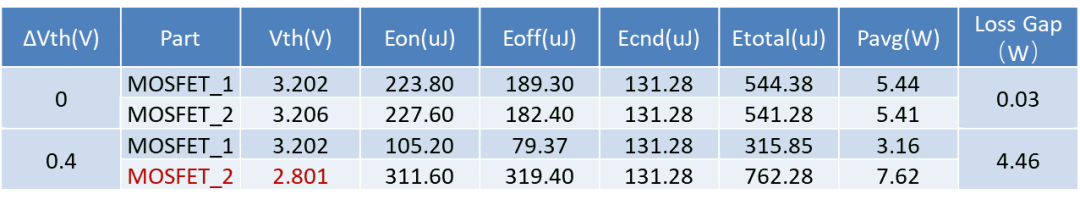

MOSFET的輸入電容或驅(qū)動回路對Eon和Eoff具有相反的影響。如果一個MOSFET的Ciss高于其他并聯(lián)MOSFET的Ciss,其Eon將減小,而Eoff則會增大。實際上,在某些條件下,Eon和Eoff的總和可以進行權(quán)衡,進而達到最小值。因此,不同Ciss對電流平衡的影響可以忽略不計,如圖1所示。在實際應(yīng)用中,建議Toff應(yīng)約為Ton的40%以實現(xiàn)最佳系統(tǒng)設(shè)計。

Ciss Variation Ratio vs Switching Loss Gap | 1 圖▲

驅(qū)動參數(shù)優(yōu)化與電流共享

外部Rg選擇對電流平衡的影響

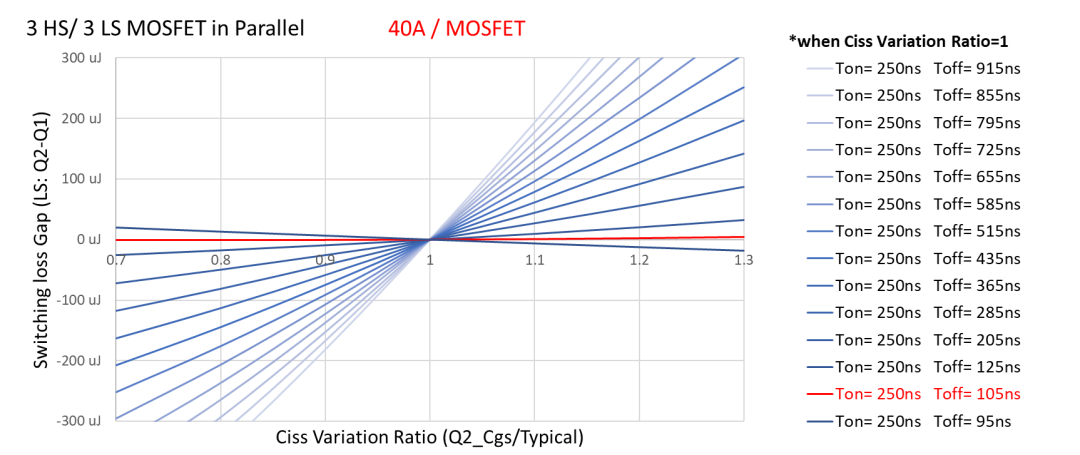

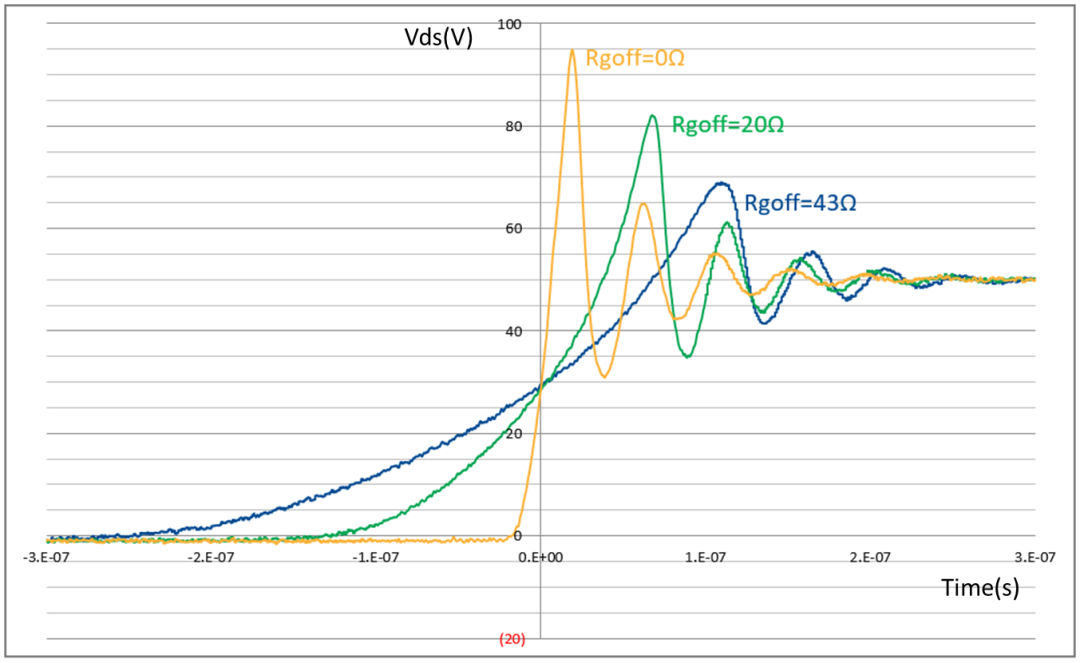

柵極驅(qū)動回路的一致性將極大地影響電流平衡性能。驅(qū)動回路應(yīng)保持一致,以滿足電流平衡的要求。其次,為了滿足系統(tǒng)效率的要求,開關(guān)速度應(yīng)盡可能快。更快的開關(guān)速度將導(dǎo)致并聯(lián)MOSFET之間的開關(guān)損耗差距變小,如圖2所示。然而,快速的開關(guān)速度可能會引發(fā)過大的電壓尖峰,如圖3所示,因此電流平衡特性和電壓尖峰之間存在權(quán)衡,在系統(tǒng)設(shè)計中應(yīng)找到平衡點。

Differences in Total Switch Losses Under Different Rg | 2 圖▲

Vds Spike Voltage vs Rgoff | 3 圖▲

結(jié)論

在高電流并聯(lián)應(yīng)用中,影響電流一致性的因素主要來自兩個方面:一是MOSFET參數(shù)的一致性,如Vth和Ciss;二是應(yīng)用中驅(qū)動回路設(shè)計和功率回路設(shè)計的不一致性。對于MOSFET制造商來說,控制生產(chǎn)工藝以獲得參數(shù)一致性至關(guān)重要。從應(yīng)用角度來看,合適的驅(qū)動設(shè)計、一致的驅(qū)動回路和功率回路電感設(shè)計同樣是確保電流一致性的關(guān)鍵因素。

-

MOSFET

+關(guān)注

關(guān)注

150文章

8620瀏覽量

220488 -

電機驅(qū)動

+關(guān)注

關(guān)注

60文章

1311瀏覽量

87837 -

高功率

+關(guān)注

關(guān)注

1文章

203瀏覽量

18716

發(fā)布評論請先 登錄

并聯(lián)MOSFET設(shè)計指南:均流、寄生參數(shù)與熱平衡

初級元器件知識之功率MOSFET

SiC MOSFET模塊并聯(lián)應(yīng)用中的動態(tài)均流問題

SiC MOSFET并聯(lián)運行實現(xiàn)靜態(tài)均流的基本要求和注意事項

互補MOSFET脈沖變壓器的隔離驅(qū)動電路設(shè)計

是否可以將6片TLV5638的REF腳并聯(lián)在一起接到基準(zhǔn)電壓?

串聯(lián)和并聯(lián)在家居布線中的應(yīng)用

AOS MOSFET并聯(lián)在高功率設(shè)計中的應(yīng)用

壓敏電阻是串聯(lián)還是并聯(lián)在電路中

兩片THS3091并聯(lián)在低頻波形完好,到高頻波形有失真,為什么?

熔斷器是串聯(lián)還是并聯(lián)在電路中

成功并聯(lián)功率MOSFET的技巧

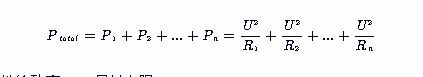

并聯(lián)電路總功率與各部分功率的關(guān)系

大功率IGBT和SiC MOSFET的并聯(lián)設(shè)計方案

MOSFET并聯(lián)在高功率設(shè)計中的應(yīng)用

MOSFET并聯(lián)在高功率設(shè)計中的應(yīng)用

評論