1997年,IBM的“深藍”超級計算機打敗了國際象棋世界冠軍加里?卡斯帕羅夫。這是超級計算機技術(shù)的一次突破性展示,也首次讓人們看到了高性能計算有一天可能超越人類智能。在接下來的十年里,我們開始將人工智能用于許多實際任務(wù),如面部識別、語言翻譯以及電影和商品推薦。

又過了15年,人工智能已經(jīng)發(fā)展到可以“結(jié)合知識”的地步。ChatGPT和Stable Diffusion等生成式人工智能可以寫詩、創(chuàng)作藝術(shù)作品、診斷疾病、編寫總結(jié)報告和計算機代碼,甚至可以設(shè)計出與人類設(shè)計相媲美的集成電路。

人工智能很有可能成為未來所有人類活動的數(shù)字助手。ChatGPT就是一個很好的例子,它展示了人工智能有助于推動高性能計算的普及性應(yīng)用,為社會中的每一個人帶來益處。

所有這些奇妙的人工智能應(yīng)用都?xì)w功于3個因素:高效機器學(xué)習(xí)算法的創(chuàng)新、可用于訓(xùn)練神經(jīng)網(wǎng)絡(luò)的海量數(shù)據(jù),以及通過半導(dǎo)體技術(shù)發(fā)展實現(xiàn)的節(jié)能計算進步。雖然最后這一項貢獻無處不在,但它在生成式人工智能革命中的重要性卻未得到應(yīng)有的重視。

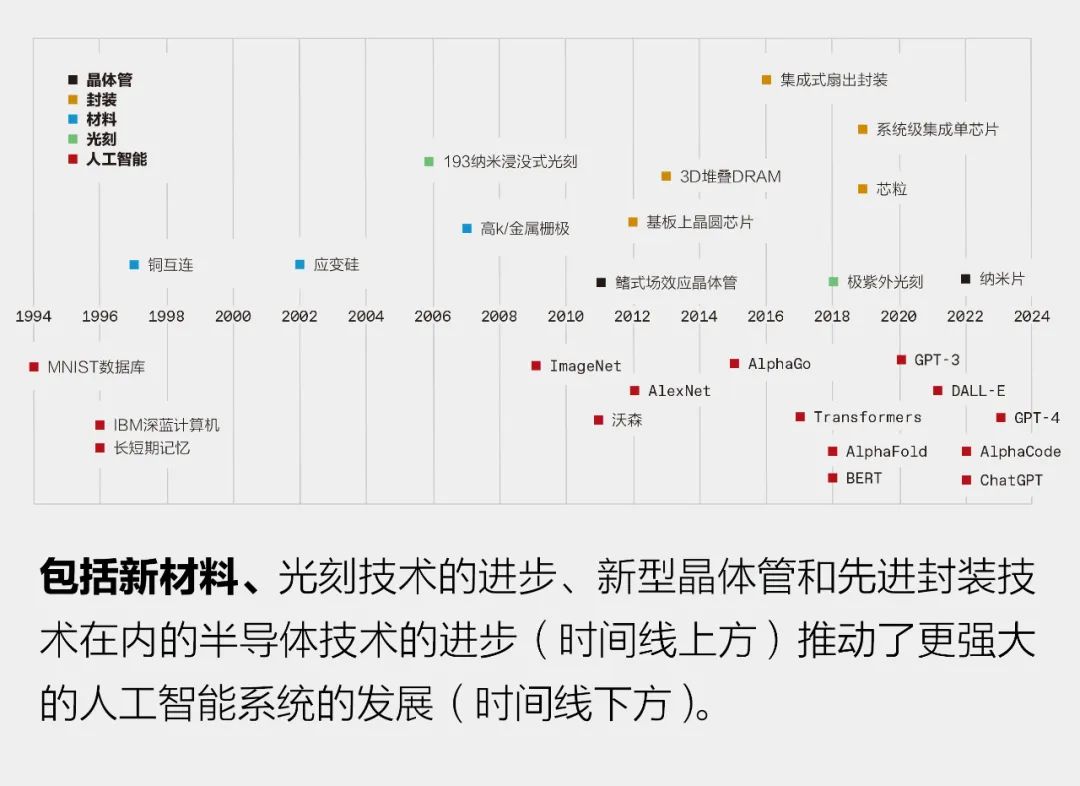

在過去30年里,人工智能的重要里程碑都是通過當(dāng)時最先進的半導(dǎo)體技術(shù)實現(xiàn)的,沒有它們,這些里程碑就不可能實現(xiàn)。深藍計算機是通過結(jié)合0.6微米和0.35微米節(jié)點的芯片制造技術(shù)實現(xiàn)的;贏得ImageNet競賽并開啟當(dāng)前機器學(xué)習(xí)時代的深度神經(jīng)網(wǎng)絡(luò)是用40納米技術(shù)實現(xiàn)的;AlphaGo使用28納米技術(shù)征服了圍棋世界,初版ChatGPT是在采用5納米技術(shù)的計算機上訓(xùn)練的。而最新版的ChatGPT則依靠使用了更先進的4納米技術(shù)的服務(wù)器提供支持。從軟件和算法到架構(gòu)、電路設(shè)計和設(shè)備技術(shù),人工智能所涉及的每一層計算機系統(tǒng)都是提高人工智能性能的倍增器。但公平地說,基礎(chǔ)晶體管技術(shù)是實現(xiàn)上層進步的關(guān)鍵。

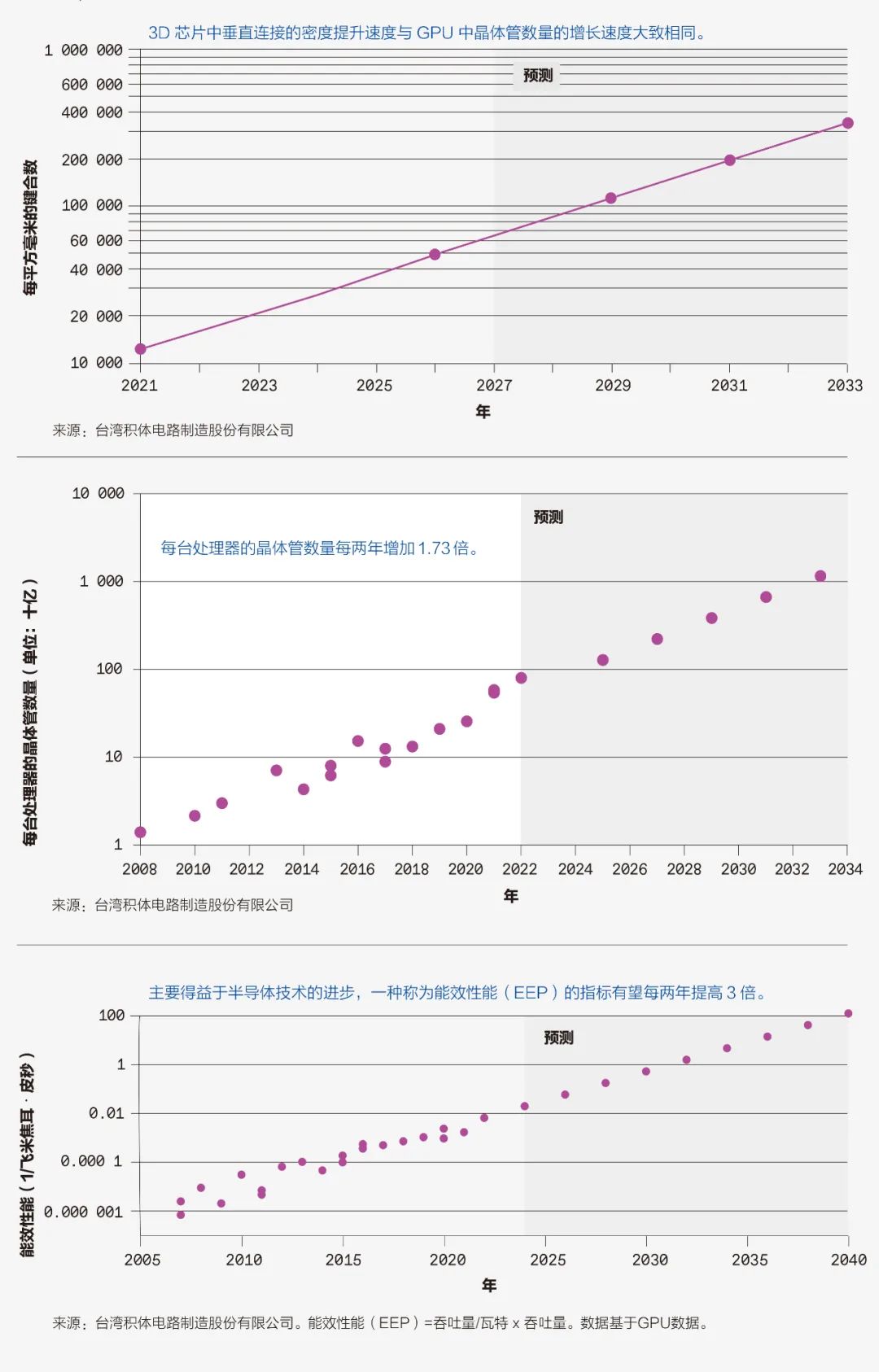

如果人工智能革命要繼續(xù)按照當(dāng)前的速度發(fā)展下去,將需要半導(dǎo)體行業(yè)提供更多的支持。10年內(nèi),它將需要擁有1萬億個晶體管的GPU,是目前常見GPU所擁有的晶體管數(shù)量的10倍。

人工智能模型規(guī)模的持續(xù)增長

過去5年里,人工智能訓(xùn)練所需的計算能力和內(nèi)存訪問量提高了幾個數(shù)量級。例如,訓(xùn)練GPT-3需要相當(dāng)于每秒超過5000千萬億次的運算持續(xù)一整天,并需要3萬億字節(jié)(3TB)的內(nèi)存容量。

新的生成式人工智能應(yīng)用所需的計算能力和內(nèi)存訪問量還在繼續(xù)快速增長。現(xiàn)在,我們需要回答一個緊迫的問題:半導(dǎo)體技術(shù)如何才能跟上這一步伐?

從集成器件到集成芯粒

自集成電路發(fā)明以來,半導(dǎo)體技術(shù)一直致力于縮小特征尺寸,以便將更多的晶體管塞進極小的芯片中。今天,集成已經(jīng)上升到了一個更高的層次;我們將超越二維縮放,進入三維系統(tǒng)集成。我們正在將許多芯片組裝成一個緊密集成的大規(guī)模互連系統(tǒng)。這是半導(dǎo)體技術(shù)集成的范式轉(zhuǎn)變。

在人工智能時代,系統(tǒng)能力直接與系統(tǒng)集成的晶體管數(shù)量成正比。限制晶體管集成數(shù)量的主要因素之一是光刻芯片制造工具被設(shè)計成只能制造不超過約800平方毫米的集成電路,這被稱為“光罩限制”。但現(xiàn)在,我們可以將集成系統(tǒng)的尺寸擴展到光刻技術(shù)的光罩限制之外。通過將幾塊芯片連接到一個更大的中介層(一塊內(nèi)置互連的硅片)上,我們可以集成一個能夠比單芯片包含更多器件的系統(tǒng)。例如,臺積電的基板上晶圓芯片(CoWoS)技術(shù)可以容納多達6個光罩范圍的計算芯片,以及十幾個高帶寬存儲器(HBM)芯片。

高帶寬存儲器是另一種對人工智能而言越來越重要的關(guān)鍵半導(dǎo)體技術(shù):該技術(shù)可將芯片堆疊在一起進行系統(tǒng)集成,臺積電稱之為“集成片上系統(tǒng)”(SoIC)。高帶寬存儲器由一堆動態(tài)隨機存取存儲器(DRAM)垂直互連芯片組成,位于控制邏輯集成電路之上。它使用了稱為“硅通孔”的垂直互連來讓信號通過每塊芯片,并使用了焊錫球連接內(nèi)存芯片。如今,高性能圖形處理器(GPU)廣泛使用了高帶寬存儲器。

未來,3D 系統(tǒng)級集成單芯片技術(shù)可以為目前的常規(guī)高帶寬存儲器技術(shù)提供替代方案,在堆疊芯片之間實現(xiàn)更密集的垂直互連。最新進展顯示,高帶寬存儲器測試結(jié)構(gòu)使用混合鍵合堆疊了12層芯片,相較于目前使用的焊錫球,這種銅對銅連接實現(xiàn)了更高的密度。這種內(nèi)存系統(tǒng)在低溫下在較大的基礎(chǔ)邏輯芯片之上進行鍵合,總厚度僅為600微米。

隨著由大量芯片組成的高性能計算系統(tǒng)運行大型人工智能模型,高速有線通信可能很快會限制計算速度。如今,數(shù)據(jù)中心已經(jīng)在使用光互連來連接服務(wù)器機架。很快,我們將需要基于硅光子技術(shù)與GPU和中央處理器(CPU)一起封裝的光學(xué)接口。它們將提高帶寬的能源效率和面積效率,實現(xiàn)直接的GPU到GPU光學(xué)通信,使成百上千臺服務(wù)器像一個具有統(tǒng)一內(nèi)存的巨型GPU一樣工作。人工智能應(yīng)用的需求將讓硅光子技術(shù)將成為半導(dǎo)體行業(yè)最重要的使能技術(shù)之一。

邁向萬億晶體管GPU

如前所述,用于人工智能訓(xùn)練的典型GPU芯片已經(jīng)達到了光罩范圍限制,其晶體管數(shù)量約為1000億個。要持續(xù)晶體管數(shù)量增多的趨勢,將需要用2.5D或3D集成互連的多芯片來執(zhí)行計算。通過基板上晶圓芯片、集成片上系統(tǒng)或相關(guān)的先進封裝技術(shù)集成多個芯片,可以使每個系統(tǒng)的總晶體管數(shù)量遠(yuǎn)遠(yuǎn)超過單塊芯片所能容納芯片的數(shù)量。我們預(yù)測,在10年內(nèi),一個多芯粒GPU將擁有超過1萬億個晶體管。

我們需要在一個3D堆棧中將所有這些芯粒連接起來,不過幸運的是,業(yè)界已經(jīng)能夠迅速縮小垂直互連的間距,從而提高連接的密度,而且還有很大的進步空間。我們認(rèn)為互連密度完全可以提高一個數(shù)量級,甚至更多。

GPU的能效性能趨勢

那么,這些硬件創(chuàng)新技術(shù)將如何提升系統(tǒng)性能?

如果關(guān)注能效性能(EEP)這一指標(biāo)的穩(wěn)步提升,我們便可以從服務(wù)器GPU中看到這一趨勢。能效性能是系統(tǒng)能源效率和速度的綜合衡量指標(biāo)。在過去15年里,半導(dǎo)體行業(yè)的能效性能每兩年提高大約3倍。我們相信這一趨勢將按照歷史速度繼續(xù)。它將受到來自多方面創(chuàng)新的推動,包括新材料、設(shè)備和集成技術(shù)、極紫外光刻、電路設(shè)計、系統(tǒng)架構(gòu)設(shè)計以及所有這些技術(shù)元素的協(xié)同優(yōu)化等。

特別是我們在此討論的先進封裝技術(shù),它將推動能效性能的提高。此外,系統(tǒng)技術(shù)協(xié)同優(yōu)化等概念也會越來越重要,系統(tǒng)技術(shù)協(xié)同優(yōu)化是將GPU的不同功能部分分散到各自的芯粒上,并使用性能最佳、最經(jīng)濟的技術(shù)來構(gòu)建每個部分。

3D集成電路的米德-康維時刻

1978年,加州理工學(xué)院教授卡沃?米德(Carver Mead)和施樂帕洛阿爾托研究中心的琳?康維(Lynn Conway)發(fā)明了一種用于集成電路的計算機輔助設(shè)計方法。他們使用了一套設(shè)計規(guī)則來描述芯片尺寸,使工程師無須深入了解工藝技術(shù)就能輕松設(shè)計超大規(guī)模集成電路。

現(xiàn)在,3D芯片設(shè)計也需要類似的能力。如今的設(shè)計師需要了解芯片設(shè)計、系統(tǒng)架構(gòu)設(shè)計以及軟硬件優(yōu)化。制造商需要了解芯片技術(shù)、3D集成電路技術(shù)和先進封裝技術(shù)。正如1978年那樣,我們再次需要一種描述這些技術(shù)的通用語言,讓電子設(shè)計工具能夠理解這些技術(shù)。這種硬件描述語言可以讓設(shè)計師自由地進行3D集成電路系統(tǒng)設(shè)計,而不必考慮底層技術(shù)。這種語言已經(jīng)在發(fā)展之中了,一種名為3Dblox的開源標(biāo)準(zhǔn)已經(jīng)被當(dāng)今大多數(shù)技術(shù)公司和電子設(shè)計自動化公司接受。

隧道盡頭的未來

在人工智能時代,半導(dǎo)體技術(shù)是推動新的人工智能能力和應(yīng)用發(fā)展的關(guān)鍵因素。新的GPU不再受制于過去的標(biāo)準(zhǔn)尺寸和形式因素。新的半導(dǎo)體技術(shù)不再局限于在二維平面上來縮小下一代晶體管。人工智能集成系統(tǒng)可以由盡可能多的節(jié)能晶體管、專用計算工作負(fù)載的高效系統(tǒng)架構(gòu)以及軟硬件優(yōu)化關(guān)系組成。

在過去50年里,半導(dǎo)體技術(shù)的發(fā)展就像在隧道中行走。前方的道路是清晰的,因為有一條明確的路徑,而且大家都知道需要縮小晶體管。

現(xiàn)在,我們已經(jīng)走到了隧道的盡頭,之后的半導(dǎo)體技術(shù)將越來越難開發(fā)。然而在隧道之外,還有更多的可能性在等待著我們。

-

gpu

+關(guān)注

關(guān)注

28文章

4925瀏覽量

130902 -

晶體管

+關(guān)注

關(guān)注

77文章

10004瀏覽量

141146 -

人工智能

+關(guān)注

關(guān)注

1805文章

48898瀏覽量

247857

原文標(biāo)題:通往萬億晶體管GPU之路

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

人工智能發(fā)展需要新的芯片技術(shù)

人工智能發(fā)展需要新的芯片技術(shù)

評論