原創(chuàng) StrivingJallan 芯片SIPI設(shè)計(jì)

為了克服硅中間層技術(shù)的尺寸限制,并實(shí)現(xiàn)更好的處理器和存儲(chǔ)器集成,開發(fā)了一種基于硅interposer的新型2.5D SiP,如圖所示。多個(gè)芯片集成在一個(gè)接口層(interposer)上,用高密度、薄互連連接,這種高密度的信號(hào),再加上硅interposer設(shè)計(jì),需要仔細(xì)的設(shè)計(jì)和徹底的時(shí)序分析。

對(duì)于需要在處理器和大容量存儲(chǔ)器單元之間進(jìn)行高速數(shù)據(jù)傳輸?shù)母叨藘?nèi)存密集型應(yīng)用程序來說,走線寬度和長(zhǎng)度是一個(gè)主要挑戰(zhàn)。HBM以更小的外形實(shí)現(xiàn)更高的帶寬,同時(shí)使用更少的功耗,interposer技術(shù)最適合峰值帶寬、每瓦帶寬和每區(qū)域容量是有價(jià)值指標(biāo)的應(yīng)用,例如圖形應(yīng)用處理器單元(gpu)、高性能計(jì)算、服務(wù)器、網(wǎng)絡(luò)和客戶端應(yīng)用。

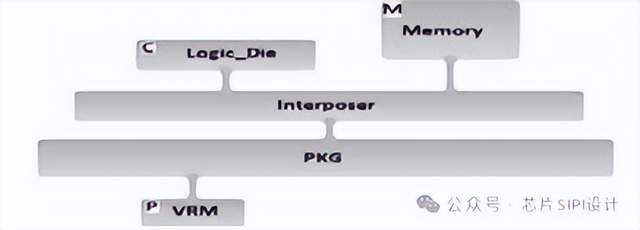

下圖為Si interposer設(shè)計(jì)側(cè)視圖:兩個(gè)芯片并排放置,通過金屬層走線連接。硅interposer用于建立具有高密度凸點(diǎn)的die to die連接。其他連接則通過interposer直接連接到IC封裝基板。給出了芯片RDL在集成電路設(shè)計(jì)環(huán)境中的布局,以及封裝設(shè)計(jì)環(huán)境中芯片RDL在封裝頂部的布局。

為了獲得良好的SI性能,系統(tǒng)封裝必須具有低傳輸損耗和短信號(hào)路徑達(dá)到所要求的電氣規(guī)格,由于高密度互連路由,interposer集成導(dǎo)致新的電氣挑戰(zhàn)。總功耗的降低要求在盡可能低的電壓和最高可靠的頻率下運(yùn)行。這導(dǎo)致需要將電感與位于晶體管上的decap,以保持電壓,獨(dú)立于正在執(zhí)行的操作,并降低接地電阻。由于必須在一個(gè)封裝中平衡多種要求,例如降低電壓,增加晶體管數(shù)量,以及模擬和混合信號(hào)設(shè)計(jì),因此提出了新的挑戰(zhàn)。

下圖顯示了帶有邏輯和存儲(chǔ)芯片的interposer層的示意圖,兩個(gè)DIE并排組裝,使用細(xì)銅線來進(jìn)行DIE to DIE連接。

整個(gè)存儲(chǔ)系統(tǒng)使用硅interposer集成到封裝中,如下圖所示,interposer尺寸為30mm × 25mm。中間層頂部附有20mm × 24mm的高性能處理器芯片。完全集成的內(nèi)存系統(tǒng)包括四層HBM內(nèi)存,帶寬為512GB/s。處理器和HBM都使用micro bump連接到interposer上。interposer通過傳統(tǒng)的倒裝芯片bump安裝在基板上,處理器有189000個(gè)micro bumps,中間處理器有34000多個(gè)倒裝芯片bump。四個(gè)DIE以2.5mm的間隙并排放置。線寬為2μm實(shí)現(xiàn)了die to die連接,為了提高布局的性能,處理器DIE被分成六個(gè)具有相同數(shù)量bump的DIE,從D1到D6,如下圖所示。

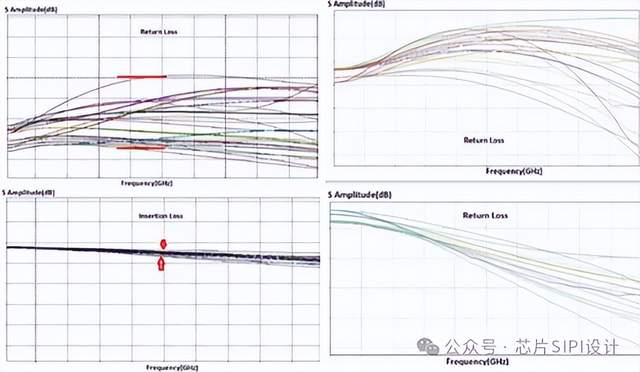

下圖顯示了回波損耗和插入損耗,左圖顯示回波損耗小于-22dB,可以支持最高可達(dá)2800MT/s interposer數(shù)據(jù)傳輸設(shè)計(jì);右圖顯示了PoP設(shè)計(jì)的回波損耗和插入損耗。在2800MT/s傳輸速率的介面設(shè)計(jì)中,插入損耗為-1dB。

結(jié)果表明,與傳統(tǒng)的PoP 技術(shù)相比,interposer具有更好的回波損耗和插入損耗性能。回波損耗提高了-8dB,反演損耗提高了-1dB,通過在互連之間使用接地保護(hù)帶,可以最大限度地減少interposer中的串?dāng)_。接下來是進(jìn)行時(shí)域分析,下圖是含有interposer結(jié)構(gòu)的仿真拓?fù)洹?/p>

在仿真中,interposer表示與HBM互連的處理器的s參數(shù),為了準(zhǔn)確地仿真IO切換行為,IBIS模型分別應(yīng)用到處理器和HBM模塊中。下圖為POP封裝仿真拓?fù)洹?/p>

對(duì)于SI分析,時(shí)域仿真使用s參數(shù)模型來檢查眼圖打開和抖動(dòng),為了電源的完整性,s參數(shù)可以簡(jiǎn)化為檢查頻域的輸入阻抗曲線。

眼高和抖動(dòng)通過眼圖仿真得到,interposer和PoP設(shè)計(jì)的仿真結(jié)果分別如下圖左右所示。與PoP封裝相比,左側(cè)為帶有interposer設(shè)計(jì),右側(cè)結(jié)果為Pop封裝結(jié)果,可以看到interposer的設(shè)計(jì)有更大的眼圖開窗。

與 PoP設(shè)計(jì)相比,interposer設(shè)計(jì)中的抖動(dòng)也更好,interposer中HBM和處理器芯片之間的互連長(zhǎng)度更小/更短,這都表明interposer技術(shù)提高了SI 的性能。

聲明:本網(wǎng)站部分文章轉(zhuǎn)載自網(wǎng)絡(luò),轉(zhuǎn)發(fā)僅為更大范圍傳播。 轉(zhuǎn)載文章版權(quán)歸原作者所有,如有異議,請(qǐng)聯(lián)系我們修改或刪除。聯(lián)系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

封裝

+關(guān)注

關(guān)注

128文章

8566瀏覽量

144901 -

PCB

+關(guān)注

關(guān)注

1文章

2072瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

高密度配線架和中密度的區(qū)別

mpo高密度光纖配線架的安裝方法

高密度系統(tǒng)級(jí)封裝:技術(shù)躍遷與可靠性破局之路

光纖高密度odf是怎么樣的

高密度封裝失效分析關(guān)鍵技術(shù)和方法

高密度3-D封裝技術(shù)全解析

LM5145EVM-HD-20A高密度評(píng)估模塊

揭秘高密度有機(jī)基板:分類、特性與應(yīng)用全解析

什么是高密度DDR芯片

高密度互連,引爆后摩爾技術(shù)革命

高密度Interposer封裝設(shè)計(jì)的SI分析

高密度Interposer封裝設(shè)計(jì)的SI分析

評(píng)論