在脈沖雷達應用中,從發(fā)射到接收操作的過渡期間需要快速開啟/關閉高功率放大器 (HPA)。典型的轉(zhuǎn)換時間目標可能小于1 s。傳統(tǒng)上,這是通過漏極控制來實現(xiàn)的。漏極控制需要在28 V至50 V的電壓下切換大電流。已知開關功率技術可以勝任這一任務,但會涉及額外的物理尺寸和電路問題。在現(xiàn)代相控陣天線開發(fā)中,雖然要求盡可能低的SWaP(尺寸重量和功耗),但希望消除與HPA漏極開關相關的復雜問題。

本文提出了一種獨特但簡單的柵極脈沖驅(qū)動電路,為快速開關HPA提供了另一種方法,同時消除了與漏極開關有關的電路。實測切換時間小于200 ns,相對于1 s的目標還有一些裕量。其他特性包括:解決器件間差異的偏置編程能力,保護HPA免受柵極電壓增加影響的柵極箝位,以及用于優(yōu)化脈沖上升時間的過沖補償。

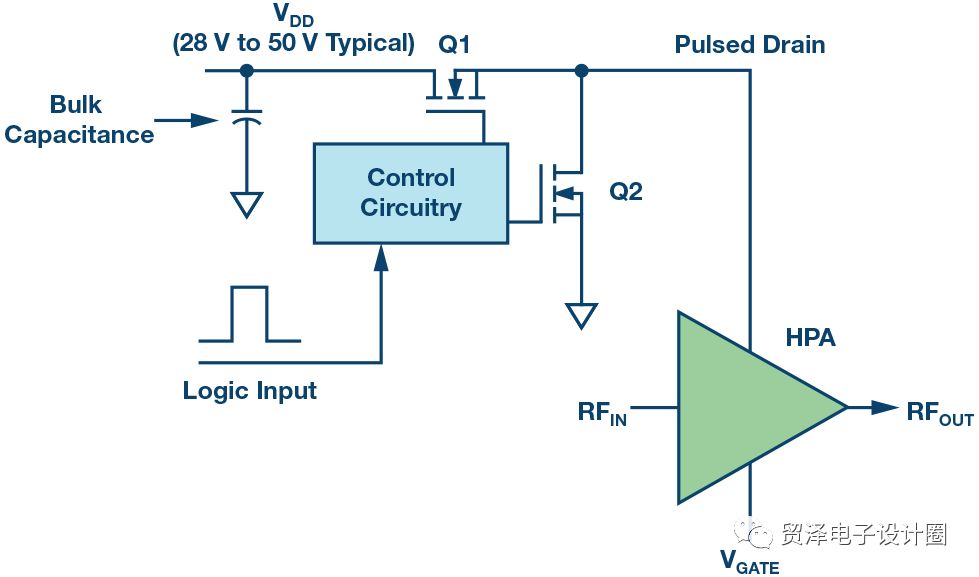

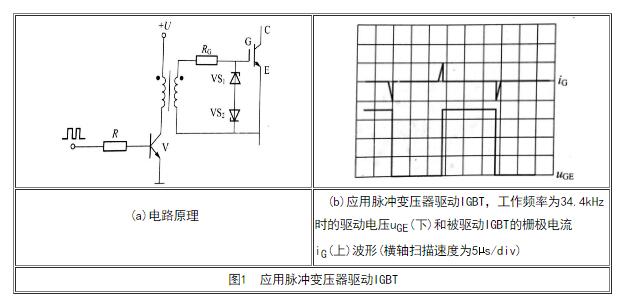

典型漏極脈沖配置通過漏極控制開關HPA的典型配置如圖1所示。一個串聯(lián)FET開啟輸入HPA的高電壓。控制電路需要將邏輯電平脈沖轉(zhuǎn)換為更高電壓以使串聯(lián)FET導通。

此配置的難點包括:

●大電流的切換要求從大容量電容到HPA漏極引腳的路徑是一條低電感路徑。

●關閉時,漏極電容保有電荷,需要額外的放電路徑。這是通過額外的FET Q2來實現(xiàn)的,對控制電路的約束隨之增加:Q1和Q2絕不能同時使能。

●很多情況下,串聯(lián)FET是N溝道器件。這要求控制電路產(chǎn)生一個高于HPA漏極電壓的電壓才能開啟。

控制電路的設計方法已是眾所周知且行之有效。然而,相控陣系統(tǒng)不斷期望集成封裝并降低SWaP,因此希望消除上述難點。實際上,人們的愿望是完全消除漏極控制電路。

圖1. 傳統(tǒng)HPA脈沖漏極配置。

推薦柵極脈沖電路柵極驅(qū)動電路的目標是將邏輯電平信號轉(zhuǎn)換成合適的GaN HPA柵極控制信號。需要一個負電壓來設置適當?shù)钠?a href="http://m.xsypw.cn/tags/電流/" target="_blank">電流,以及一個更大的負電壓來關閉器件。因此,電路應接受正邏輯電平輸入并轉(zhuǎn)換為兩個負電壓之間的脈沖。電路還需要克服柵極電容影響,提供急速上升時間,過沖應極小或沒有。

對柵極偏置設置的擔憂是,偏置電壓的小幅增加可能導致HPA電流的顯著增加。這就增加了一個目標,即柵極控制電路應非常穩(wěn)定,并有一個箝位器來防止受損。另一個問題是,設置所需漏極電流時,不同器件的最佳偏置電壓有差異。這種差異使得人們更希望有系統(tǒng)內(nèi)可編程柵極偏置特性。

圖2. 推薦HPA柵極驅(qū)動電路。

圖2所示電路達成了所述的全部目標。運算放大器U1使用反相單負電源配置。利用一個精密DAC設置運算放大器基準電壓,以實現(xiàn)V+引腳上的增益。當邏輯輸入為高電平時,運算放大器箝位到負供電軌。當輸入為低電平時,運算放大器輸出接近一個小的負值,該值由電阻值和DAC設置決定。反相配置是故意選擇的,目的是當邏輯輸入為低電平或接地時開啟HPA,因為邏輯低電平的電壓差異小于邏輯高電平。采用軌到軌運算放大器,它具有較大壓擺率和足夠的輸出電流驅(qū)動能力,適合該應用。

元件值選擇如下:

●R1和R2設置運放增益。

●DAC設置連同R3和R4決定運算放大器V+引腳的基準電壓。C1和R3針對低通濾波器噪聲而選擇。

●R5和R6用于實現(xiàn)重要的箝位功能。這是因為運放的VCC引腳以地為基準,所以這是運放輸出的最大值。R5和R6為–5 V電源提供一個電阻分壓器。

●R5的不利影響是由于柵極電容,它會減慢脈沖響應。這要通過增加C3來補償,以實現(xiàn)陡峭的脈沖。

●C2的值較小,用以限制運放輸出脈沖上升沿的過沖。

實測數(shù)據(jù)用于驗證電路的測試設置如圖3所示。對精密DAC、運算放大器和HPA使用評估板。一個脈沖發(fā)生器用于模擬1.8 V邏輯信號。信號發(fā)生器連續(xù)工作,利用一個輸入帶寬高于RF頻率的RF采樣示波器測量HPA對RF信號的開啟/關閉。

圖3. 測試設置。

測試所用的元器件值參見表1。

表1. 所用元器件值

實測開啟時間如圖4所示。時間標度為每格500 ns,RF信號的上升時間小于200 ns。對于測量從柵極脈沖開始到RF脈沖上升沿結束的時間的系統(tǒng),可以看到開啟時間約為300 ns,這說明系統(tǒng)分配1s用于發(fā)射到接收轉(zhuǎn)換會有相當可觀的裕量。

圖4. 實測HPA開啟時間。

圖5. 實測HPA關閉時間。

實測關閉時間如圖5所示。時間標度同樣是每格500 ns,下降時間明顯快于上升時間,同樣遠小于200 ns,說明系統(tǒng)分配1 s用于發(fā)射到接收轉(zhuǎn)換會有相當可觀的裕量。

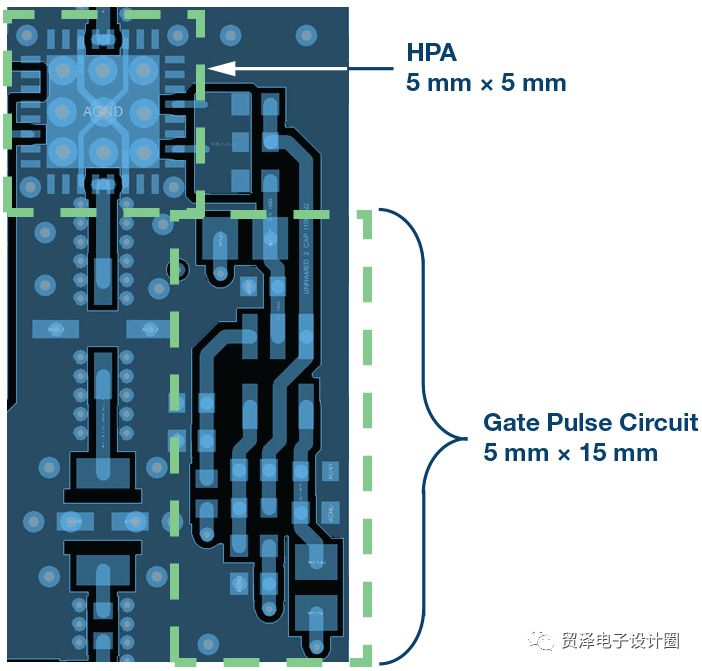

布局考慮對一個代表性布局做了尺寸研究,如圖6所示。柵極脈沖電路的運算放大器部分放置在通向HPA輸入的RF路徑附近。精密DAC未顯示出來,假定其放置在控制部分中,為多個發(fā)射通道提供輸入。布局研究表明,可將該電路添加到實際的低成本PWB實現(xiàn)方案中,發(fā)射RF電路所需的額外空間極小。

圖6. 物理尺寸分配。

結語本文提出了一種獨特的柵極脈沖電路,并進行了HPA快速開/關評估。

其特性包括:

-

轉(zhuǎn)換時間小于200 ns。

-

兼容任何邏輯輸入。

-

通過可編程偏置消除器件間差異。

-

提供箝位保護以設置最大柵極電壓。

-

上升時間/過沖補償。

-

尺寸支持高密度相控陣應用。

先進電子系統(tǒng)集成度不斷提高,要求縮小物理尺寸,因此可以想象,這種電路及其方法的其他變化,將開始在需要快速HPA轉(zhuǎn)換時間的相控陣應用中激增。

作者

Peter Delos

Peter Delos 是ADI公司航空航天和防務部的技術主管。他于1990年獲得美國弗吉尼亞理工大學電氣工程學士學位(BSEE),并于2004年獲得美國新澤西理工學院電氣工程碩士學位(MSEE)。1990年至1997年,他為美國海軍核電站計劃工作。工作內(nèi)容包括:完成海軍核電站學校官員計劃,擔任海軍潛艇基地教師,領導康涅狄格州格羅頓的海狼級潛艇的現(xiàn)場電氣工程師。

1997年,他接受了洛克希德馬丁公司在新澤西州穆爾斯頓的一個職位,開始了一段碩果累累的職業(yè)歷程,為多個雷達和電子戰(zhàn)計劃開發(fā)接收機/激勵器和頻率合成器。這段經(jīng)驗包括架構定義、詳細設計、快速原型開發(fā)、制造、現(xiàn)場安裝和協(xié)調(diào)多個工程專業(yè)。他的工作引領了相控陣接收器/激勵器從集中式架構到陣列上數(shù)字波束合成系統(tǒng)的轉(zhuǎn)變。

Jarrett Liner

Jarrett Liner是ADI公司航空航天與防務部門(位于美國北卡羅來納州格林斯博羅)的RF系統(tǒng)應用工程師,他在射頻系統(tǒng)和器件設計方面有著豐富的經(jīng)驗。

此前,他是防務和航空航天領域碳化硅襯底氮化鎵放大器應用工程師。其先前的經(jīng)歷還包括從事13年的RF IC WLAN功率放大器和前端模塊的設計與測試工作。他曾作為電子技師在美國海軍服役6年。Jarrett于2004年獲得美國北卡羅來納州農(nóng)業(yè)技術州立大學(位于北卡羅來納州格林斯博羅)電氣工程學士學位。

當Jarrett不在實驗室仿真電路或測量數(shù)據(jù)時,他可能在山地上騎自行車、在健身房教授自行車課程、跑步或者在庭院與他的四個孩子追逐嬉戲。

-

ADI

+關注

關注

148文章

46026瀏覽量

259041 -

柵極驅(qū)動

+關注

關注

8文章

209瀏覽量

23555

原文標題:能否在200 ns內(nèi)開啟或關閉RF源?看完這篇你就知道了。。。

文章出處:【微信號:Mouser-Community,微信公眾號:貿(mào)澤電子設計圈】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

對稱柵極控制驅(qū)動電路

柵極驅(qū)動應 支持高功率放大器快速開啟/關閉

獨特的柵極驅(qū)動應用能否在200 ns內(nèi)開啟或關閉RF源?

DVRFD630-275,開發(fā)板是一種通用電路板,旨在簡化IXRFD630柵極驅(qū)動器的評估

一種新型實用的IGBT驅(qū)動電路

一種小功率步進電機驅(qū)動電路的設計與實現(xiàn)

一種用于功率MOSFET的諧振柵極驅(qū)動電路

一種快沿脈沖信號發(fā)生器的設計

一種獨特但簡單的柵極脈沖驅(qū)動電路

一種獨特但簡單的柵極脈沖驅(qū)動電路

評論