PLD(Programmable Logic Device,可編程邏輯器件)設計流程是指從設計概念到最終實現的一系列步驟,用于創建和驗證可編程邏輯器件的功能。

1. 需求分析(Requirement Analysis)

- 定義功能 :明確PLD需要實現的具體功能和性能指標。

- 確定輸入輸出 :列出所有輸入信號和輸出信號,并定義它們的屬性。

- 性能要求 :包括速度、功耗、面積等。

2. 設計規劃(Design Planning)

3. 概念設計(Conceptual Design)

- 邏輯圖 :繪制邏輯圖,描述信號流和邏輯關系。

- 狀態機設計 :對于需要狀態機的應用,設計狀態機的狀態轉換圖。

4. HDL編碼(HDL Coding)

- 選擇HDL :根據項目需求選擇VHDL或Verilog等硬件描述語言。

- 編寫代碼 :根據邏輯圖和狀態機設計,編寫HDL代碼。

- 模塊化設計 :將代碼劃分為模塊,便于管理和復用。

5. 代碼審查(Code Review)

- 同行評審 :代碼編寫完成后,進行同行評審,檢查代碼的正確性和可讀性。

- 代碼規范 :確保代碼遵循公司或項目的編碼規范。

6. 綜合(Synthesis)

- 綜合工具選擇 :選擇合適的綜合工具,如Xilinx ISE、Synopsys DC等。

- 綜合過程 :將HDL代碼轉換為門級網表。

- 資源利用報告 :分析綜合結果,檢查資源使用情況。

7. 優化(Optimization)

- 時序優化 :調整設計以滿足時序要求。

- 面積優化 :優化設計以減少資源消耗。

- 功耗優化 :采取措施降低功耗。

8. 布局與布線(Place and Route, P&R)

- P&R工具選擇 :選擇合適的布局與布線工具。

- 布局 :將邏輯單元放置在PLD內部。

- 布線 :連接邏輯單元,形成電路。

9. 時序分析(Timing Analysis)

- 靜態時序分析 :檢查電路是否滿足時序要求。

- 動態時序分析 :模擬電路運行,檢查時序問題。

10. 驗證(Verification)

- 仿真 :使用仿真工具驗證設計的功能和時序。

- 測試向量生成 :生成測試向量,用于驗證設計。

- 硬件測試 :將設計下載到實際的PLD上,進行硬件測試。

11. 調試(Debugging)

- 問題定位 :分析仿真和硬件測試結果,定位問題。

- 代碼修改 :根據調試結果修改HDL代碼。

- 重復驗證 :修改后重新進行驗證和測試。

12. 文檔編寫(Documentation)

- 設計文檔 :編寫詳細的設計文檔,包括設計說明、接口定義等。

- 用戶手冊 :編寫用戶手冊,指導用戶如何使用PLD。

- 維護文檔 :編寫維護文檔,記錄設計變更和問題解決過程。

13. 版本控制(Version Control)

- 代碼管理 :使用版本控制系統管理HDL代碼。

- 文檔管理 :管理設計文檔和用戶手冊的版本。

14. 生產準備(Production Readiness)

- 設計固化 :確保設計穩定,準備生產。

- 生產測試 :制定生產測試計劃,確保產品質量。

15. 發布(Release)

- 最終驗證 :在發布前進行最終的驗證和測試。

- 發布產品 :將設計發布到生產環境。

16. 后期支持(Post-Release Support)

- 用戶反饋 :收集用戶反饋,用于改進設計。

- 問題修復 :解決用戶報告的問題。

- 更新維護 :根據需要更新設計和文檔。

以上步驟概述了PLD設計流程的各個階段,每個步驟都需要細致的工作和嚴格的質量控制,以確保最終產品的質量和性能。在實際的設計過程中,這些步驟可能會根據具體的項目需求和設計團隊的工作流程有所調整。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電源

+關注

關注

185文章

18313瀏覽量

255412 -

PLD

+關注

關注

6文章

230瀏覽量

60060 -

輸出信號

+關注

關注

0文章

302瀏覽量

12173 -

輸入信號

+關注

關注

0文章

472瀏覽量

12861

發布評論請先 登錄

相關推薦

熱點推薦

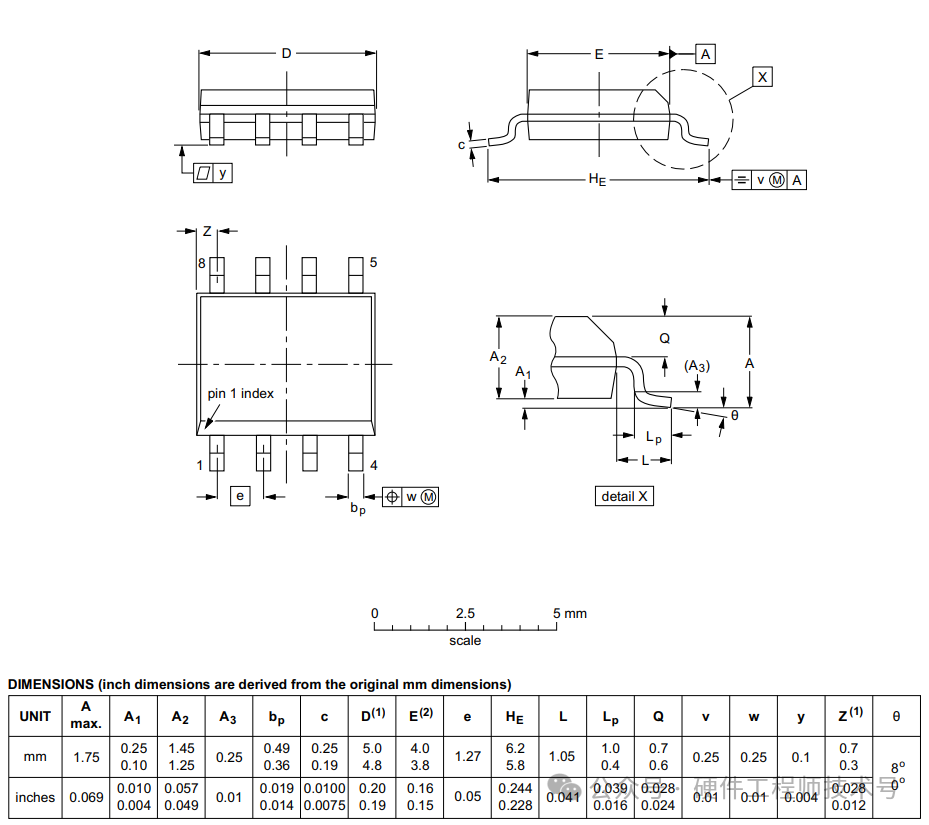

設計SO-8封裝的詳細步驟和注意事項

設計 SO-8(Small Outline-8)芯片的 PCB 封裝需要遵循一定的規范和步驟。SO-8 是一種常見的表面貼裝封裝,具有 8 個引腳,引腳間距通常為 1.27mm(50 mil)。以下是設計 SO-8 封裝的詳細步驟

什么是PLD的定義和應用 PLD與FPGA的區別和聯系

PLD的定義和應用 一、PLD的定義 PLD(Programmable Logic Device)即可編程邏輯器件,是一種能夠根據用戶的需求和設計規格,通過內部的可編程連接和邏輯門陣列,靈活地組合

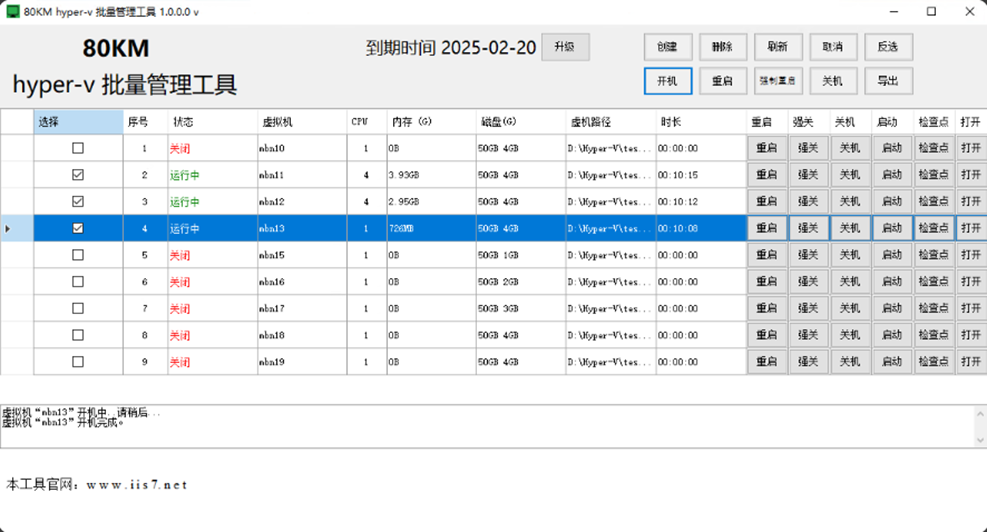

開啟hyper v,開啟hyper v的詳細操作步驟

就為大家介紹開啟hyperv的詳細操作步驟。 ? ?Hyper-V是微軟提供的虛擬化技術,允許用戶在單一物理硬件上運行多個操作系統。以下是開啟Hyper-V的詳細步驟,適用于Windo

如何快速入門PLD電路設計

1. 理解PLD的基本概念 PLD的定義 :PLD是一種可以通過編程來配置的集成電路,用于實現特定的數字邏輯功能。 PLD的類型 :包括FPGA(Field-Programmable

PLD的優勢與劣勢分析

減少廢物產生。 2. 成本效益 降低長期成本 :PLD通過減少維修和更換的需要,降低產品的總體擁有成本。 提高效率 :優化生產流程和材料使用,減少浪費,提高生產效率。 3. 法規遵從 遵守環境法規 :PLD幫助企業遵守各種環境法

如何選擇合適的PLD型號

在選擇合適的PLD(可編程邏輯器件)型號時,需要考慮多個因素,以確保所選器件能夠滿足應用需求并具有成本效益。以下是一些關鍵的步驟和考慮因素: 一、明確應用需求 功能需求 :確定PLD需要實現的具體

PLD芯片的工作原理解析

在現代電子設計領域,PLD芯片因其靈活性和可編程性而備受青睞。 1. PLD芯片概述 PLD芯片是一種集成電路,它允許設計者通過編程來定義其內部邏輯。與傳統的固定邏輯芯片不同,PLD芯

MTP協議的步驟和流程詳解

的不同節點之間傳遞信令消息。以下是MTP協議的步驟和流程的詳解: 1. MTP協議概述 MTP協議分為三個層次: MTP Level 1 :負責在物理鏈路上傳輸信令單元。 MTP Level 2 :負責在

邏輯組件中的流程塊節點通常出于什么用途

邏輯組件中的流程塊節點是流程圖、狀態圖、序列圖等圖表中的基本元素,它們用于表示業務流程、工作流程、算法步驟、系統狀態等。這些節點在軟件開發、

集成電路設計流程主要有哪些步驟

集成電路設計流程是一個復雜且精細的過程,主要包括以下幾個關鍵步驟: 一、規格定義 需求分析 :明確電路的需求、功能和性能指標,如成本、功耗、算力、接口方式、安全等級等。這是設計流程的基礎,為后續

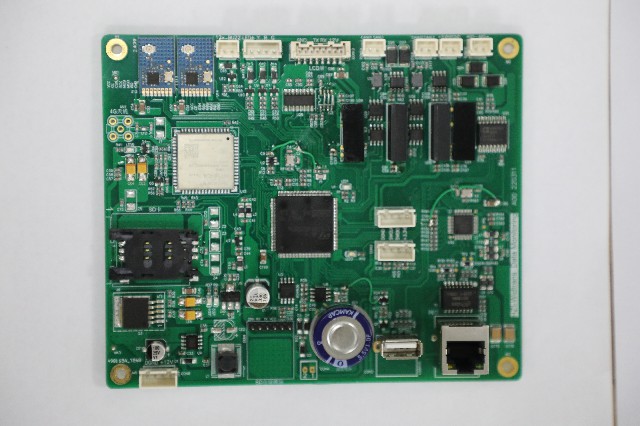

PCBA加工打樣要經過哪些流程?每一步驟都很關鍵

一站式PCBA智造廠家今天為大家講講PCBA打樣整套流程有哪些?PCBA打樣從設計到成品交付流程。在電子產品設計和開發過程中,PCBA打樣是一個至關重要的步驟。下面我們將詳細介紹PCB

簡述連接器的工藝流程

連接器的工藝流程是一個復雜而精細的過程,涉及多個環節,包括材料準備、成型、加工、電鍍、注塑、組裝、測試以及包裝等。以下是對連接器工藝流程的詳細解析,旨在全面覆蓋各個關鍵步驟。

圖像邊緣檢測系統的設計流程

圖像邊緣檢測系統的設計流程是一個涉及多個步驟的復雜過程,它旨在從圖像中提取出重要的結構信息,如邊界、輪廓等。這些邊緣信息對于圖像分析、機器視覺、圖像壓縮等領域至關重要。以下是一個詳細的圖像邊緣檢測系統設計

PLD設計流程的詳細步驟

PLD設計流程的詳細步驟

評論