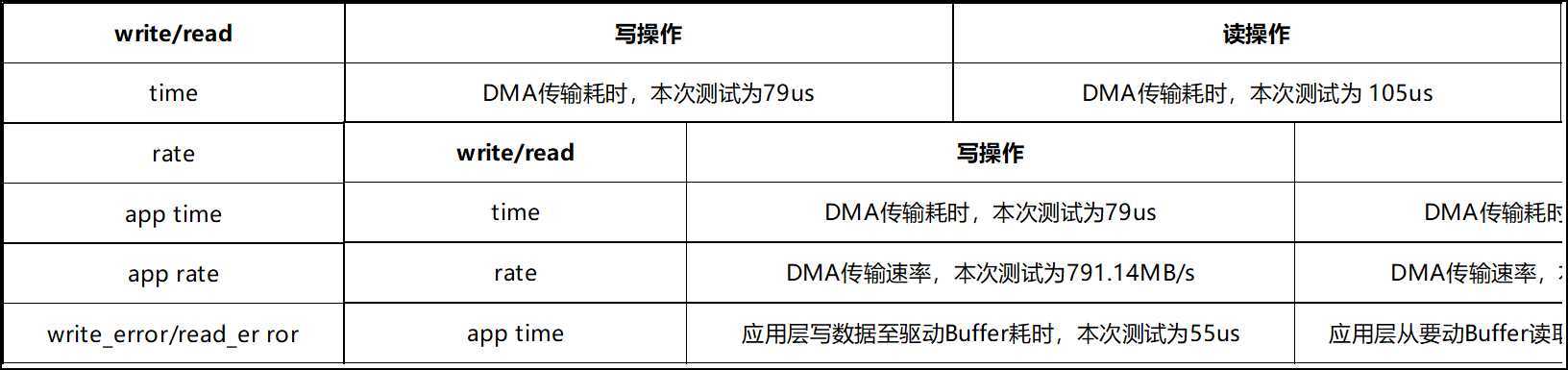

測試數據匯總

表 1

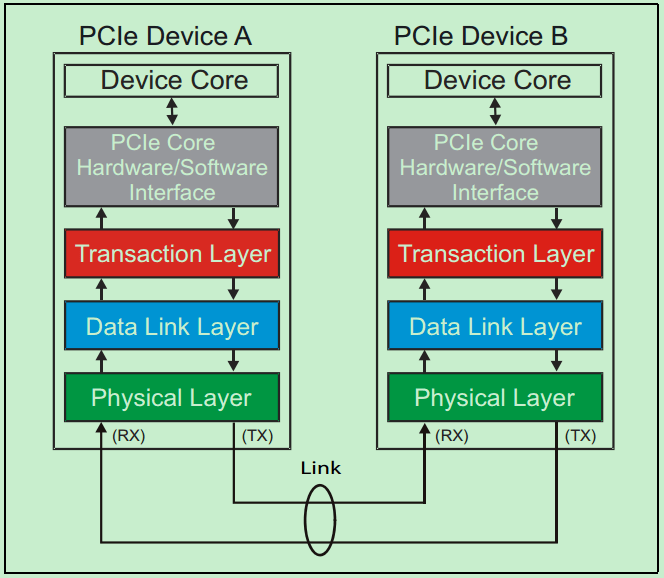

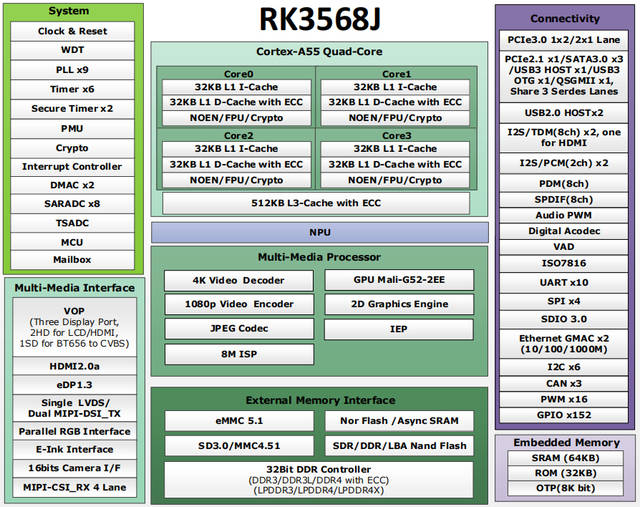

PCIe總線介紹

PCIe,即PCI-Express(peripheral component interconnect express)是一種高速串行計算機擴展總線標準。主要用于擴充計算機系統總線數據吞吐量以及提高設備通信速度。

圖 1

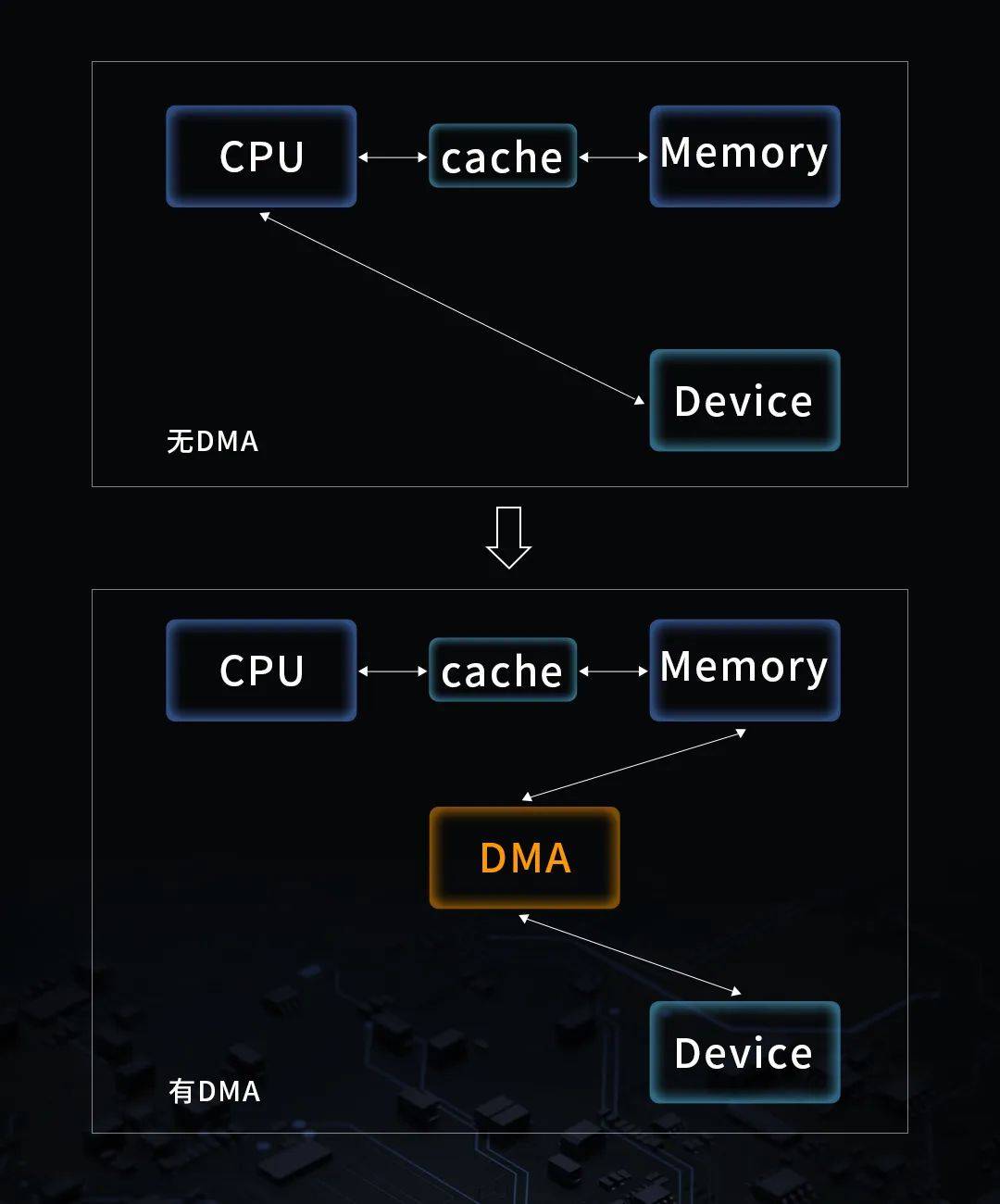

DMA技術介紹

DMA(Direct Memory Access,直接內存訪問)是一種讓硬件外設直接與存儲器進行數據交換的技術,無需CPU參與數據傳輸過程。

使用非DMA方式進行數據傳輸時,外設與內存之間的數據搬運需要依靠CPU來完成。這意味著每次數據傳輸都需要CPU的介入,導致CPU資源占用較高,并且數據傳輸速度相對較低。

使用DMA方式進行數據傳輸時,外設可以直接與內存進行數據交換。減少了CPU的介入和中斷處理,數據傳輸過程更加流暢和高效。

圖 2

RK3568J + FPGA典型應用場景

圖 3

基于RK3568J + FPGA的PCIe通信案例

本文主要介紹基于RK3568J + FPGA的PCIe通信案例,適用開發環境如下:

Windows開發環境:Windows 7 64bit、Windows 10 64bit

Linux開發環境:VMware15.5.5、Ubuntu18.04.4 64bit

U-Boot:U-Boot-2017.09

Kernel:Linux-4.19.232、Linux-RT-4.19.232

LinuxSDK:LinuxSDK-[版本號](基于rk356x_linux_release_v1.3.1_20221120)

硬件平臺:創龍科技TL3568F-EVM工業評估板

(基于瑞芯微RK3568J + 紫光同創Logos-2)

為了簡化描述,本文僅摘錄部分方案功能描述與測試結果,詳細產品資料可以通過公眾號(Tronlong創龍科技)下載。

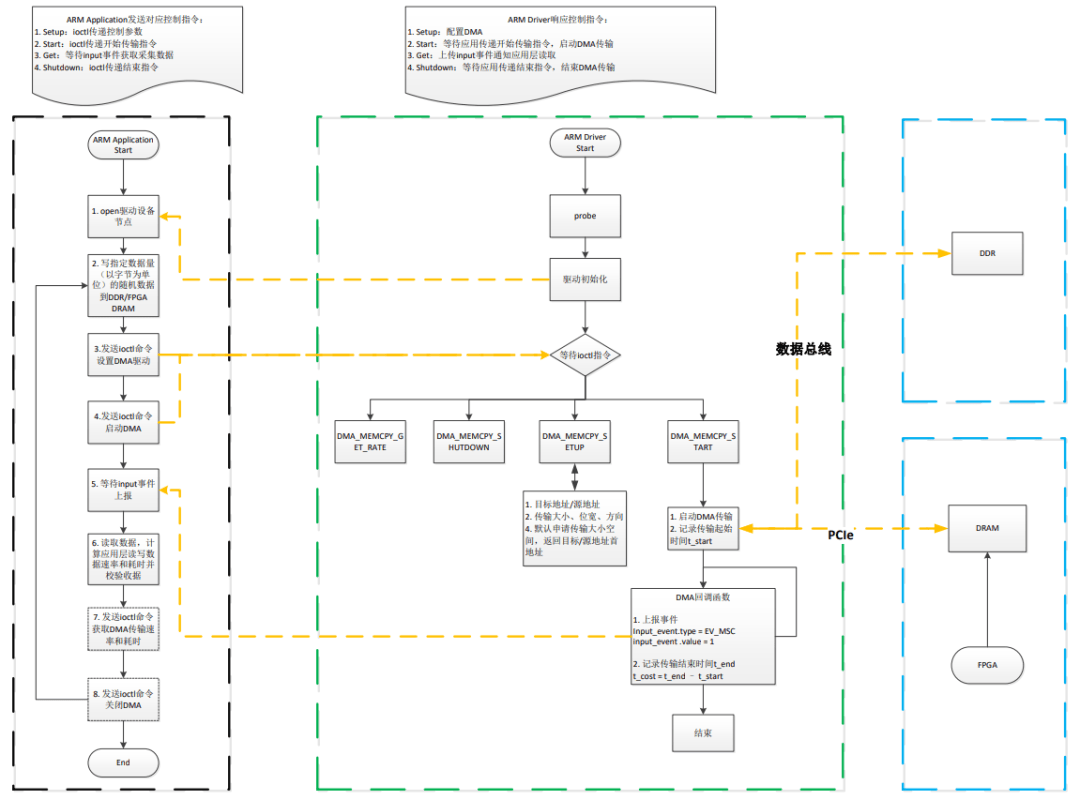

案例說明

ARM端基于PCIe總線對FPGA DRAM進行讀寫測試。應用程序通過ioctl函數發送命令開啟DMA傳輸數據后,等待驅動上報input事件;當應用層接收到input事件,說明DMA傳輸數據完成。

程序流程如下圖所示。

圖 4

(1)ARM端程序原理說明如下:

a)采用DMA方式;

b)將數據寫至dma_memcpy驅動申請的連續內存空間(位于DDR);

c)配置DMA,如源地址、目標地址、傳輸的數據大小等;

d)寫操作:通過ioctl函數啟動DMA,通過PCIe總線將數據搬運至FPGA DRAM;

e)程序接收驅動上報input事件后,將通過ioctl函數獲取DMA搬運數據耗時,并計算DMA傳輸速率(即寫速率);

f)讀操作:通過ioctl函數啟動DMA,通過PCIe總線將FPGA DRAM中的數據搬運至dma_memcpy驅動申請的連續內存空間(位于DDR);

g)程序接收驅動上報input事件后,將數據從內核空間讀取至用戶空間,然后校驗數據,同時通過ioctl函數獲取DMA搬運數據耗時,并計算DMA傳輸速率(即讀速率)。

(2) FPGA端程序原理說明如下:

a)實現PCIe Endpoint功能;

a)處理PCIe RC端發起的PCIe BAR0空間讀寫事務;

b)將PCIe BAR0讀寫數據緩存至FPGA DRAM中。

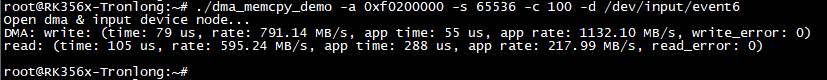

案例演示

評估板上電啟動后,進入評估板文件系統執行如下命令,將隨機數據先寫入FPGA DRAM,再從FPGA DRAM讀出。測試完成后,程序將會打印最終測試結果,包含讀寫平均傳輸耗時、讀寫平均傳輸速率、讀寫錯誤統計等信息。

Target#./dma_memcpy_demo -a 0xf0200000 -s 65536 -c 100 -d /dev/input/event6

圖 5

表 2 測試結果說明

到這里,我們的演示步驟結束。想要查看更多瑞芯微RK3568J + FPGA相關的案例演示,歡迎各位工程師通過公眾號(Tronlong創龍科技)下載,快來試試吧!

審核編輯 黃宇

-

FPGA

+關注

關注

1645文章

22034瀏覽量

617849 -

PCIe

+關注

關注

16文章

1340瀏覽量

85078

發布評論請先 登錄

RK3568J高性能多媒體處理器特性概述

瑞芯微 RK3568J 視頻圖像處理框架全解析

1分鐘學會如何提升PCIe通信速率,基于RK3568J + FPGA國產平臺!

1分鐘學會如何提升PCIe通信速率,基于RK3568J + FPGA國產平臺!

評論